I

Изобретение относится к области аналоговой вычислительной техники и может быть использовано в устройствах автоматики, измерительной и вычислительной техники.

Известно аналоговое запоминающее устройство замкнутого типа, содержащее накопитель на магнитных аналоговых эле.ментах памяти, каждый из которых содержит четыре магнитопровода с обмотками, образующими цепь записи входного сигнала, цепь выходного сигнала, цепь записи и цепь считывания, распределитель, сдвигающий регистр, синхронизирующий генератор, формирователи импульсов записи и считывания, выходное устройство, сумматор, причем входы формирователей соединены с соответствующими выходами сдвигающего регистра и распределителя, управляющие входы которых соединены с выходом синхронизирующего генератора, выходы формирователей соединены с соответствующими цепями записи и считывания накопителя, выходная цепь которого присоединена к выходному устройству, выход последнего является выходом всего устройства и соединен с вычитающим входом сумматора, другой вход которого является входом всего устройства, а

выход сум.матора соединен со второй цепью записи накопителя 1.

Недостатком такого устройства является низкая скорость записи информации.

Наиболее близким техническим решением к предлагаемому изобретению является аналоговое запоминающее устройство разомкнутого типа, выполненное на накопителе из элементов памяти, построенных на трансфлюксорах с обмотками, образующими цепь записи, цепь считывания, цепь входного сигнала, цепь выходного сигнала, устройство управления, входное и выходное устройства, блок выбора адресов, включающий в себя распределитель, формирователи импульсов, ключи записи и считывания, логические схемы, причем выходы устройства управления соединены с соответствующими входами блока выбора адресов, выходы которого присоединены к цепям записи и считывания накопителя, цепь входного сигнала которого присоединена к выходу входного 20 устройства, а цепь выходного сигнала - к входу выходного устройства, выход которого является выходом всего устройства (2).

Такое устройство имеет невысокую точность регистрации информации, а для повышения точности требует предварительной отбраковки аналоговых элементов памяти по погрешности записи.

Цель изобретения - повысить точность устройства.

Это достигается тем, что в аналоговое запоминающее устройство, содержащее накопитель, входы которого подключены к выходам блока выбора адресов и к выходу блока записи, блок управления, выходы которого подключены к входам блока выбора адресов, блок считывания, вход которого подключен к выходу накопителя, введены первый ключ, один из входов которого является входом устройства, другой вход подключен к выходу блока управления, источники эталонного напряжения, подключенные через первый ключ к входу блока записи, второй ключ, один из входов которого подгс 1ючен к выходу блока считывания, другойк выходу блока управления, элементы памяти, одни.из входов которых подключены к соответствующим выходам второго ключа, другие - к выходу блока управления, сумматоры, входы которых подключены к выходам соответствующих элементов памяти, блок умножения, один из входов которого подключен к эталонному источнику напря жения, другой - к выходу первого сумматора, блок, деления, один из входов которого подключен к выходу блока умножения, другой - к выходу второго сумматора, причем выход блока деления является выходом устройства.

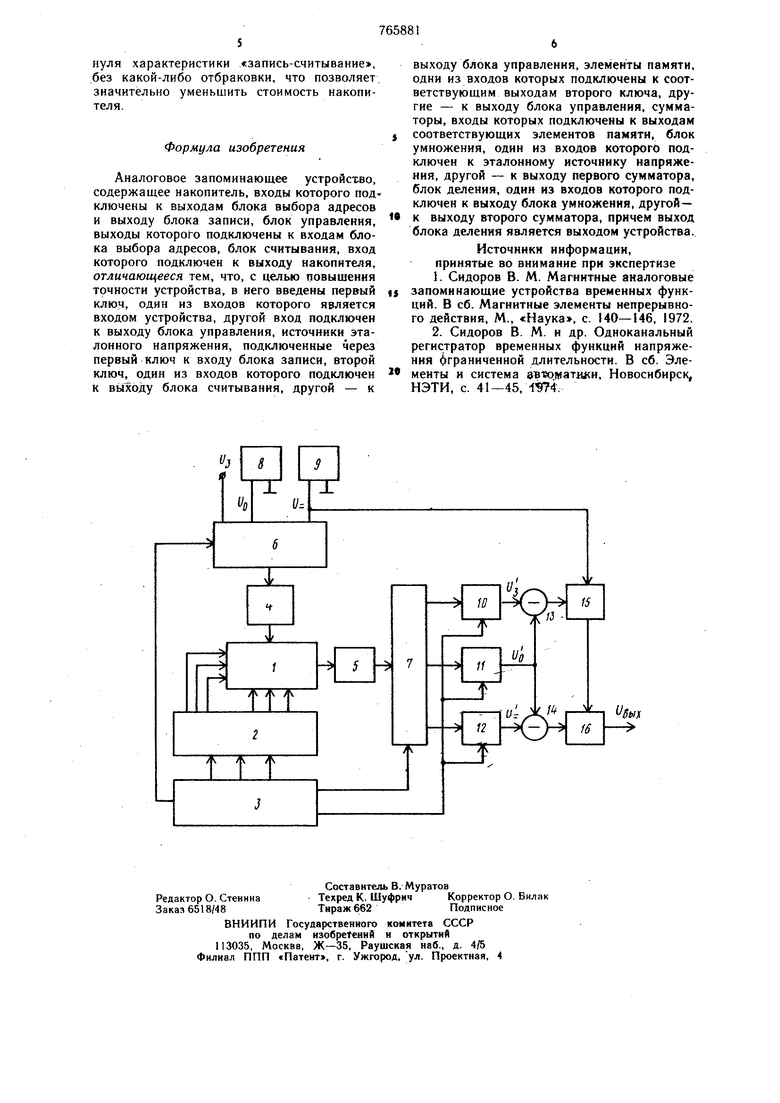

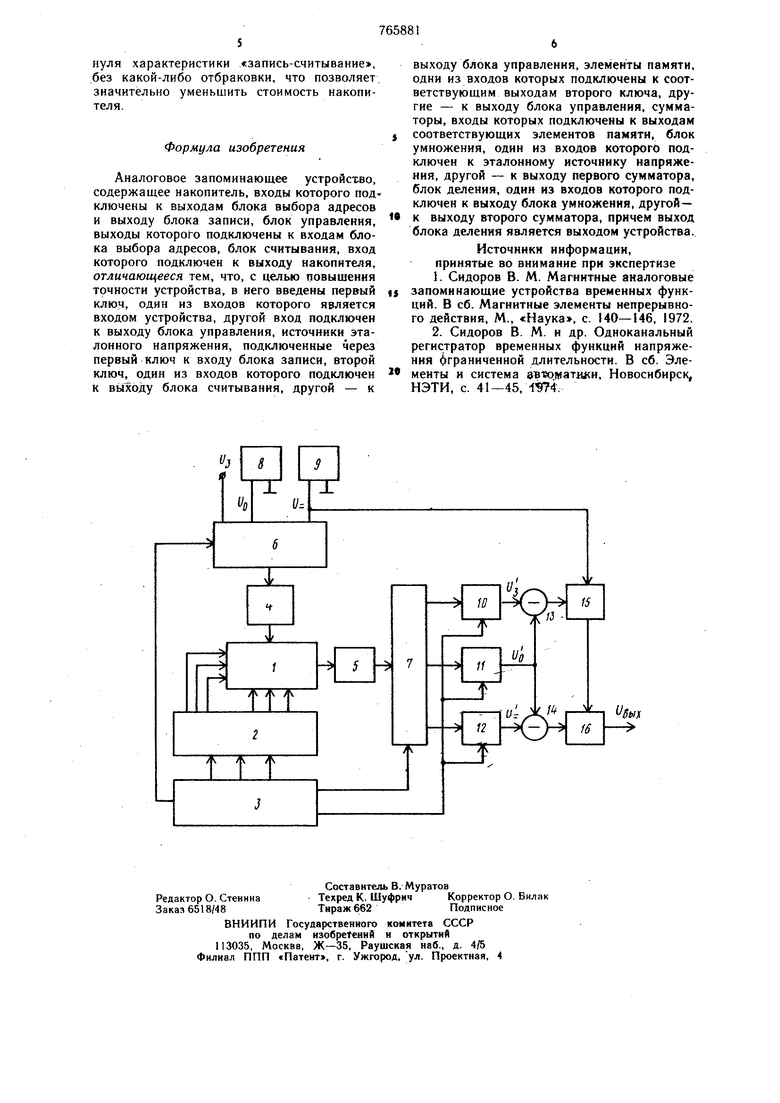

На чертеже представлена структурная схема аналогового запоминающего устройства.

Аналоговое запоминающее устройство содержит накопитель I, блок 2 выбора адресов, блок управления 3, блок записи 4, блок считывания 5, ключи 6 и 7, источники 8 и 9 эталонного напряжения, элементы памяти 10, И и 12, сумматоры 13 и 14, блок умножения 5, блок деления 16.

Устройство работает следующим образом,

В режиме записи блок управления 3 выдает сигнал на управляющий вход ключа б, который подключает входную клемму аналогового запоминающего устройства к блоку записи 4. Кроме того, блок управления 3 вырабатывает сигналы на входы блока 2 выбора адресов, который обеспечивает последовательность выбора элементов памяти накопителя и осуществляет запись значений входного сигнала, соответствующих моментам квантования.

В режиме считывания блок 2 выбора адресов по сигналам с блока управления 3 обеспечивает считывание записанной информации с первого элемента памяти накопителя 1. Сигнал с этого элемента памяти поступает на вход блока.считывания 5, с Выхода которого напряжение LJ з через ключ 7 по сигналу с блока управления 3 запоминается элементом памяти 10. Далее по сигналам с блока управления 3 ключ 6 обеспечивает подключение источника 8 эталонного напряжения к блоку записи 4. Напряжение и о этого источника выбирается таким, чтобы в элемент памяти записывался «О, чаще всего U о 0. По сигналам с блока управления 3 блок 2 выбора адресов обеспечивает запись этого напряжения в первый элемент памяти и последующее считывание. Напряжение с выхода блока считывания 5 и о, показывающее смещение характеристики «запись-считывание первого элемента памяти накопителя 1 относительно начала координат, через ключ 7, запоминается элементом памяти П. На следующем этапе работы устройства ключ 6 по сигналу с

блока управления 3 подключает источник 9 эталонного напряжения к блоку записи 4. Напряжение этого источника U соответствует максимально допустимому значению сигнала записи линейного участка характеристики «запись-считывание. Блок 2 выбора адресов по сигналам с блока управления 3 обеспечивает запись этого напряжения в первый элемент памяти накопителя I и его считывание. Напряжение 1/- с выхода блока считывания через ключ 7, управляемый

блоком управления 3, запоминается элементом памяти 12. По сигналу с блока управления 3 напряжения, записанные в элементах памяти 10, 11 и 12, поступают на входы сумматоров 13 и 14. Напряжение (Ua-Uo),

Q получаемое на выходе сумматора 13, поступает на вход блока умножения 15, на другой вход которого поступает напряжение и с источника 9 эталонного напряжения. Таким образом, на выходе блока умножения 15 имеется напряжение (из-Uo),

5 которое поступает на вход блокаделения 16, на другой вход которого поступает напряжение () с выхода, сумматора 14. Таким образом, на выходе всего устройства будет напряжение

. ): - (/о

Далее цикл работы повторяется для второго и последующих элементов памяти до окончания процесса считывания со всех элементов памятинакопителя 1.

S Применение при считывании записи нулевого значения сигнала Uo, фиксированного значения U- и последующих вычислительных операций позволяет учесть смещение нуля характеристики «запись-считывание и ее наклон для каждого элемента памяти накопителя I, что позволяет существенно повысить точность регистрации информации аналогрвого запоминающего устройства. При этом сохраняется высокое быстродействие при записи, так как устройство ется разомкнутым по структуре.

Кроме того, становится возможным использование в накопителе 1 элементов памяти, имеющих большие значения смещения

5

нуля характеристики .«запись-считывание, без какой-либо отбраковки, что позволяет, значительно уменьшить стоимость накопителя.

Формула изобретения

Аналоговое запоминающее устройство, содержащее накопитель, входы которого подключены к выходам блока выбора адресов и выходу блока записи, блок управления, выходы которого подключены к входам блока выбора адресов, блок считывания, вход которого подключен к выходу накопителя, отличающееся тем, что, с целью повышения точности устройства, в него введены первый ключ, один из входов которого является входом устройства, другой вход подключен к выходу блока управления, источники эталонного напряжения, подключенные через первый ключ к входу блока записи, второй ключ, один из входов которого подключен к выходу блока считывания, другой - к

выходу блока управления, элементы памяти, одни из входов которых подключены к соответствующим выходам второго ключа, другие - к выходу блока управления, сумматоры, входы которых подключены к выходам соответствующих элементов памяти, блок умножения, один из входов которого подключен к эталонному источнику напряжения, другой - к выходу первого сумматора, блок деления, один из входов которого подключен к выходу блока умножения, другой - к выходу второго сумматора, причем выход блока деления является выходом устройства.

Источники ннформацнн, принятые во вннманне при экспертизе

1.Сидоров В. М. Магнитные аналоговые запоминающие устройства временных функций. В сб. Магнитные элементы непрерывного действия, М., «Наука, с. 140-146, 1972.

2.Сидоров В. М. и др. Одноканальный регистратор временных функций напряжения Ограниченной длительности. В сб. Элемеиты и система звтюматили, Новосибирск, НЭТИ, с. 41-45, -f.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU849307A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1298869A2 |

| Электронная фотонаборная машина | 1977 |

|

SU1276252A3 |

| Аналоговое запоминающее устройство | 1981 |

|

SU960957A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

Авторы

Даты

1980-09-23—Публикация

1978-12-21—Подача