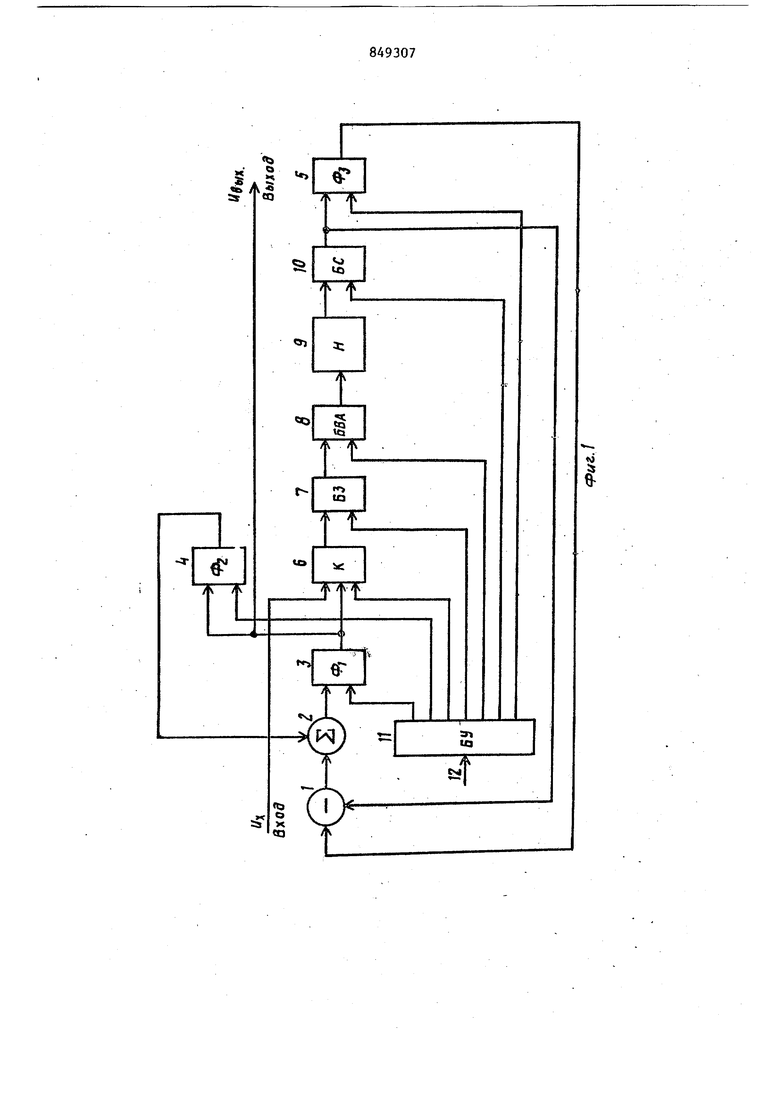

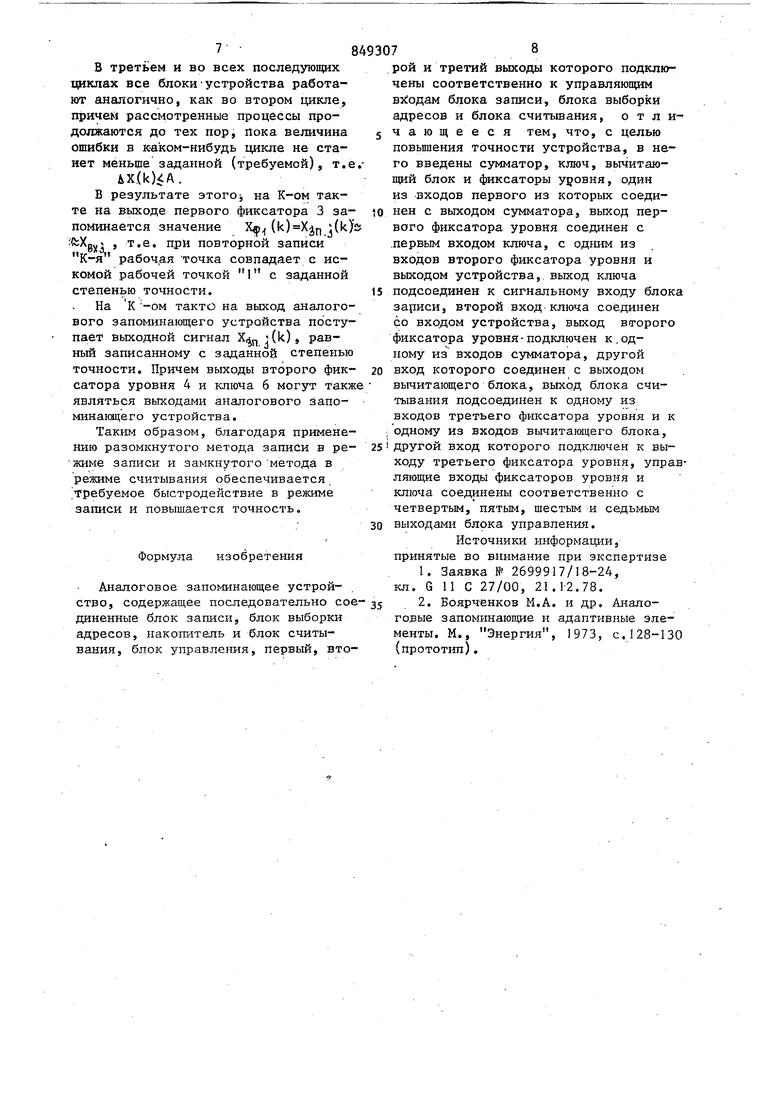

Изобретение относится к вычислите ной технике и может быть использован в устройствах автоматики и измерител ной техники. Известно аналоговое запоминающее устройство разомкнутого типа, содержащее накопитель, вводы которого под соединены к вьпсодам блока выбора адр сов и выходу блока записи, блок управления, выходы которого подключены к входам блока выбора адресов, блок считывания, вход которого подключен к выходу накопителя, первый ключ, один из входов которого является входом устройства, а другой вход под ютючен к выходу блока управления; источники эталонного напряжения, подключенные через первый ключ к входу блока записи, второй ключ, один из входов которого подключен к выходу блока считьтания, а другой - к выходу блока управления, элементы памяти, одни из входов которых подключены к соответствующим выходам второго ключа, а другие - к выходу блока управления, сумматоры, входы которьк подключены к выходам соответстпующих элементов памяти, блок умножения, один из входов которого подключен к эталону источника напряжения, а другой - к ВЫХОДУпервого сумматора, блок деления, один из входов которого подключен к выходу блока уьпюжения, а другой - к выходу второго сумматора, причем выход блока деления является выходом устройства flj« Недостатком этого устройства является низкая точность регистрации информации из-за погрешности от нелинейности характеристик запись-считы-ванне аналоговых элементов памяти, Наиболее близким по технической сущности к предлагаемому является аналоговое запЪминающее устройство разомкнутого типа, содержащее последовательно соединенные бдок записи, блок выбора адресов, накопители, построенный на запо..шнающих элементах с разрушающим считыванием информации, блок считывания и. блок управления 2 Недостатком этого устройства является низкая точность регистрации информации. Цель изобретения - повьшение точности устройства, Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее последовательно соединенные блок записи, блок выборки адресов, накопитель и блок считывания, блок управления, первый,второй и третий выходы которого подключень соответственно к управляющим входам блока записи, лока выборки адресов и блока считывания, введены сумматор, ключ, вычитающий блок и фиксаторы уровня, один из входов первого из которых соединен с выходом сумматора, выход первого фиксатора уровня соединен с первым входом ключа,С одним из входов второго фиксатора уровня и выходом устройства,. выход ключа подсоединен к сигналь ному входу блока записи, второй вход ключа соединен со входом устройства, выход второго фиксатора уровня подклю чен к одному из входов сумматора, другой вход которого соединен с выходом вычитающего блока,выход блока считывания подсоединен к одному из входов третьего фиксатора уровня и к одному из входов вычитающего блока другой вход которого подключен к выходу третьего фиксатора уровня, управляющие входы фиксаторов уровня и ключа соединены соответственно с чет вертым, пятымJ шестым и седьмым выхо дами блока управления. На фиг. 1 изображена функциональн схема предлагаемого устройства; на фиг. 2 - характеристика записи-считы вания аналогового элемента памяти. Устройство (фиг. 1) содержит вычитающий блок , сумматор 2, фиксато ры уровня 3-5, ключ 6, блок 7 записи блок 8 выборки адресов, накопитель 9 блок 10 считьшания, блок 11 управлен и шину 12 управления. Устройство работает следующим образом. Рассмотрим его работу в режиме , подготовки записи информации/ режиме записи и режиме считывания. В режиме подготовки записи информ ции (фиг. 2) блок 1 управления выдает сигналы на управляющие входы блока 8 выборки адресов и блока 10 считьшалия, которые обеспечивают разрушающее считывание информации со всех элементов памяти накопителя 9, которые при этом устанавливаются в нулевое состояние (рабочая точка каждого элемента перемещается из произвольного положения в положение О/. В режиме записи в устройстве применяется разомкнутый метод записи, при котором используется непосредственная однозначная зависимость между записываемой информацией Хп и остаточным состоянием носителя информации П. Р, называемой характеристикой записи Пдр Kj (xj j), которая для Каждого элемента памяти накопителя 9 имеет свой определенный вид. В этом режиме блок 11 управления выдает сигнал на управляющий вход ключа 6, который подключает вход устройства к блоку 7 записи. Кроме того, блок 11 управления вырабатьшает, сигналы на управляющие входы блока 7 записи и блока 8 выборки адресов, которые обеспечивают последовательность выбора элементов памяти накопителя 9 и осуществляют запись значений входного сигнала, соответствуюЩ11Х моментов квантования. Например, рабочая точка j-ro элемента памяти накопителя 9 перемещается в положение 1 согласно зависимости Пр( j(X. j). Следовательно, разомкнутый метод обеспечивает требуемое быстродействие записи информации. В режиме считывания сначала производится разрушающее считьшание хранимой информации из выбранного j-ro элемента памяти накопителя 9 с последующим запо; инанием выходного сигнала , однозначно определяемого состоянием j-ro элемента памяти. Затем, используя однозначность характеристики записи-.считывания элемента памяти X.,,j j. . /,, -DDlX.J rj v/wp. ) , производится повторная запись в тот же j-й элемент памяти накопителя 9 этого же сигнала по схеме с импульсной отрицательной обратной связью с требуемой точностью за несколько циклов, при этом, в конце времени записи на входе блока 7 записи устанавливается истинное значение записанной ранее информации в j-й элемент памяти накопителя 9. Следовательно, в отличие от известного устройства, в котором в режиме гчитывання используется обобщенная усредненная характеристика считы-вания накопителя 9 X. (lIocT j), предлагаемое устройство учитывает индивидуальные особенности характеристик записи-считьшания каждого эл мента памяти накопители 9, а это приводит к повышению точности. Весь интервал времени считьшания информации с каждого элемента памяти накопителя 9 состоит из нескол ких временных циклов, калсдьш из кот рых состоит из двух тактов: разруша щего считьшанияИ записи. При этом работа аналогового запоминающего ус ройства иллюстрируется системой нелинейных разностных уравнений для каждого элемента памяти накопителя . 6b«j()fjCX3n,j(i-i)L где второе уравнение системы опреде ляет характеристику записи-считывания j-ro запоминающего элемента накопителя 9 (,2, 3...). В режиме считывания по сигналам с блока 11 управления вход устройства отключается от блока 7 записи и на вход блока 7 записи через шхюч 6 подключается выход первого фиксатора уровня 3. В первом цикле, .в такте считьшания, по сигналам с блока 11 управления последовательно во време осуще ствляются следующие операции. Второй фиксатор уровня 4устанавливается в нуль, т.е. Хф (0-)0, с помощью блоков.выборки адресов 8 и считьшания10 осуществляется разрушающее считывание информации с j-ro элемента памяти накопителя 9, кото-. рый при этом устанавливается в нулевое состояние, рабочая точка перемещается из положения 1 в положение О. Блок 10 считывания формирует выходной сигнал, однозначно определяемый характеристикой записисчнтьшания j-ro элемента памяти накопителя 9 и величиной входного сигнала записи в режиме записи g( соответствует рабочей точке 1. , Третий фиксатор уровня 5 отслеживает и запоминает выходной сигнал с блока 10 считьшания, .т.е. (1 После этого выходной сигнал с блока 10 считывания устанавливается в нуль Благодаря этому вычитающий блок выделяет сигнал ошибки uX(1),76 БС ( BbW i который складывается в сумматоре 2 с выходным сигналом второго фиксатора уровня 4, Хг(1)ДХ()Хф2(0)Хвыу(1). Первый фиксатор уровня 3,отслеживает и запоминает выходной сигнал с сумматора 2, т.е. Хл,. (1 )Х5 (1 ) -Y СИ . fi . -Bbiy.rf- Таким образом, на вход блока 7 записи поступает сигнал х,„,;(1) X В такте записи по сигналам с блока 4 управления осуществляется запись в- J-й элемент памяти накопителя 9 под действием сигнала рабочая точка которого перемещается в положение 2. В этом такте второй фиксатор уровня 4 отслежива.т и запоминает сигнал с первого фиксатора уровня 3 до следующего цикла, т.е. (1) X3nj (О . Во втором цикле, в такте считьшания, по сигналам с блока 11 управления последовательно во времени осу- . ществляется разрушающее считьшание с J-ro элемента памяти накопителя 9, который при этом устанавливается в нулевое состояние, т.е. рабочая точка перемещается из положения 2 в положение О. Блок 10 считывания формирует выходнЬй сигнал Х.,,.у ;(2) fjCX3n(l),, Вычитающий блок I выделяет сигнал ошибки uX(2)Xg,jjj(l) (2), который складывается в сумматоре 2 с выходным сигналом второго фиксатора уровня 4, т.е. Х(а)йХ(2)-.(1)-Х,.(1)-Х,,,(2)..Первый фиксатор уровня 3 отслежи вает и запоминает выходной сигнал с сумматора 2, т.е. Хф (2)Xg(2), Таким образом, на вход блока 7 записи поступает сигнал , %п.з(2) ., X4,{2) В такте записи по сигналам с блока 11 управления осуществляется загтась j-й элемент памяти накош теля 9 под ействием сигнала Хп ч (2), рабоая точка которого перемещается в положение 3. А на втором фиксаторе ровня 4 запо нается сигнал с перого фиксатора уровня 3 до следуюего цикла, т.е. Xjfl.(2). Хф5(2) В третьем и во всех последующих циклах все блокиустройства работают аналогично, как во втором цикле, гфичей рассмотренные процессы продолжаются до тех пор, Пока величина ошибки в каком-нибудь цикле не станет меньще заданной (требуемой), т.е iX(k)4A. В результате этого на К-ом такте на выходе первого фиксатора 3 запоминается значение ЗЦ) () ( fcXgv , т.е. при повторной записи К-я рабоч.ая точка совпадает с искомой рабочей точкой с заданной степенью точности. На к -ом такто на выход аналогового запоминающего устройства поступает выходной сигнал Х. -(k), равный записанному с заданной степенью точности. Причем выходы второго фиксатора уровня 4 и ключа 6 могут такж являться выходами аналогового запоминанщего устройства. Таким образом, благодаря применению разомкнутого метода записи в режиме записи и замкнутого метода в режиме считывания обеспечивается, Требуемое быстродействие в режиме записи и повышается точность. Формула изобретения Аналоговое запоминающее устройство, содержащее последовательно сое диненные блок записи, блок выборки адресов, накопитель и блок считывания, блок управления, первый, вто878 рой и третий выходы которого подключены соответственно к управляющим вводам блока записи, блока выборки адресов и блока считьшания, о т л ичающееся тем, что, с целью повышения точности устройства, в него введены сумматор, ключ, вычитающий блок и фиксаторы уровня, один из входов первого из которых соединен с выходом сумматора, выход первого фиксатора уровня соединен с .первым входом ключа, с одгшм из входов второго фиксатора уровня и выходом устройства,, выход ключа подсоединен к сигнальному входу блока зариси, второй вход ключа соединен со входом устройства, выход второго фиксатора уровня-подключен к,одному из входов сумматора, другой вход которого соединен с выходом вычитающего блока, выход блока считывания подсоединен к одному из входов третьего фиксатора уровня и к одному из входов вычитающего блока, другой вход которого подключен к выходу третьего фиксатора уровня, управляющие входы фиксаторов уровня и ключа соединены соответственно с четвертым, пятым, шестым и седьмым выходами блока управления. Источники информации, принятые во внимание при зкспертизе 1.Заявка № 2699917/18-24, кл. G 11 С 27/00, 21,12.78, 2.Боярченков М.А. и др. .Аналоговые запоминающие и адаптивные элементы. М., Энергия, 1973, с,128-130 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799014A1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Аналоговое запоминающее устройство | 1984 |

|

SU1244724A1 |

| Цифровой компандер | 1986 |

|

SU1427575A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

Авторы

Даты

1981-07-23—Публикация

1979-11-01—Подача