54 АНАЛОГОВОЕ АПОМИНАКШЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Аналоговое запоминающее устройство | 1977 |

|

SU723686A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU720514A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Логическое запоминающее устройство | 1981 |

|

SU1014036A1 |

Изобретение относится к аналоговой вычислительной технике и может быть использовано в устройствах авто матики, измерительной и вычислительной техники. Известен аналоговый элемент памя,ти замкнутой структуры, содержащий запоминающий элемент с неразрушамщим считыванием информации, схему сравнения, усилитель ошибки, устройство считывания информации и нелинейной функциональный преобразователь, причем выход устройства считывания подключен к первому вычитакжаему входу схемы сравнения, суммируюпдай вход ко торой подключен к выходу источника записываемой аналоговой величины, а выход подключен ко входу усилителя ошибки, выход которого подключен ко входу устройства считывания, а вход нелинейного функционального преобразователя подключен к выходу усилите ля ошибки, а выход - ко второму вычи тающему входу схемы сравнения l|. Однако устройство паулти имеет ограниченные функциональные возможности . Наиболее близким к предлагаемому является аналоговое запомииающее ус ройство. содержащее накопитель, вхо ды которого подключены к выходам блока выборки адресов, блок поочередной выдачи кодов адресов, первые входы которого соединены с информационными шинами устройства, второй вход блока поочередной выдачи кодов адресов подключен к шине управления и к одному из входов генератора тактовых импульсов , первый выход которого соединен с третьим входом блока поочередной выдачи кодов адресов и одним из входов блока выборки адресов, другие входы которого соединены с выходами блока поочередной выдачи кодов адресов , четыре элемента стробирования, причем один из входов первого элемента стробирования соединен со вторым выходом генератора тактовых импульсов, сукмирукяций усилитель, выход которого соединен с выходом устройства, нуль-орган, шесть ключей, четыре разрядных ключа, четыре интегрирующих усилителя, три переключателя режимов, при этом один из входов второго и третьего элементов стробирования соединены с выходом накопителя и через первый переключатель режимов с одними из входов первого и четвертого элементов стробирования, другие входь элементов стробирования соединены с

третьими выходами генератора тактовых импульсов, выходы элементов стробирования соединены с одними из входов иитегрируюктх усилителей, другие входы которых подключены к четвертым выходам генератора тактовых импульсов, выход первЬго интегрирующего усилителя через второй переключатель соединен со вхсдами суммируклцего усилителя и выходом второго интегрируюшего усилителя, выход трзтьего интегрирующего усилителя соединен через нульорган со вторым входом генератора тактовых импульсов, выход четвертого интегрирующего усилителя через третий переключатель соединен с одним из входов первого ключа, выход которого соединен с третьим входом третьего интегрирующего усилителя и выходом второго ключа, вход второго ключа соединен со входом третьего и четвертого ключей и шиной напряжения первого операнда, входы пятого и шестого ключей соединены с шиной напряжения второго операнда, выходы третьего и шестого ключей, соответственно подсоединены к выходам первого и четвертого элементов стробирования, выходца четвертого и пятого ключей соединены со входами первого и четвертого элементов стробирования, управляющие входы ключей соединены с пятыми выходами генератора тактовых импульсов 2 .

Недостаток устройства -.низкое (йлстродействие при выполнении множительно-делйтельных операций.

Цель изобретеиия - повышение быстродействия устройства при выполнении м«ожительно-делительных операций.

Поставленная цель достигается тем, что в устройство, содержащее накопитель, входы которого подключеги к выходам блока выборки адресов, блок записи, блок поочередной выдачи кодов адресов, первые входы которогчэ соединены с информационными шинами устройства, второй вход блока поочередной всшачи кодов autpecoB подключен к шине управления и к одному из входов генератора тактовых импульсов, первый выход которого соединен с третьим входом блока поочередной выдачи кодов адресов и одним из входов блока выборки адресов, другие входы которого соединены с выходами блока поочередной выдачи кодов адресов, четыре элемента стробирования, причем один из входов первого элемента стробирования соединен со вторым выходом генератора тактовых импульсов, суммирукхций усилитель, выход которого соединен с выходом устройства, нульорган, шесть ключей,- четыре разрядных ключа, четыре интегрирующих усилителя, три переключателя режимов, при этом один из входов второго и третьего элементов стробирования соединены с выходом накопителя и через

первый переключатель режимов с одними из входов первого и четвертого элементов стробирования, другие входы элементов стробирования соединены с третьими выходами генератора тактовых импульсов, выходы элементов стробирования соединены с одними из входов интегрирунвдих усилит ей, другие входы которых подключены к четвертым выходам генератора тактовых импульсов/ выход первого интегрирующего усилителя через второй переключатель режимов соединен со входами суммирующего усилителя и выходом второго интегрирующего усилителя, выход третьего интегрирующего усилителя сое5динен через нуль-орган со вторым входом генератора тактовых импульсов, выход четвертого интегрирующего усилителя через третий переключатель режимов соединен с одним из вхо0дов первого ключа, выход которого соединен с третьим входом третьего интегрирующегчэ усилителя и выходом второго ключа, вход второго ключа соединен со входом третьего и четвертого ключей и шиной напряжения пер5вого операнда, входы пятого и шестого ключей соединены с шиной напряжения второго операнда, выходы третьего и шестого ключей, соответственно, подсоединены к выходам первого и чет0вертого элементов стробирования, выходы четвертого и пятого ключей соединены со входами первого и четвертого элементов стробирования, управляющие входы ключей соединены с пятыми выходами генератора тактовых импульсов, введены фиксатор уровня и седьмой ключ, причем первый вход фиксатора уровня соединен с выходом устройства, выход фиксатора уровня

0 соединен с первым входом блока записи, второй вход которого соединен с выходом устройства, при этом первый вход которого соединен с выходом устройства, при этом первый вход седьмого ключа является аналоговым вхо5дом устройства, а выход его подключен к первому входу блока записи и входу четвертого интегрирующего усилителя, управляющие же входы фиксатора уровня, блока записи и седьмо0го ключа соединеш с шестыми выхода.ми генератора тактовых импульсов, соответственно.

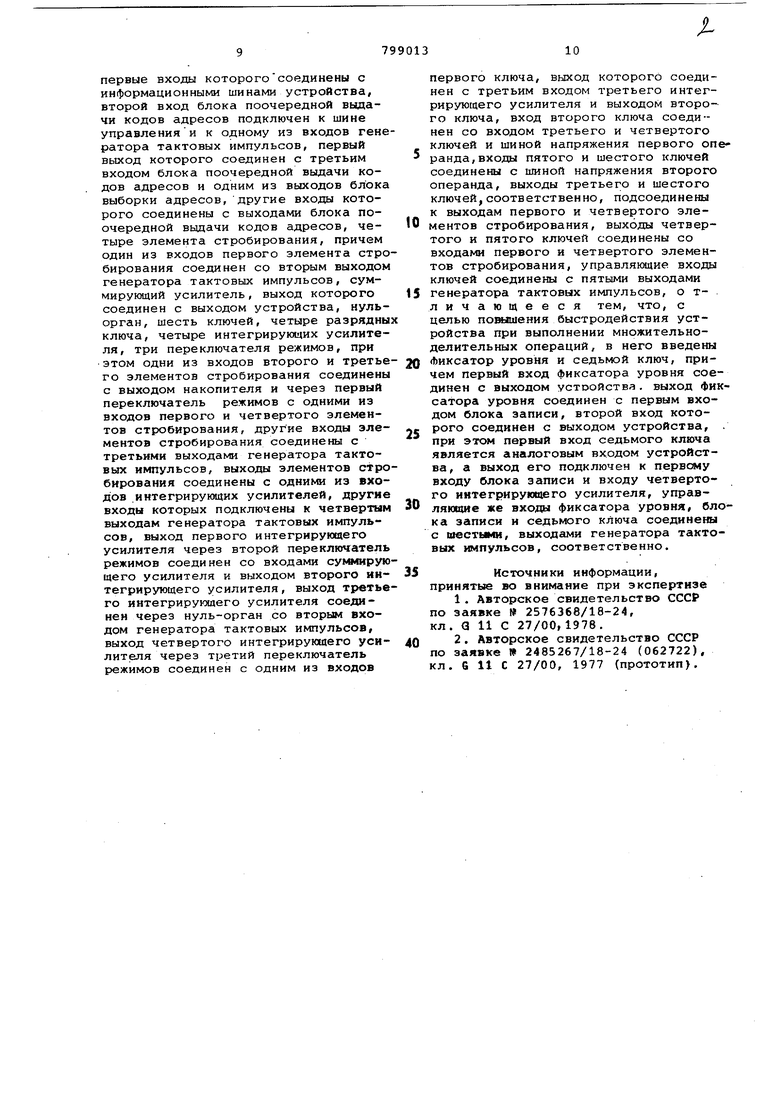

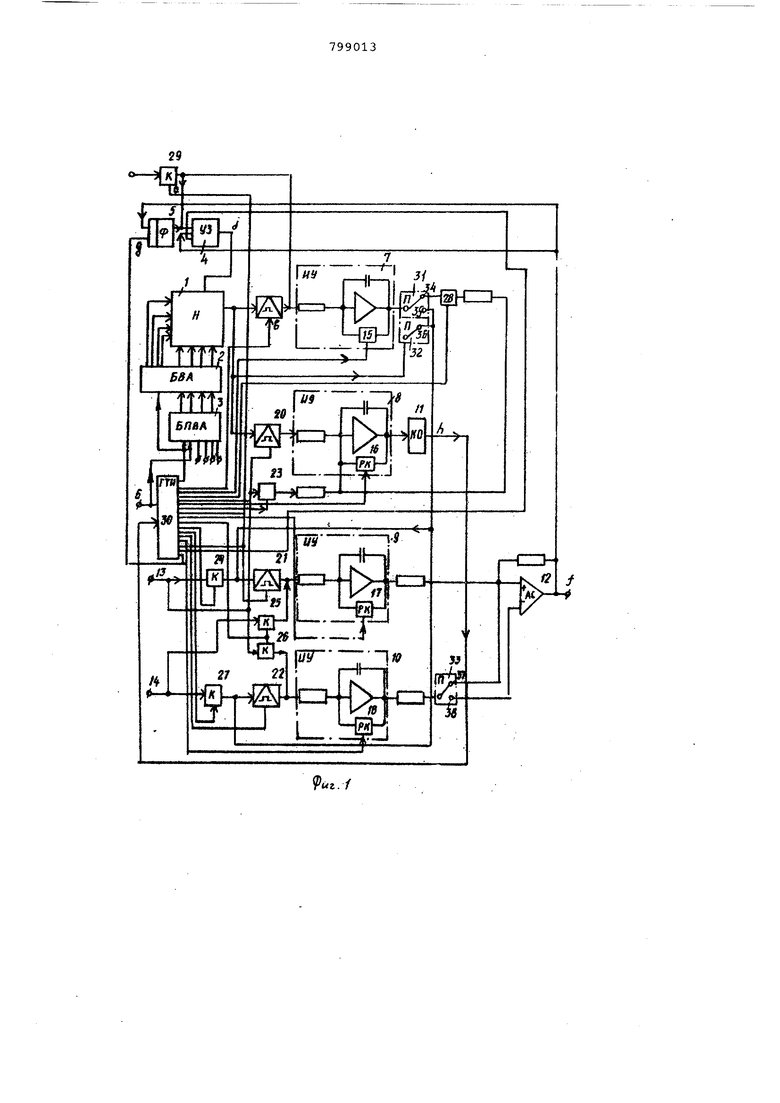

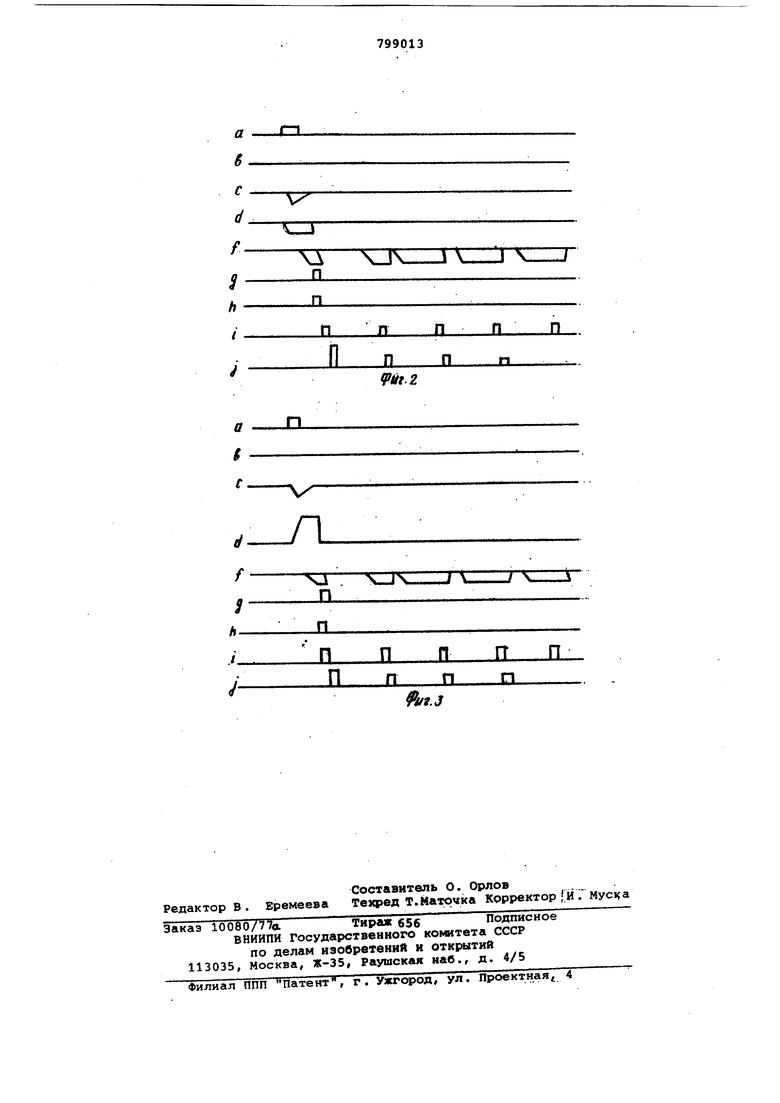

На фиг. 1 - изображена схема устройства; на фиг. 2 и 3 - (Временные

5 диаграмма, поясняющие работу устройства в режимах умножения одного записываемого числа на другое с последующей записью произведения и деления одного записываемого числа на

0 другое с записью частного, соответственно .

Устройство содержит накопитель 1 (Н), блок 2 (БВА) зыборки адресов, блок 3 (БПВА) поочередной выдачи кодов адресов, блок 4 (УЗ) записи, фик5сатор 5 (Ф) ,уровня, шину .6 управления, интегрирующие усилители 7, 8, 9и 10 (ИУ), нуль-орган 11 (НО), сум мирующий усилитель 12 (АС), шины 13, 14 напряжений первого и второго операндоэ, раз рядные ключи 15-18 (РК) входящие в интегрирующие усилители, элементы 19-22 (сс) стробирования, ключи 23-29 (к), генератор 30 (ГТЙ) тактовых импульсов, пepeключateлй 31 32 и 33 (П) режимов,контакты 34-38 переключателей 31, 32 и 33. Устройство работает следующим образом. Режим записи одного числа задается положением переключателей 31, 32 и 33 и сигналом операции на шину 6 управления генератора 30 тактовых им пульсов . Принцип записи соответствуе известному принципу записи в элемент памяти с замкнутой структурой. В это режиме работы постоянно замкнут ключ 29, и на выход блока 4 записи поступает записываемое число. Процесс счи тывания записываемого в накопитель 1 числа аналогичен известному, за исключением коммутгщки разрядными ключами 17, 18 запоминающих конденсаторов интегрирукнцих усилителей 9, 10по заднему фронту импульса записи с целью подготовки выходного устройства к следующему такту считывания . Сравнение входной и выходной величин в блоке 4 записи и запись разности в накопитель 1 происходят по сигналам управления, вьщаваемым генератором 30 тактовых импульсов. В режиме умнс кения одного записываемого числа на другое на шину 6 управления поступает сигнал задания операции. Генератор 30 тактовых импульсов, запускаясь по этому сигналу обеспечивает совместно с переключате лями 31, 32 и 33 в первый такт работ устройства одновременно считывание информации из накопителя 1 по второму адресу,вследствие чего на згшоминаюсцем конденсаторе интегрирующего усилителя 8 появляется напряжение Ujj пропорциональное по величине хранившемуся по второму адресу числу, и коммутацию ключом 29 входного напряжения и на вход интегрируницего усилителя 7. Режим коммутации элемента 19 стробирования в режиме умножения одного записываемого числа на другое аналогичен режиму коммутации при считывании числа. Во втором такте в выходном устройстве осуществляется умножение одной аналоговой величины и на величину (iy, и на выходе устройства появляется напряжение, пропорциональное f работы выходного устройства в этом такте аналогичен известному. Начиная со второго такта работы и до окончания процесса записи произведения двух чисел, ключ 29 находится в разомкнутом соетоянии. Сигнал окончания такта умножения поступает с нуль-органа 11 на второй вход генератора 30 тактовых импульсов и он формирует сигнал, поступающий на управляющий вход фиксатора 5 уровHHjкоторый запоминает и хранит напряжение, пропорциональное полученному произведению . По окончании процесса запоминания происходит сброс напряжения с запоминающих конденсаторов интегрирующих усилителей 7-10 с помощью разрядных ключей 15-18 и напряжение на выходе устройства становится равным нулю. В следующем такте работы по сиг налуу поступающему на управляющий вход блока 4 записи,,в блоке 4 записи происходит сравнение подаваемой на его первый вход величины и величины напряжения Ugyj,Ha выходе устройства в этот момент времени. В результате сравнения блок 4 записи формирует сигнал записи по первому адресу, пропорциональный .где . В следующем такте работы происходит считывание по первому адресу, в pef-. зультате которого на выходе устройства появляется напряжение Ц,-и,, где d,U - .погрешность, воз ник акяцая при записи в элемент памяти по первому адресу в первом такте записи. Периодический режим считывания по первому адресу обеспечивается генератором 30 тактовых импульсов и переключателями 31,32 и 33 .Следующий такт работы устройства - сравнение выходной величины Uj-Uji -cf U с величиной , хранимой в фиксаторе 5. Сравне-. ние производится в блоке 4 записи при поступлении на его управлягаций вход сигнала с генератора 30 тактовых имПульсов и при наличии на его первом входе напряжения с выхода фиксатора 5 уровня, и напряжения , считанного по первому адресу. В результате сравнения блок 4 записи формирует сигнал записи, пропорциональный U , После второго такта записи в элементе памяти накопителя 1 по первому адресу накапливается информадия , где dj-iJ - погрешность, возникающая при записи в элемент памяти по первому адресу во втором такте записи. В дальнейшем режим работы периодичен, т.е. происходит считывание по первому адресу, сравнение считанной величины с хранимой на фиксаторе 5 уровня, запись по первому адресу и т.д. При 3.fOM, начиная со второго такта записи, сброс напряжения с запоминающих конденсаторов интегриующих усилителей 9, 10 разрядными лючами 17, 18 с целью qoдгoтoвки выходного устройства к очередному такту считывания, производится по заданному фронту импульса записи. Режим записи произведения записываемых чиел продолжается до тех пор, пока JIj и в f-TOM такте записи не достигу

7 нет наперед заданной величины погреш ности записи. В предлагаемом устройстве для получения в накопителе 1 произведения одного записываемого числа на другое находящееся в накопителе, необходилм такт считывания второго числа U, такт умножения тактов записи произведения - определенной пог решностью. В данном случае для записи произведения записываемых чисел необходимо п+2 тактов работы устройства. Сравнение требуемого количества тактов работы устройства с извест Hbw устройством, в котором требуется 2h -3 тактов, свидетельствует о том, что предлагаемое устройство обладает повышенным быстродействием. В режиме деления одного записываемого числа на другое, находящееся в накопителе, на шину 6 управления поступает сигнал задания операции. Генератор 30 тактовых импульсов запускаясь по этому сигналу, обеспечивает совместно с переключателями 31, 32 и 33 в первый такт равоты уст ройства считывания информации из накопителя 1 по второму адресу, вследствие чего на запоминающем конденсаторе интег| иру101цего усилителя 8 появляется напряжение U2,пропорциональное по величине хранившемуся по второму адресу числу, и одновременно коммутацию ключом 29 на вход инте рирующего усилителя 7 напряжения (i. Режим коммутации элемента 19 стросирования в режиме деления одного записываемого числа на другое аналогичен известному режиму коммутации при считывании числа. Начиная со вто рого такта работы и до окончания процесса записи результата деления, ключ 29 находится в разомкнутом соетоянии. Во втором такте работы в выходном устройстве осуществляется деление одной аналоговой величины U2 на вторую и и на выходе устройства появляется напряжение, пропорционапь rioe U-j/lt;( . Режим работы выходного уст ройства в этбм также аналогичен иэвестному. Сигнал окончания такта деления поступает с нуль-органа 11 на второй вход генератора 30 тактовых импульсов, и он формирует сигнал, поступающий на управляющий вход фиксатора 5 уровня, который запоминает и хранит напряжение, пропорциональное полученному частному Uj/LI . По окончании процесса запоминания проис ходит сброс напряжения с запоминающих конденсаторов интегрирующих усилителей 7-10 с помощью разрядных клю чей 15-18 и напряжение на выходе уст ройства равно нулю .В следующем такте работы по сигналу, поступающему на управляющий вход блока 4 записи, происходит сравнение подаваемой на его первый вход величнно и величины напряжения ивьцС выхода уст8ройства. В результате сравнения блок 4 записи формирует сигнал записи, пропорциональный, -выи В следующем такте работы происходит считывание по первому адресу, в результате которого на выходе устройства появляется напряжение Uj/U -d IJ , где d и-погрешность, возникаю:-.ая при записи в элемент памятипо первому адресу в первом такте записи . Периодический режимсчитывания по первому адресу обеспечивается генератором 30 тактовых импульсов и переключателями 31, 32 и 33. Следующий такт работы устройства - сравнение выходной величины с величиной Uj/U, хранимой в (1)иксаторе 5 уровня . -В результате сравнения блок 4 записи вырабатывает сигнал записи, пропорциональный (TjU . После второго такта записи в элементе памяти накопителя 1 по первому адресу нахапливается информация ,где cf2U - погрешность, возникающая при записи в элемент памяти по первому адресу во втором такте записи. В дальнейшем режим работы периодичен, т.е. происходит считывание по первому адресу, сравнение считанной величины с хранимой на фиксаторе 5 уровня,запись по первому адресу и т.д. При этом, начиная со второго такта записи, сброс напряжения с запоминающих конденсаторов интегрирующих усилителей 9, 10 разрядными ключами 17, 18 с целью подготовки выходного устройства к очередному такту считывания производится по заднему фронту импульса записи. В известном методе для записи частного от деления одного записываемого числа на другое необходимо 2h +3 такта работы устройства. В предлагаемрм устройстве для получения в накопителе частного от деления одного записываемого числа на другое, хранимое в накопителе, необходимо п+2 тактов работы . Сравнение количества тактов работы устройства, необходимых для выполнения операции деления одного записываемого числа на второе, хранимое в накопителе, позволяет сделать заключение о том, что предлагаемое устройство обладает повышенным быстродействием. Таким образом, в предлагаемом устройстве при осугдествлении множительно-делительных операций над записываекыми числами достигается повышение быстродействия. Формула изобретения Аналоговое запоминающее устройство, содержащее накопитель, входы которого подключены к выходам блока выборки адресов, блок записи, блок поочередной выдачи кодов адресов, первые входы которого соединены с информационными шинами устройства, второй вход блока поочередной выдачи кодов адресов подключен к шине управленияи к одному из входов гене ратора тактовых импульсов, первый выход которого соединен с третьим входом блока поочередной выдачи кодов адресов и одним из вьлходов блока выборки адресов, другие входы которого соединены с выходами блока поочередной выдачи кодов адресов, четыре элемента стробирования, причем один из входов первого элемента стро бирования соединен со вторым выходом генератора тактовых импульсов, суммирующий усилитель, выход которого соединен с выходом устройства, нульорган, шесть ключей, четыре разрядны ключа, четыре интегрирующих усилителя, три переключателя режимов, при этом одни из входов второго и третье го элементов стробирования соединены с выходом накопителя и через первый переключатель режимов с одними из входов первого и четвертого элементов стробирования, другие входы элементов стробирования соединены с третьими выходами генератора тактовых импульсов, выходы элементов стро бнрования соединены с одними из входов интегрирующих усилителей, другие входы которых подключены к четвертым выходам генератора тактовых импульсов, выход первого интегрирующего усилителя через второй переключатель режимов соединен со входами суммирую щего усилителя и выходом второго интегрирующего усилителя, выход третье го интегрирующего усилителя соединен через нуль-орган со вторым входом генератора тактовых импульсов, выход четвертого интегрирующего усилителя через третий переключатель режимов соединен с одним из входов первого ключа, выход которого соединен с третьим входом третьего интегрирующего усилителя и выходом второго ключа, вход второго ключа соединен со входом третьего и четвертого ключей и шиной напряжения первого операнда, входы пятого и шестого ключей соединены с шиной напряжения второго операнда, выходы третьего и шестого ключей,соответственно, подсоединены к выходам первого и четвертого элементов стробирования, выходы четвертого и пятого ключей соединены со входами первого и четвертого элементов стробирования, управляющие входы ключей соединены с пятыми выходами генератора тактовых импульсов, о тличающееся тем, что, с целью поилшеВИЯ быстродействия устройства при выполнении множительноделительных операций, в него введены (Ьиксатор уровня и седьмой ключ, причем первый вход фиксатора уровня соединен с выходом устройства, выход фиксатора уровня соединен с первым входом блока записи, второй вход которого соединен с выходом устройства, при этом первый вход седьмого ключа является аналоговым входом устройства, а выход его подключен к первому входу блока записи и входу четвертого интегрирующего усилителя, управляющие же входы фиксатора уровня, блока записи и седьмого ключа соединены с шестыкш, выходами генератора тактовых импульсов, соответственно. Источники информации, принятые во внимание при экспертизе 1, Авторское свидетельство СССР по заявке I 2576368/18-24, кл. а 11 С 27/00,1978. 2. Авторское свидетельство СССР по заявке 2485267/18-24 (062722), л. G 11 С 27/00, 1977 (прототип).

л

п

n

a f

f

.п

JL

n

JL

n

Авторы

Даты

1981-01-23—Публикация

1979-03-26—Подача