(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1977 |

|

SU723686A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Ячейка памяти | 1979 |

|

SU1022222A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПИКОВЫХ ЗНАЧЕНИЙ | 2007 |

|

RU2343429C1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЧИСЛА ПРОСТОЕВ ОБОРУДОВАНИЯ | 1991 |

|

RU2017219C1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU849307A1 |

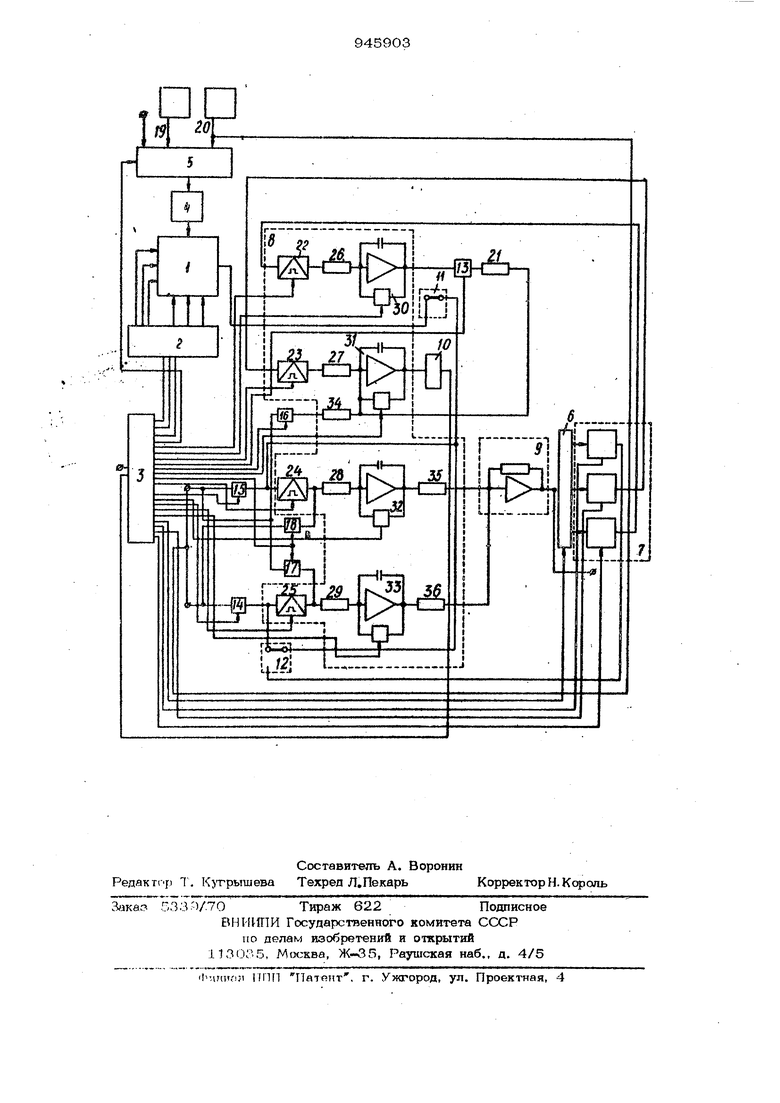

Изобретение относится к аналоговой вычислительной технике и может быть использовано в устройствах автоматики, измерительной и вычислительной техники. Известно аналоговое запоминающее устройство, содержащее накопитель, входы которог.о подключены к выходам блока выборки адресов, блок поочередной выдачи кодов адресов , первые входы кото рого соединены с информщионными шинами устройства, второй вход блока пооче редной вьодачи кодов адресов подключен к шине управления и к одному из входов генератора тактовых импульсов, первый вход которого соединен с третьим входом блока поочередной выдачи кодов адресов и одним таз входов блока выборки адресов другие входы которого соединены с выхо дами блока поочередной выдачи кодов адресов, четыре элемента стробирования, причем один из входов первого: элемента стробирования соединен с вторым выходом генератор тактовых импульсов, сум усилитель, выход которого соединен с выходом устройства, нутп орган, ключи, интегрирующие усилители, причем одни из входов второго и третьего элементов стробирования соединены с выходом накопителя и через первый переключатель с одними из входов первого и четвертого элементсш стробирования, другие входы элементов стробирования соединены с третьими выходами генератора тактовых импульсов, выходы элементов стробирования соединены с одними из входов интёг- Р1ФУЮЩИХ усилителей, другие входы которых подключены к четвертым выходам г&нератора тактов дх импульсов, вь1ХОД пёр- вого интегрирующего усилителя через второй переключатель соединен с входами суммирующего и выходом второго интегрирующего усилителя, третьего ин- тетТрирующегЪ усилителя соединен через нуль-орган с вторым входом генератора тактовых импульсов, выход четвертого интегрирующего усилителя через третий переключатель соединен с одним из входов первого ключа, выход которого соедвнен с третьим входом третьего интегрирующего, усилителя и выходом второго ключа, вход второго ключа соединен с . входом третьего и четвертого ключей и шийой напряжения первого операнда, входы пятого и шестого ключей соединены с шиной напряжения второго операнда, выходы третьего и шестого ключей соответственно подсоединены к входам первого и четвертого элементов стробирования, выходы четвертого и пятого ключей соеди нены соответственно с входами второго и первого интегрирующих усилителей, управляющие входы ключей соединены с пятыми иыходами генератора тактовых импульсов соответственно Cll . Однако известное устройство обладает пониженной точностью регистрации информации и способно, выпйлнять, кроме регистрации информации, только операции умножения и деления считываемых чисел. Известно также аналоговое запоминающее устройство, содержащее накопитель, входы которого подключены к выходам блока выборки адресов, блок поочередной вьщачн кодов адресов, первые входы кото рого соединены с информационными шинам устройства, второй вход блока поочередной выдачи кодов адресов подключен к шине управления и входу генератора тактовых импульсов, первый выход | оторого соединен с третьим входом блока поочередной выдачи кодов адресов и одним из входов блока выборки адресов, другие вхо ды которого соединены с выходами блока поочередной выдачи копов адресов, два блока стробирования, интегрирующие уси литепи и дифференциальный усилитель, при чем один из входов первого блока стробярования соединен с вторым выходом генератора тактовых импульсов, выход дифференциального усилителя соединен с выходом устройства, один из выходов второго блока стробирювания соединен с третьим выходом генератора тактовых импульсов, другие входь блоков стробировання соединены с выходом накопителя, выходы блоков стробирования соединены с одними из входов интегрирующих усилителей соответ ственно, выходы интегрирующих усилителей соединены соответственно с входами дифференпипяьного усилителя, другие входы интегрирующих усилителей подключены к четвертому и пятому выходам генератора тактовых импульсов соответственно Наиболее близким по технической сущности к предлагаемому являетсгя аналоговое запоминающее.устройство, содержащее накопитель, входы которого подклю- чены к входам блока выбора адреса и к выходу входного устройства, устройство управления, выходное устройство, два коммутационных ключа, три аналоговых элементапамяти, два сумматора, два источника эталонного напряжения, устройства умножения и деления, причем часть выходов устройства управления подключена к входам блока выбора адресов, а вход выходного устройства соединен с выходом накопителя, один из входов первого коммутационного ключа является входом всего устройства, другие входы присоединены к выходам источников эталонного напряжения, выход этого коммутационного ключа соединен с входом входного устройства, вход второго коммутахшонного ключа соединен с выходом выходного устройства, выходы этого ключа присоединены к входам аналоговых элементов памяти соответственно, причем управляющие вхо- ,ды коммутационных ключей и аналоговых элементов памяти соединены с соответствующими выходами устройства управления, выходы двух аналоговых элементов памяти присоединены к входам сумматоров, выход третьего аналогового элемента памяти присоединён к вычитающим входам обоих сумматоров, выход одного из них соединен с входом множительного устройства, другой вход которого присоединен к выходу одного из источников эталонного напряжения, выход множительного устройства соединен с выходом делительного устройства, другой вход которого присоединён к выходу второго сумматора, причем выход делительного устройства является выходом всего устройства CSJ . Недостатком этого устройства является сложность кояструкции, так как наряду с выходным устройством оно содержит два сумматора и устройства умножения и деления, причем с учетом сохранения быстродействия устройства, для реализации выходного устройства и устройств для выполнения арифметических операций необходимо, как минимум, девять операционных усилителей, из них три реализуют выходное устройство, два сумматора и по два усилителя необходимо для реализации схем умножения и деления. Отметим, что при этом выбрано минимально возможное Число усилителей для реализации схем умножения и деления, поясняющее лишь принципиально возможность их вьшолнения. Устройство обладает пониженной точностью регистрации информации и способно выполнять, кроме регистра1ши информации, только функции сложения и вычитания считываемых чисел. Целью изобретения является упрощение устройства при сохранении его точности и быстродействия, Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее основной накопитель, адресные входы которого соединены с выходом блока выбора адреса, информационный вход основного накопителя соединен с выходом блока записи, вход которого соединен с выходом первого ключа, одни вз информационных входов первого ключа являются первым входом устройства, а другие соединены с шинами эталонного напряжения, дополнительчый накопитель, информационные входы которого соединены с выходом второго ключа, блок управлени подключенный к блоку выбора адреса, дополнительному накопителю, блоку считыва ния, первому и второму ключам, сумматор первый переключатель, вход которого соединен с выходом основного накопителя введены третий, четвертый, пятый, шесто седьмой и восьмой ключи, нуль-орган, вто рой переключатэль, пассивный элемент, например резистор, причем информацион- ный вход третьего ключа соединен с перьвым выходом блока считьгоания, второй выход которого подключен к входу нульоргана, третий и четвертый выходы блока считывания соединены с входом сумматора, выход которого соединен с информационйым входом второго ключа и является выходом устройства, выход нуль-органа соединен с входом блока управления, выход первого переключателя соединен с первым входом второго переключателя, выход которого соединен с первым входом блока считьшания и с выходом четвертого ключа, информационные входы пятого, шес того и восьмого ключей 5тляются вторым входом устройства, информационные входы четвертого и седьмого ключей являются третьим входом устройства, управляющие входы ключей подключены к соответствую щим выходам блока управления, выход пятого ключа соединен с вторым входом блока считьюания и с выходом первого переключателя, выходы шестого, седьмого и восьмого ключей соединены соот ветственно с третьим, четвертым и пятым входами блока считывания, выход третьего ключа соединен через пассивный элемент с шестым входом блока считывания, первый и второй выходы дополнительного накопители.соединрны .соответственно с седьмым и восьмым входами блока счи- тывания, третий вход дополнительного накопителя соединен с вторым входом второго переключателя. Кроме того, блок считывания состоит из четырех каналов, каждый из которых содержит последовательно соединенные элемент стробирования, первый пассивный, элемент, например резистор и интегратор, в цепь обратной связи которого включен ключ и второй пассивный элемент, например резистор, выходы интеграторов каналов соединены соответственно с выходами блока считьшания, первые входы элементов стробирования соединены с управляющими входами блока считывания, вторые входы элементов стробирования первого и второго каналов соединены соответственно с первым и вторым входами блока считьшания, первый вывод второго резистора соединен с третьим входом блока считывания, второй вывод второго резистора соединен с входом интегратора третьего канала, выходы элементов стробирования второго и первого каналов под ключены соответственно к четвертому и к пятому входам блока считв тания, второй вывод второго резистора третьего канала соэдинен с шестым входом блока считывания, входы элементов стробнровання третьего и четвертого каналов соединены соответственно с седьмым и с восъ мым входами блока считывания. На чертеже представлена функциональная схема предложенного устройства. Устройство содержит основной накопитель 1, блок 2 выбора адреса, блок 3 управления, блок 4 записи, первый и второй ключи 5 к 6, дополнительный накопитель 7, блок 8 считывания, сумматор 9, нульгюрган 1О, переключатель 11 и. 12, третий, четвертый, пятый, шестой, седьмой и восьмой ключи 13 - 18, шины 19 и 20 эталонного напряжения, пассившдй элемент, например резистор 21. Блок 8 считътання содержит элементы 22-25 стробирования, пассивные элементы, например резисторы 26 - 29, интеграторы ЗО - 33, второй пассивнъ1й элемент, например резистор 34, третий и четвертый пассивные элементы, например резисторы 35 и 36. Устройство работает следуюйхим об{эазом. В первый такт работы осуществляется запись от эталонного источника напряжения величины Ug по шинам 2О в элемент памяти накопителя 1 по первому адресу, выбор которого обеспечивается совмесч но блоком 2 выбора адреса и блоком 8 считывания. Во втором такте рабрты устройства происходит считьгоание информации, записанной по первому адресу в накопитепе 1. В этом такте работы первые входы элементов стробирования соединены с помощью переключателей 11 и 12 с выходной шиной накопителя 1. Считанная величина аналоговой информации UQ запоминается в элементе накопителя 7, который подключается к выходу сумматора 9 ключом 6. Третий такт работы - запись величшЫ Ua по первому адресу в элемент памяти накопителя 1. В четвертом такте работы при считывании по первому адресу информашш и переключатель 12 соединяет выход элемента 7 памяти с входом элемента 25 стробирования, при этом элементы 24 и 25 стробирования коммутируются импульсами программы алгебраи ческого сложения, вырабатываемой блоком 3 управления. Результатом выполнения этой операции есть разность Oj -Up , ко торая запоминается на элементе памяти накопителя 7. В следующем такте работы происходит запись величины U- в накопитель 1 по первому адресу. В шестом так те работы осуществляется считывание записанной по первому адресу накопителя 1 величины UL.C одновременнымвычитанием из нее величины Ug . хранимой в элемен- те памяти накопителя 7. Резуль ты операции - разность (jL - и запоминается в элементе памяти накопителя 7. В седьгмом такте работы устройства осуществляется множительно-делитеяьные опера1пш над aнaлoгoвIfl fи величинами, зфанящимяся в элементах пймяти накопителя 7 и величиной TJI источника эталонного напряжения Для этого заблокированные ранее элементы 22 и 23 стробирования и ключи 13- 18 начинают работать в режиме осуществ ления операции деления, причем величина U-jj - UQ подключена к входу интегратора 31, а величина U- UQ - к входу интегратора 32.. В результате ц.-К-) u;:-ui Таким образом, наряду с операцией считывания информашш непосредственно в блоке 8 считывания осуществляются арифметические операции, необходимые для повьпиения точности его работы. При оценке количества оборудования, необходимая о для реализации данной функции в предложенном устройстве и в известном мизо ходим о учесть, что быстродействующие аналоговые запоминающие устройства требуют специальнь1Х выходных устройств усложненной конструкции, в частности, минимально возможное время считьшания достигается с помощью выходного устройства, содержащего дваинтегрирующих усилителя с разрядными ключами, два элемента стробирования и дифференциальный усилитель. Предложенное устройство для выполнения арифметических операций создано с использованием пяти операционных усилителей и одного дополнительного переключателя. (При анализе аппаратурных затрат на реализацию устройств операхшонный усилитель принят наиболее сложным узлом, а сопутствующие активные и пассивные компоненть не учитывались). Таким образом, достигнуто упрощение конструкции устройства при сохранении его точности и быстродействия, так как для обработки аналоговых сигналов в предложенном устройстве требуется поч- га вдвое меньшее количество оборудования. Формула изобретения 1. Аналоговое запоминающее устройство, содержащее основной накопитель, адресные входы которого соединены с выходом блока выбора адреса, информационный вход основного накопителя соеди нен с выходом блока записи, .вход которого соединен с выходом первого ключа, одни из информационных выходов первого ключа являются первым входом устройства, а другие соединены с шинами эталонного напряжения, дополнительный накопи тель, информационные входы которого соединены с выходом второго ключа, блок управления, подключенный к блоку выбора адреса, дополнительному накопителю, блоку считывания, первому и второму ключам, сумматор, первый переключатель, вход которого соединен с выходом основного накопителя, отличающее - с а тем, что, с целью упрощения устрой- стаа, в него введены третий, четвертый, пятый, шестой, седьмой, восьмой ключи, нуль-орган, второй переключатель, пассивный элемент, например резистор, причем ннформацнонный вход третьего ключа соединен с первым выходом блока считывания/второй выход которого подключен к входу нуль-органа, третий и четвертый выходы блока считывания соединены с взводом сумматора, выход которого соёд1б1ен с информациот1ым входом второго 1атюча и является выходом устройства, Ьыход нуль-органа соединен с входом блока управления, выход первого переключателя соединен с первым входом второго переключателя, выход которого соединен с первым входом блока считьша- НИН и с выходом четвертого ключа, информационные входы пятого, шестого и BOCliMOrO ключей являются вторым входом устройства, тшформационные йходы чет вертого и седьмого ключей являются третьим входом устройства, управляющие входы ключей подключены к соответствую щим выходам блока управления, выход пятого ключа соединен с вторым входом блока считьшания и с выходом первого переключателя, выходы шестого, седьмого я восьмого ключей соединены соответс венно с третьим,, четвертым и пятым вход ми блока считывания, выход третьего клю ча соединен через пассивный элемент с шестым входом блока считывания, первый и второй выходы дополнительного накопителя соединены соответственно с седьмы в восьмым входами блока считьшания, тре тий выход дополнительного накопи1реля соединен с вторым входом второго переключателя. 2. Устройство по п. 1. о т л и ч а ю ш е е с я тем, что блок считывания сос тоит из четырех каналов, каждый из которых содержит последовательно соединенные элемент стробирования, первый пассивный элемент, например резистор и ин943 тегратор, в цепь оЬратной связи которого включен клкзч, и второй пассивный элемент, например резистор, выходы интеграторой каналов являются выходами блока считывания, первые входы элементов стробирования яовляются управляющими входами блока считывания, вторые входы элементов стробирования первого и второго каналов являются соответственно с первым и вторым входами блока считывания, первый вывод второго резистора является третьим входом блока считьгоания, второй вьгаод второго резистора соединен с входом интегратора третьего канала, выходы элементов стробирования второго и первого каналов соединены соответственно с первыми выводами третьего и четвертого пассивных элементов, например резисторов, вторые вьшоды которых являются соответственно четвертым и пягым входами блока считывания, второй вывод второго резисfopa третьего канала является шестым входом блока считывания, входы элементов стробирования третьего и четвертого каналов являются соответственно седьмым и восьмым входами блока считывания. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР NO 720514, кл. Q 11 С 27/00, 1977. 2.Авторское свидетельство СССР № 723686, кл. Q 11 С 27/ОО, 1977. 3.Авторское свидетельство СССР по заявке № 2699917/18-24, кл. Gi 11 С 27/ОО, 09.01.79 (прототип).

Авторы

Даты

1982-07-23—Публикация

1980-10-29—Подача