выход второго элемента ИЛИ является вторым выходом анализатора,

3. Устройство по п. 1, отличающееся тем, что анализатор нулевых значений операндов содержит одиннадцать элементов И и элемент ИЛИ, причем первый вход анализатора соединен с входами с первого по четвертый первого элемента И, второй вход анализатора соединен с входами второго элемента И с первого по четвертый , первый вход анализатора соединен с первыми входами элементов И с третьего по шестой, вторые входы которых подключены к выходу второго элемента И, второй вход анализатора соединен с первыми входами элементов И с седьмого по десятый, вторые входы которых соединены с выходом первого элемента И, выходы первого и второго элементов И соединены с входами элемента ИЛИ и одиннадцатого элемента И, третий вход анализатора соединен с пятыми входами первйго и второго элементов И, выходы элемента ИЛИ и одиннадцатого элемента И являются соответственно первым и вторым выходами анализатора, выходы элементов И с третьего по десятый являются третьим выходом анализатора.

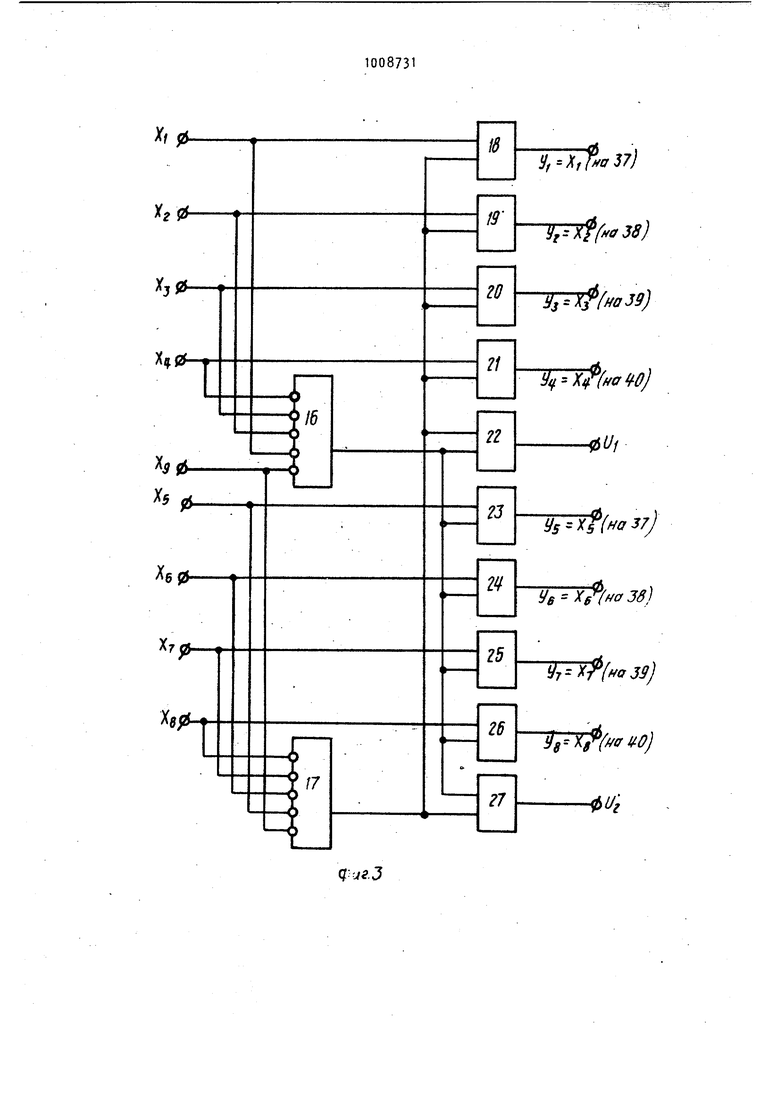

k. Устройство по п, 1, отличающееся тем, что шифратор результата содержит тринадцать элементов ИЛИ, восемь элементов И, элемент НЕ, причем выходы элементов И с первого по восьмой являются выходом шифратора, а их первые входы соединены соответственно с выходами элементов ИЛИ с первого по восьмой, первые входы которых соединены с первым входом шифратора, вторые входы элементов И с первого по третий соединены с первыми входами элементов ИЛИ с девятого по тринадцатый, входом элемента НЕ и третьим входом шифратора, вторые входы элементов И с четвертого по восьмой соединены соответственно с выходами элементов ИЛИ с девятого по тринадцатый, вторые входы которых соединены с вторым входом шифратора, третьи входы элементов ИЛИ с десятого по тринадцатый соединены с четвертым входом шифратора, пятый вход которого соединен с четвертым входом тринадцатого элемента ИЛИ, вторые входы элементов ИЛИ с четвертого по восьмой соединены с выходом элемента НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

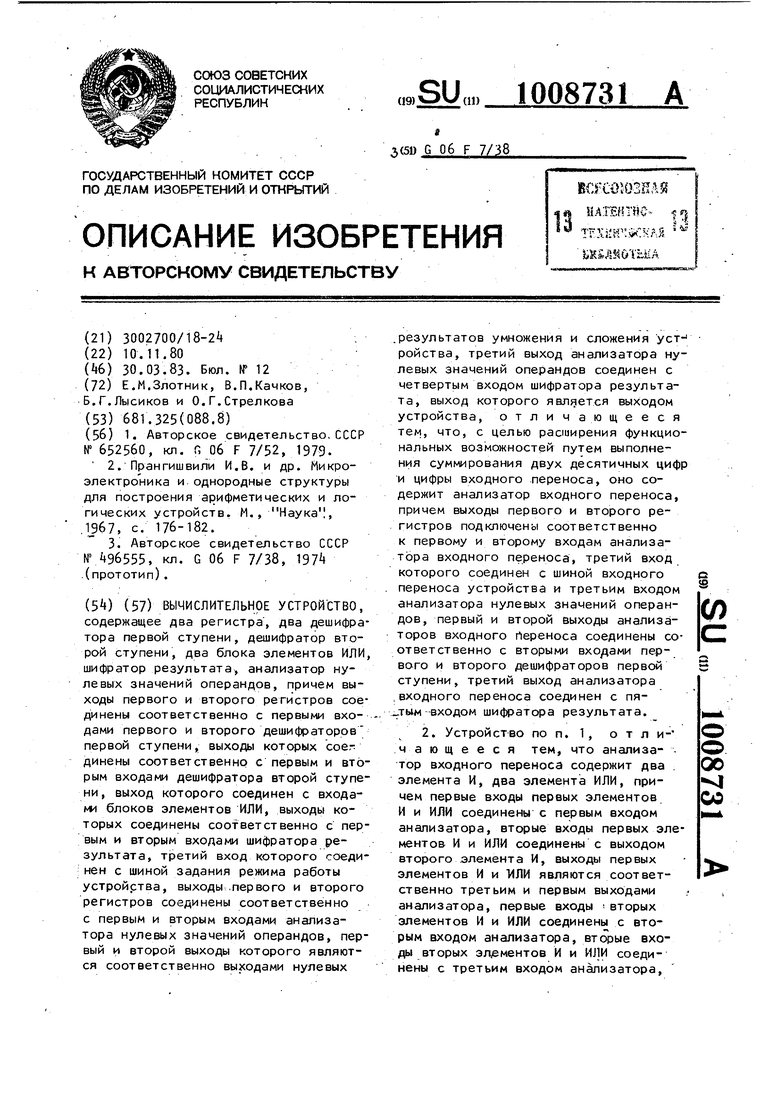

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО, содержащее два регистра , два дешифратора первой ступени, дешифратор второй ступени, два блока элементов ИЛИ, шифратор результата, анализатор нулевых значений операндов, причем выходы первого и второго регистров соединены соответственно с первыми входами первого и второго дешифраторов первой ступени, выходы которых сое,динены соответственно с первым и вторым входами дешифратора второй ступени, выход которого соединен с входами блоков элементов ИЛИ, выходы которых соединены соответственно с первым и вторым входами шифратора результата, третий вход которого соеди: ней с шиной задания режима работы устройртва, выходы., пер во го и второго регистров соединены соответственно с первым и вторым входами анализатора нулевых значений операндов, первый и второй выходы которого являются соответственно выходами нулевых .результатов умножения и сложения устройства, третий выход анализатора нулевых значений операндов соединен с четвертым входом шифратора результата, выход которого является выходом устройства, отличающееся тем, что, с целью расширения функциональных возможностей путем выполнения суммирования двух десятичных цифр и цифры входного переноса, оно содержит анализатор входного переноса, причем выходы первого и второго регистров подключены соответственно к первому и второму входам анализатора входного переноса, третий вход которого соединен с шиной входного i переноса устройства и третьим входом (О анализатора нулевых значений операндов, первый и второй выходы анализаторов входного переноса соединены соответственно с вторыми вкоцами первого и второго дешифраторов первой ступени, третий выход анализатора .входного переноса соединен с входом шифратора результата. 2. Устройство по п. 1, о т л ичающееся тем, что анализа- 00 тор входного переноса содержит два . элемента И, два элемента ИЛИ, присо чем первые входы первых элементов И и ИЛИ соединены с первым входом анализатора, вторые входы первых элементов И и ИЛИ соединены с выходом второго .элемента И, выходы первых элементов И и ИЛИ являются соответственно третьим и первым выходами анализатора, первые входы вторых элементов И и ИЛИ соединены с вторым входом анализатора, вторые входы вторых элементов И и ИЛИ соединены с третьим входом анализатора.

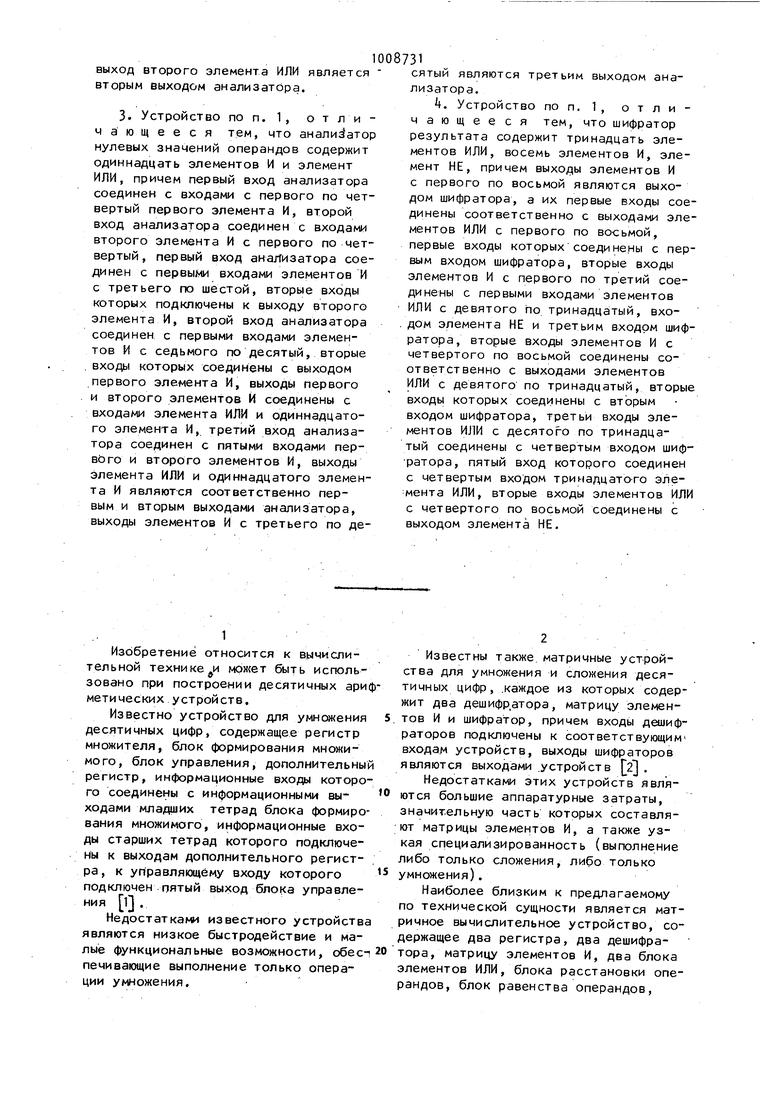

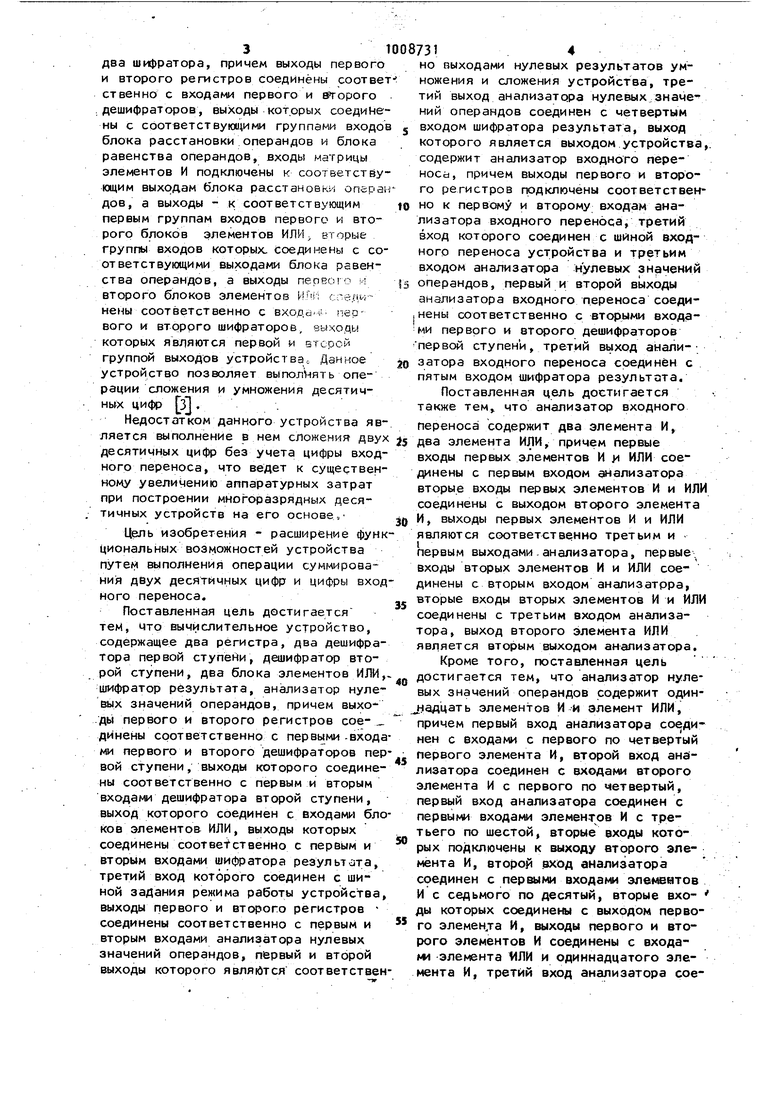

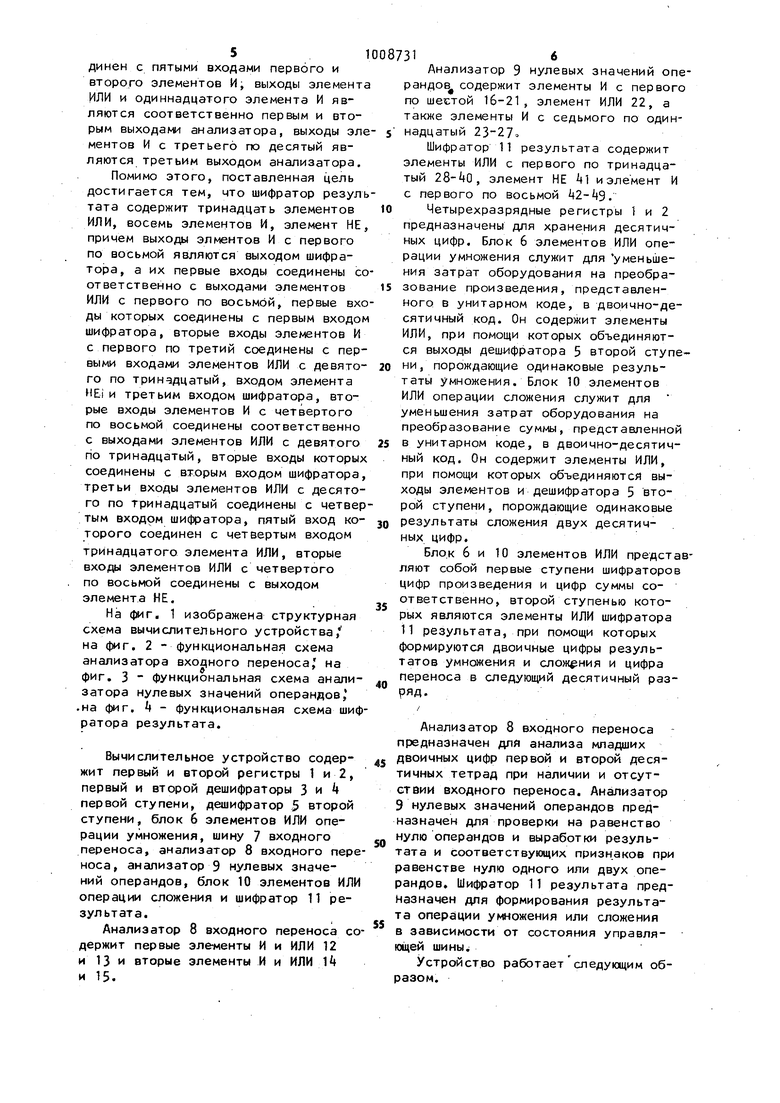

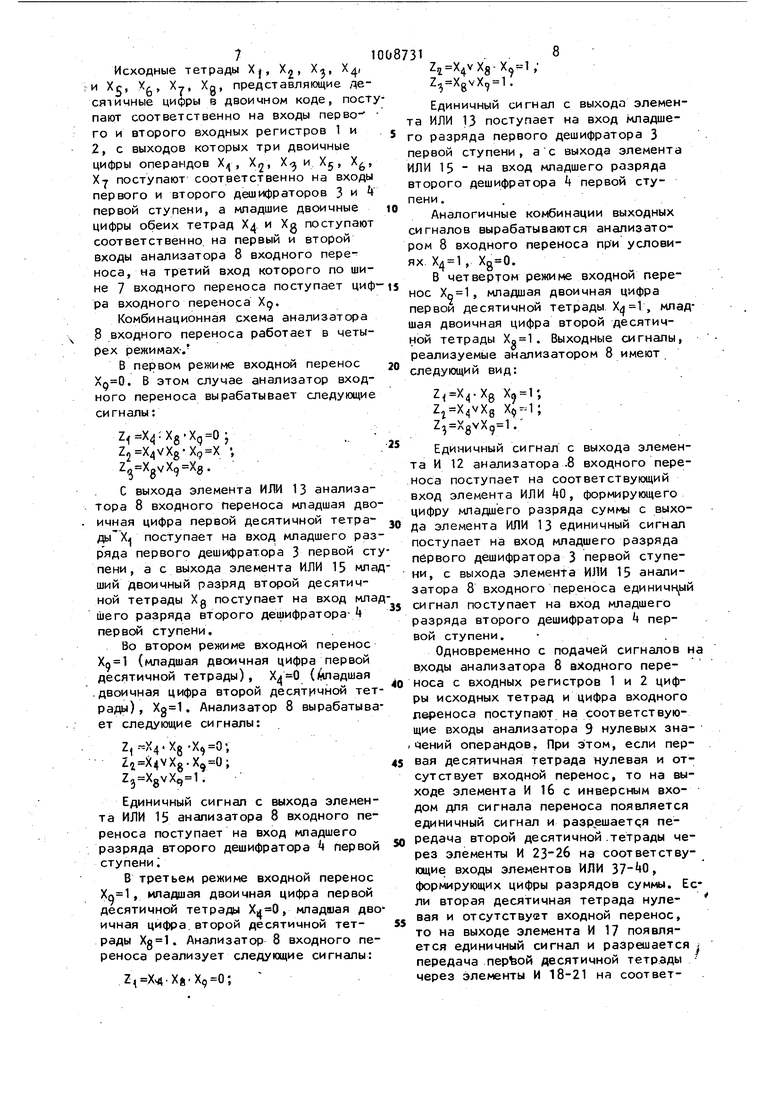

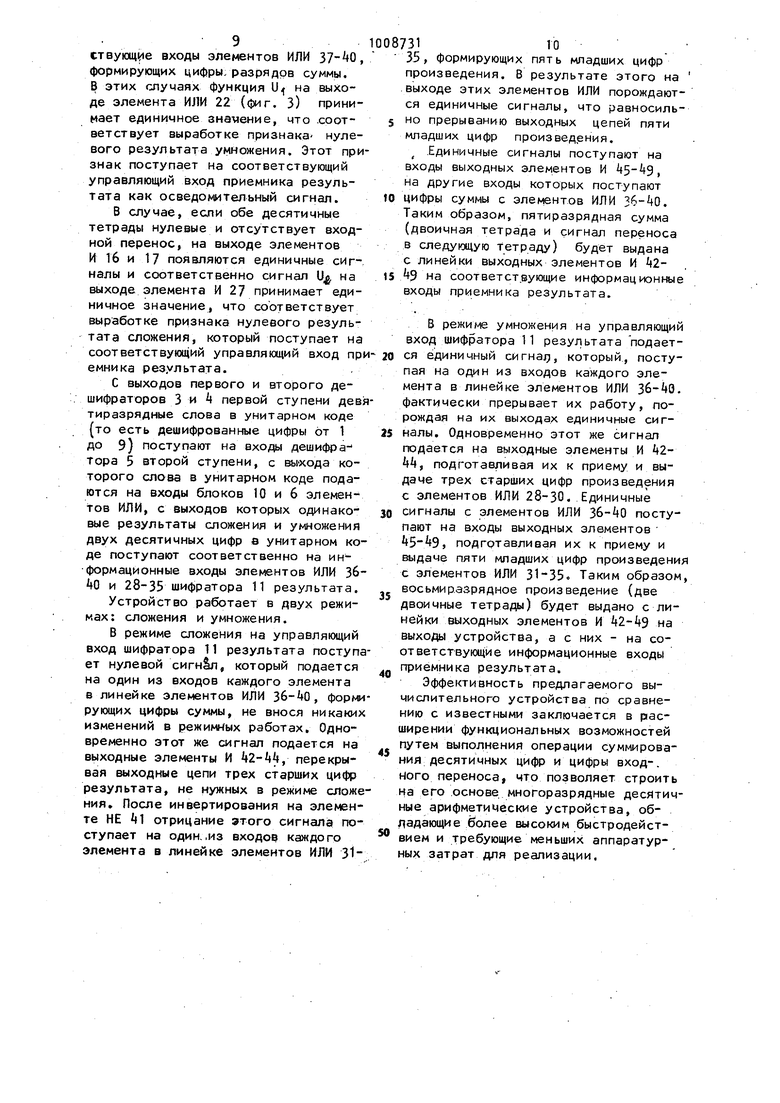

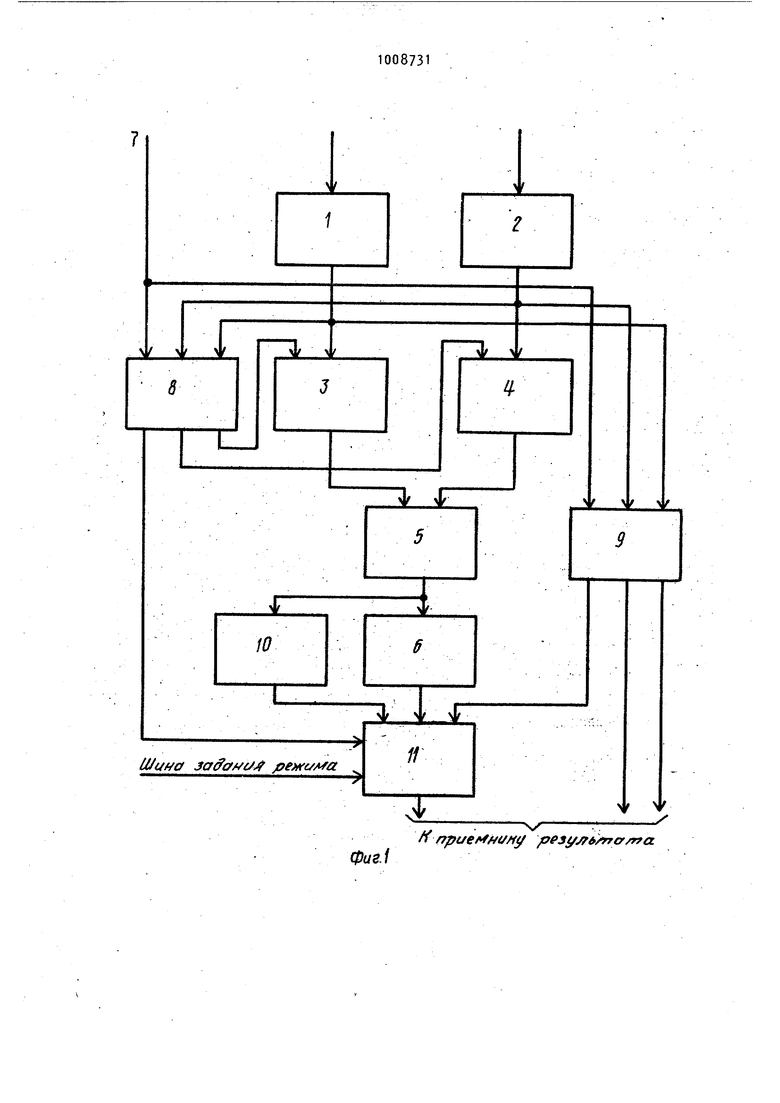

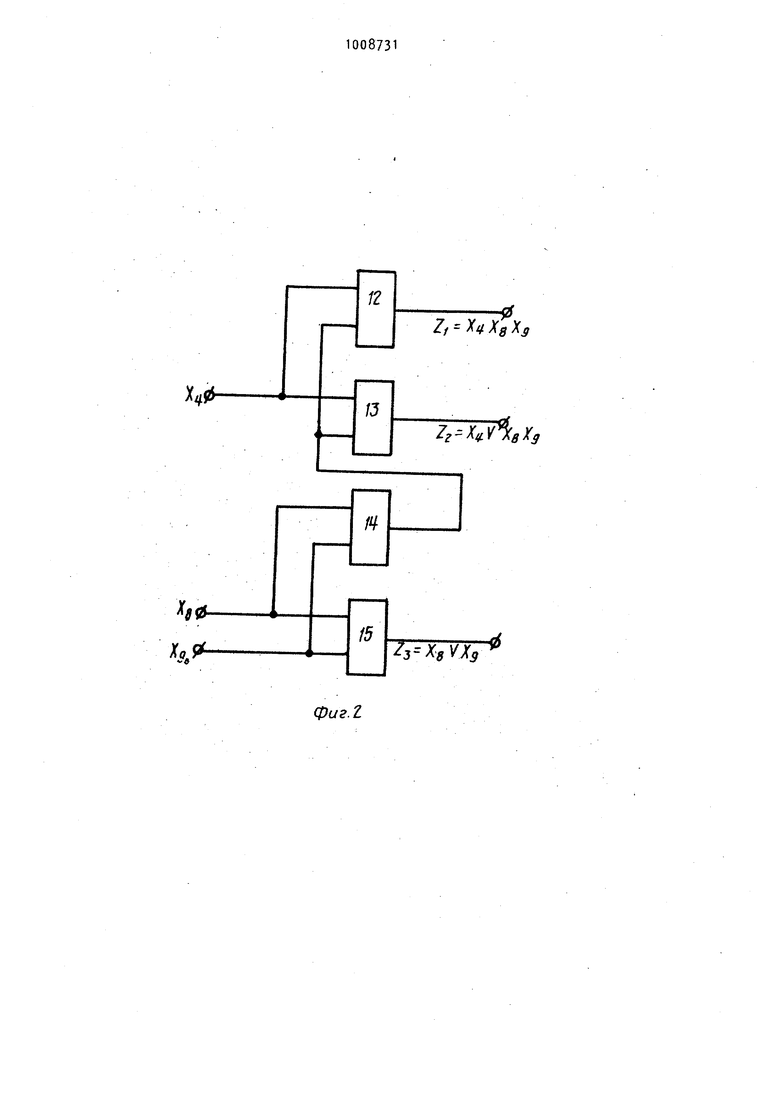

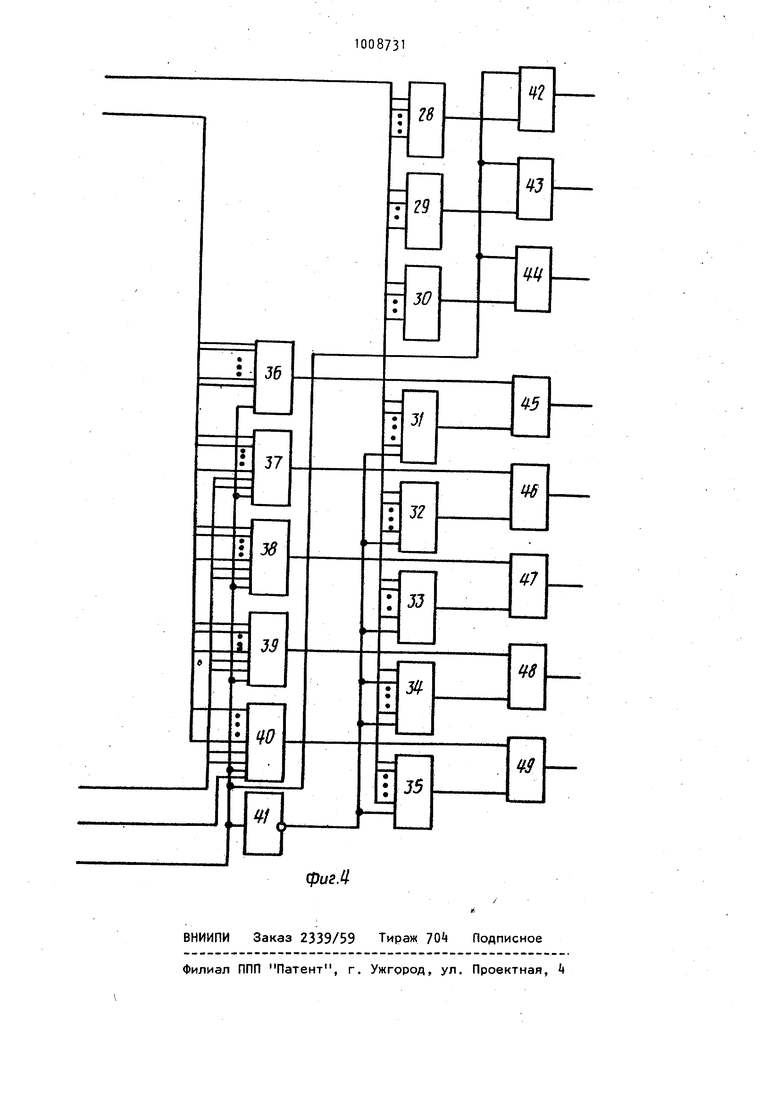

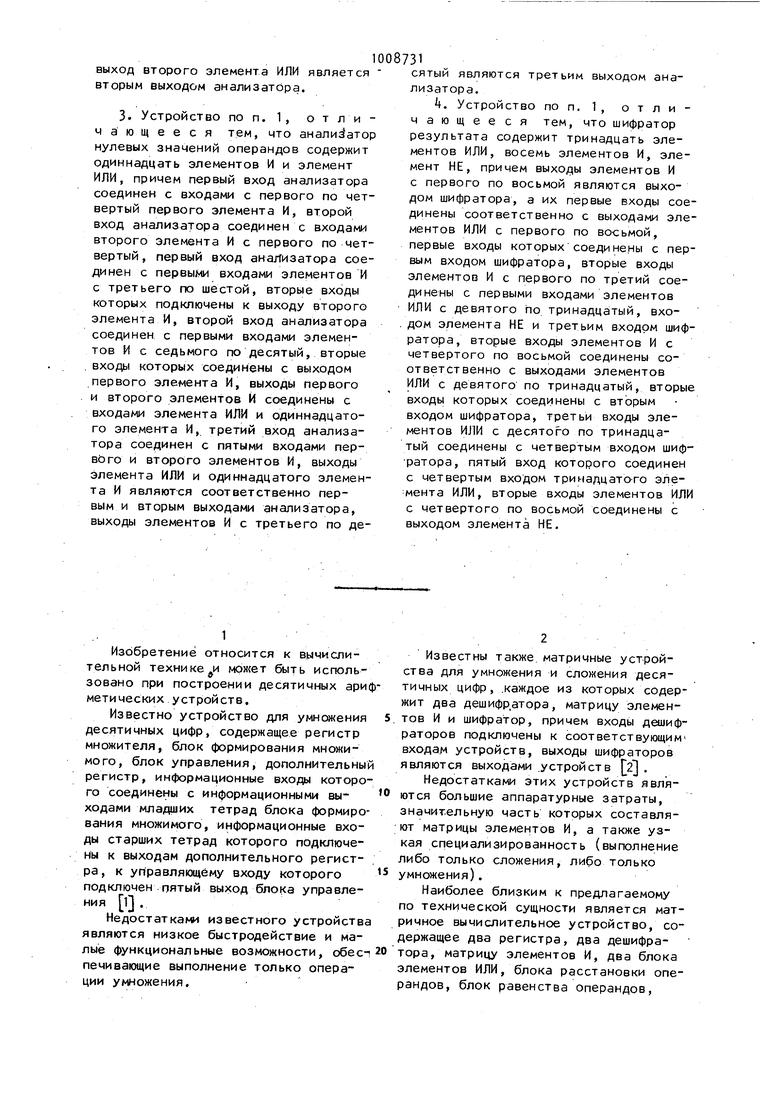

Изобретение относится к вычислительной технике .и может быть использовано при построении десятичных ари метических устройств. Известно устройство для умножения десятичных цифр, содержащее регистр множителя, блок формирования множимого, блок управления, дополнительны регистр, информационные входы которо го соединены с информационными выходами младших тетрад блока формиро вания множимого, информационные входы старших тетрад которого подключены к выходам дополнительного регистра , к управляющему входу которого подключен пятый выход блока управления Л . Недостатками известного устройств являются низкое быстродействие и малые функциональные возможности, обес печивающие выполнение только операции умножения. Известны также, матричные устройства для умножения и сложения десятичных цифр, .каждое из которых содержит два дешифратора, матрицу элементов И и шифратор, причем входы дешифраторов подключены к соответствующим входа.м устройств, выходы шифраторов являются выходами .устройств 2J . Недостатками этих устройств являются большие аппаратурные затраты, значительную часть которых составляют матрицы элементов И, а также узкая специализированность (выполнение либо только сложения, либо только умножения). Наиболее близким к предлагаемому по технической сущности является матричное вычислительное устройство, содержащее два регистра, два дешифратора, матрицу элементов И, два блока элементов ИЛИ, блока расстановки операндов, блок равенства операндов. два шифратора, причем выходы первого и второго регистров соединены соответ ственно с входами первого и второго . дешифраторов, выходы которых соединены с соотеетствуюцими группами входов блока расстановки операндов и блока равенства операндов, входы матрицы элементов И подключены к соответствующим выходам блока расстановки операн дов, а выходы - к соответствующим первым группам входов первого и второго блоков элементов ИЛИ вторые группы входов которых, соединены с соответствующими выходами блока равенства операндов, а выходы первого м второго блоков элементов ИЛИ соединены соответственно с входа первого к второго шифраторов, выходы которых являются первой и втсрой группой выходов устройства. Данное устройство позволяет выполнять операции сложения и умножения десятичны х цифр з .. Недостатком данного устройства является выполнение в нем сложения двух десятичных цифр баз учета цифры входного переноса, что ведет к существенному увеличению аппаратурных затрат при построении многоразрядных десятичных устройств на его основе Цель изобретения - расширение функ циональных возможностей устройства путем выполнения операции суммирования дВух десятичных цифр и цифры вход ного переноса. Поставленная цель достигается тем. Что вычислительное устройство, содержащее два регистра, два дешифратора первой ступени, дешифратор второй ступени, два блока элементов ИЛИ, шифратор результата, анализатор нулевых значений операндов, причем выходь1 первого и второго регистров сое- динеНы соответственно с первыми -входа ми первого и второго дешифраторов пер вой ступени, выходы которого соединены соответственно с первым и вторым входам дешифратора второй ступени, выход которого соединен с входами бло ков элементов ИЛИ, выходы которых соединены COOTBetствеНно с первым и вторым входами шифратора результэта, третий вход которого соединен с шиной задания режима работы устройства выходы первого и второго регистров соединены соответственно с первым и вторым входами анализатора нулевых значений операндов, п1врвый и второй выходы которого являйтся соответствен но выходами нулевых результатов умножения и сложения устройства, третий выход анализатора нулевых/значе НИИ операндов соединен с четвертым входом шифратора результата, выход которого является выходом устройства,. содержит анализатор входного переноса, причем выходы первого и второго регистров подключены соответственно к первому и второму входам анализатора входного переноса, третий вход которого соединен с шиной входного переноса устройства и третьим входом анализатора нулевых значений операндов, первый и второй вь1ходы анализатора входного переноса соединены соответственно с вторыми входами первого и второго дешифраторов первой ступени, третий выход анали- затора входного переноса соединён с пятым входом шифратора результата. Поставленная цель достигается также тем, что анализатор входного переноса содержит два элемента И, два элемента ИЛИ, причем первые входы первых элементов И л ИЛИ соединены с первым входом ализатора вторые входы первых элементов И и ИЛИ соединены с выходом второго элемента И, выходы первых элементов И и ИЛИ являются соответственно третьим и первым выходами-анализатора, первые, входы втсчэых элементов И и ИЛИ соединены с вторым входом анализатрра, вторые входы вторых элементов И и ИЛИ соединены с третьим входом анализатора, выход второго элемента ИЛИ является вторым выходом анализатора. Кроме того, поставленная цель достигается тем, что анализатор нулевых значений операндов содержит одинiaAUaTb элементов И и элемент ИЛИ, причем первый вход анализатора соединен с входами с первого по четвертый первого элемента И, второй вход aHaiлизатора соединен с входа второго элемента И с первого по четвертый, первый вход анализатора соединен с первыми входами элементов И с третьего по шестой, вторые входы которых подключены к выходу второго элемента И, второй .вход анализатора соединен с входами элементов И с седьмого по десятый, вторые входы которых соединены с выходом первого элеменда И, выходы первого и второго элементов И соединены с входами элемента VIЛИ и одиннадцатого элемента И, третий вход анализатора соединен с пятыми входами первого и второго элементов И, выходы элемента ИЛИ и одиннадцатого элемента И являются соответственно первым и вторым выходами анализатора, выходы эле ментов И с третьего по десятый являются третьим выходом анализатора. Помимо этого, поставленная цель достигается тем, что шифратор резул тата содержит тринадцать элементов ИЛИ, восемь элементов И, элемент НЕ причем выходы элментов И с первого по восьмой являются выходом шифратора, а их первые входы соединены со ответственно с выходами элементов ИЛИ с первого по восьмой, первые вхо ды которых соединены с первым входо шифратора, вторые входы элементов И с первого по третий соединены с первыми входами элементов ИЛИ с девятого по тринадцатый, входом элемента НЕ и третьим входом шифратора, вторые входы элементов И с четвертого по восьмой соединены соответственно с выходами элементов ИЛИ с девятого ho тринадцатый, вторые входы которых соединены с вторым входом шифратора третьи входы элементов ИЛИ с десятого по тринадцатый соединены с четвер тым входом шифратора, пятый вход которого соединен с четвертым входом тринадцатого элемента ИЛИ, вторые входы элементов ИЛИ с четвертого по восьмой соединены с выходом элемента НЕ. На фиг. 1 изображена структурная схема вычислительного устройства/ на фиг. 2 - функциональная схема анализатора входного переноса/ на фиг. 3 - функциональная схема анализатора нулевых значений операндов, .на фиг. Ц - функциональная схема шиф ратора результата. Вычислительное устройство содержит первый и второй регистры 1 и 2, первый и второй дешифраторы 3 и i первой ступени, дешифратор 5 второй ступени, блок 6 элементов ИЛИ операции умножения, шину 7 входного переноса, анализатор 8 входного пере носа, анализатор 9 нулевых значений операндов, блок 10 элементов ИЛИ операции сложения и шифратор 11 результата. Анализатор 8 входного переноса со держит первые эле-менты И и ИЛИ 12 и 13 и вторые элементы И и ИЛИ I) и 15. 316 Анализатор 9 нулевых значений операндов содержит элементы И с первого по шестой 16-21, элемент ИЛИ 22, а также элементы И с седьмого по одиннадцатыйШифратор 11 результата содержит элементы ИЛИ с первого по тринадцатый 28-40, элемент НЕ 1 иэлемент И с первого по восьмой . Четырехразрядные регистры 1 и 2 предназначены для хранения десятичных цифр. Блок 6 элементов ИЛИ операции умножения служит для уменьшения затрат оборудования на преобразование произведения, представленного в унитарном коде, в двоично-десятичный код. Он содержит элементы ИЛИ, при помощи которых объединяются выходы дешифратора 5 второй ступени, порождающие одинаковые результаты умножения. Блок 10 элементов ИЛИ операции сложения служит для уменьшения затрат оборудования на преобразование суммы, представленной в унитарном коде, в двоично-десятичный код. Он содержит элементы ИЛИ, при помощи которых объединяются выходы элементов и дешифратора 5 второй ступени, порождающие одинаковые результаты сложения двух десятичных цифр. Блок 6 и 10 элементов ИЛИ представляют собой первые ступени шифраторов цифр произведения и цифр суммы соответственно, второй ступенью которых являются элементы ИЛИ шифратора 11 результата, при помощи которых формируются двоичные цифры результатов умножения и сложения и цифра переноса в следующий десятичный разряд. Анализатор 8 входного переноса предназначен для анализа младших двоичных цифр первой и второй десятичных тетрад при наличии и отсутствии входного переноса. Анализатор 9 нулевых значений операндов предназначен для проверки на равенство нулю операндов и выработки результата и соответствующих признаков при равенстве нулю одного или двух операндов. Шифратор 11 результата предназначен для формирования результата операции умножения или сложения в зависимости от состояния управляющей шины Устройство работает следующим образом. 7 Исходные тетрады Xj, Х2, Х, Х, и Хс, Х, Ху, Хд, представляющие деся1ичные цифры в двоичном коде, пост пают соответственно на входы пер вого и второго входных регистров 1 и 2, с выходов которых три двоичные цифры операндов Хц, Х, Х и Xg, Х, XY поступают соответственно на входы первого и второго дешифраторов 3 и % первой ступени, а младшие двоичные цифры обеих тетрад Х и Xg поступают соответственно, на первый и второй входы анализатора 8 входного переноса, на третий вход которого по шине 7 входного переноса поступает цмф pa входного переноса Хф, Комбинационная схема анализатора 8 входного переноса работает в четырех режимах-. В первом режиме входной перенос . В этом случае анализатор входного переноса вырабатывает следующие сигналы: Z X -Xg-Xg 0Zj , . С выхода элемента ИЛИ 13 анализатора 8 входного переноса младшая дво ичная цифра первой десятичной тетрадьГХ поступает на вход младшего раз ряда первого дешифратора 3 первой ст пени, а с выхода элемента ИЛИ 15 мла ший двоичный разряд второй десятичной тетрады Xg поступает на вход мла шего разряда второго дешифратора- 4 первой ступени. Во втором режиме входной перенос (младшая двоичная цифра первой десятичной тетрады), (падшая .двоичная цифра второй десятичной тет рады) , . Анализатор 8 вырабатыва ет следующие сигналы: 1 4 Xg , Zj X4VXg.X,0; Z5 XgvXq 1. Единичный сигнал с выхода элемента ИЛИ 15 анализатора 8 входного переноса поступает на вход младшего разряда второго дешифратора 4 первой ступени . В третьем режиме входной перенос , иладшая двоичная цифра первой десятичной тетрады , младиая дво ичная цифра.второй десятичной тетрады . Анализатор 8 входного переноса реализует следующие сигналы: Z,X«4.XeX9 0; 31 Xg- , XQVX,I. Единичный сигнал с выхода элемента ИЛИ 13 поступает на вход младшего разряда первого дешифратора 3 первой ступени, ас выхода элемента ИЛИ 15 - на вход младшего разряда второго дешифратора k первой ступени. Аналогичные комбинации выходных сигналов вырабатываются анализатором 8 входного переноса при условиях , . В четвертом режиме входной перенос , младшая двоичная цифра первой десятичной тетрады. X(, младшая двоичная цифра второй десятичной тетрады . Выходные сигналы, реализуемые анализатором 8 имеют следующий вид: Х4-Х8 AgVX( . Единичный сигнал с выхода элемента И 12 анализатора -8 входного переноса поступает на соответствующий вход элемента ИЛИ 40, формирующего цифру младшего разряда суммы с выхода элемента ИЛИ 13 единичный сигнал поступает на вход младшего разряда первого дешифратора 3 первой ступени, с выхода элемента ИЛИ 15 анализатора 8 входного переноса единичн ый сигнал поступает на вход младшего разряда второго дешифратора k первой ступени. Одновременно с подачей сигналов на входы анализатора 8 входного переноса с входных регистров 1 и 2 цифры исходных тетрад и цифра входного переноса поступают, на соответствующие входы анализатора 9 нулевых значений операндов. При этом, если первая десятичная тетрада нулевая и отсутствует входной перенос, то на выходе элемента И 16 с инверсным входом для сигнала переноса появляется единичный сигнал и разрешается передача второй десятичной.тетрады через элементы И 23-26 на соответствующие входы элементов ИЛИ , формирующих цифры разрядов суммы. Ее ли вторая десятичная тетрада нулевая и отсутствует входной перенос, то на выходе элемента И 17 появляется единичный сигнал и разрешается передача пер%ой десятичной тетрады через элементы И 18-21 на соответствущие входы элементов ИЛИ , формирующих цифры, разрядов суммы. В этих случаях функция (i на выходе элемента ИЛИ 22 (фиг. З) принимает единичное значение, что .соответствует выработке признака- нулевого результата умножения. Этот признак поступает на соответствующий управляющий вход приемника результата как осведомительный сигнал. В случае, если обе десятичные тетрады нулевые и отсутствует входной перенос, на выходе элементов И 16 и 17 появляются единичные сигналы и соответственно сигнал 11 на выходе элемента И 27 принимает единичное значение, что соответствует выработке признака нулевого результата сложения, который поступает на соответствующий управляющий вход при емника результата. С выходов первого и второго дешифраторов 3 и 4 первой ступени дев; тиразрядные слова в унитарном коде (то есть дешифрованные цифры от 1 до 9) поступают на входы дешифра тора 5 второй ступени, с выхода которого слова в унитарном коде подаются на входы блоков 10 и 6 элементов ИЛИ, с выходов которых одинаковые результаты сложения и умножения двух десятичных цифр а унитарном коде поступают соответственно на информационные входы элементов ИЛИ Зб40 и 28-35 шифратора 11 результата. Устройство работает в двух режимах: сложения и умножения. В режиме сложения на управляющий вход шифратора 11 результата поступа ет нулевой сигн, который подается на один из входов каждого элемента в линейке элементов ИЛИ , форми рующих цифры суммы, не внося никаких изменений в режимных работах. Одновременно этот же сигнал подается на выходные элементы И 2-, перекрывая выходные цепи трех старших цифр результата, не нужных в режиме сложе ния После инвертирования на элементе НЕ Ц отрицание этого сигнала поступает на один.,из входов каждого элемента в линейке элементов ИЛИ 313135, формирующих пять младших цифр произведения. В результате этого на выходе этих элементов ИЛИ порождаются единичные сигналы, что равносильно прерыванию выходных цепей пяти младших цифр произведения. .Единичные сигналы поступают на входы выходных элементов И , на другие входы которых поступают цифры суммы с элементов ИЛИ . Таким образом, пятиразрядная сумма (двоичная тетрада и сигнал переноса в следующую Тетраду) будет выдана с линейки выходных элементов И 29 на соответствующие информационные входы приемника результата. В умножения на упр.авляющий вход шифратора 11 результата подается единичный сигна), который, поступая на один из входов каждого элемента в линейке элементов ИЛИ . фактически прерывает их работу, порождая на их выходах единичные си|- налы. Одновременно этот же сигнал подается на выходные элементы И 4244, подготавливая их к приему и выдаче трех старших цифр произведения с элементов ИЛИ 28-30. Единичные сигналы с элементов ИЛИ 36-40 поступают на входы выходных элементов 45-49, подготавливая их к приему и выдаче пяти младших цифр произведения с элементов ИЛИ 31-35. Таким образом, восьмиразрядное произведение (две двоичные тетрады) будет выдано с линейки выходных элементов И 42-49 на выходы устройства, а с них - на соответствующие информационные входы приемника результата. Эффективность предлагаемого вычислительного устройства по сравнению с известными заключается в расширении функциональных возможностей путем выполнения операции суммирования десятичных цифр и цифры вход-, ноге переноса, что позволяет строить на его .основе многоразрядные десятичные арифметимеские устройства, обладающие более высоким быстродействием и требующие меньших аппаратурных затрат для реализации.

f fTpt/cffHt/Mi/ pe3t/jf6/rra/rfa

фиг.1

Фиг.2.

г/ х

8Л

Xgvx;

(

y,J(fflff37)

-Ч:(а38)

-J ffiaJd)

J infff/ff ff)

W( j

(на38

) J(w )

Авторы

Даты

1983-03-30—Публикация

1980-11-10—Подача