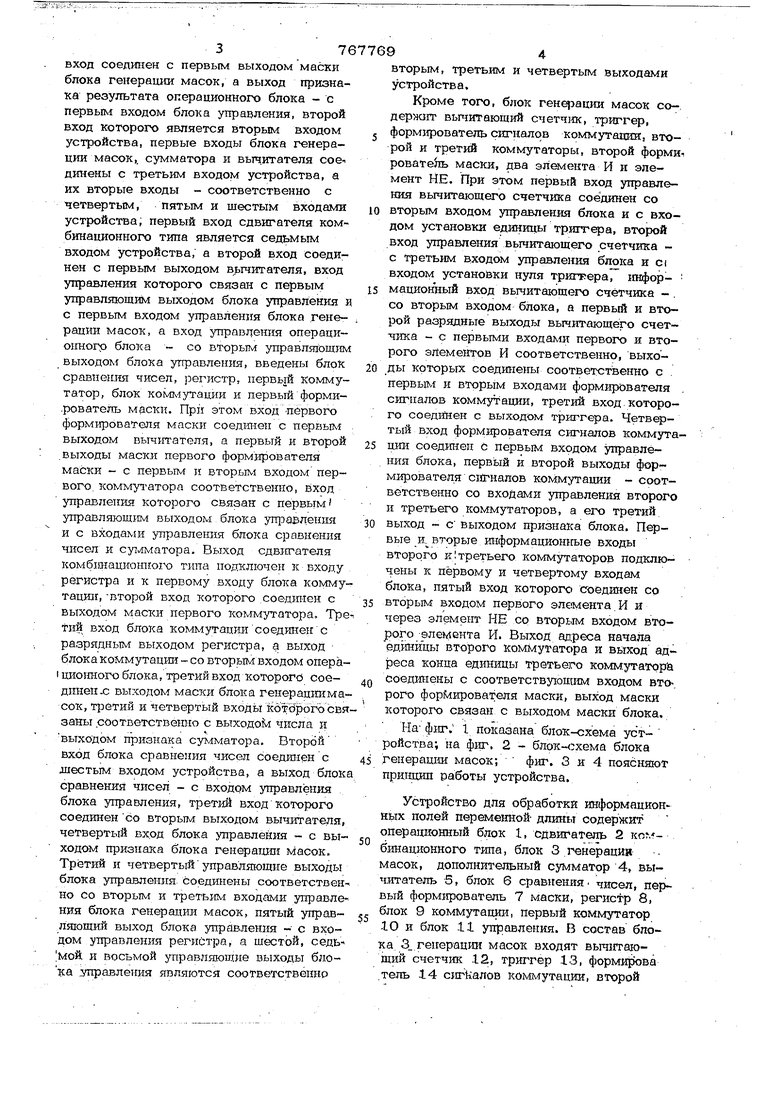

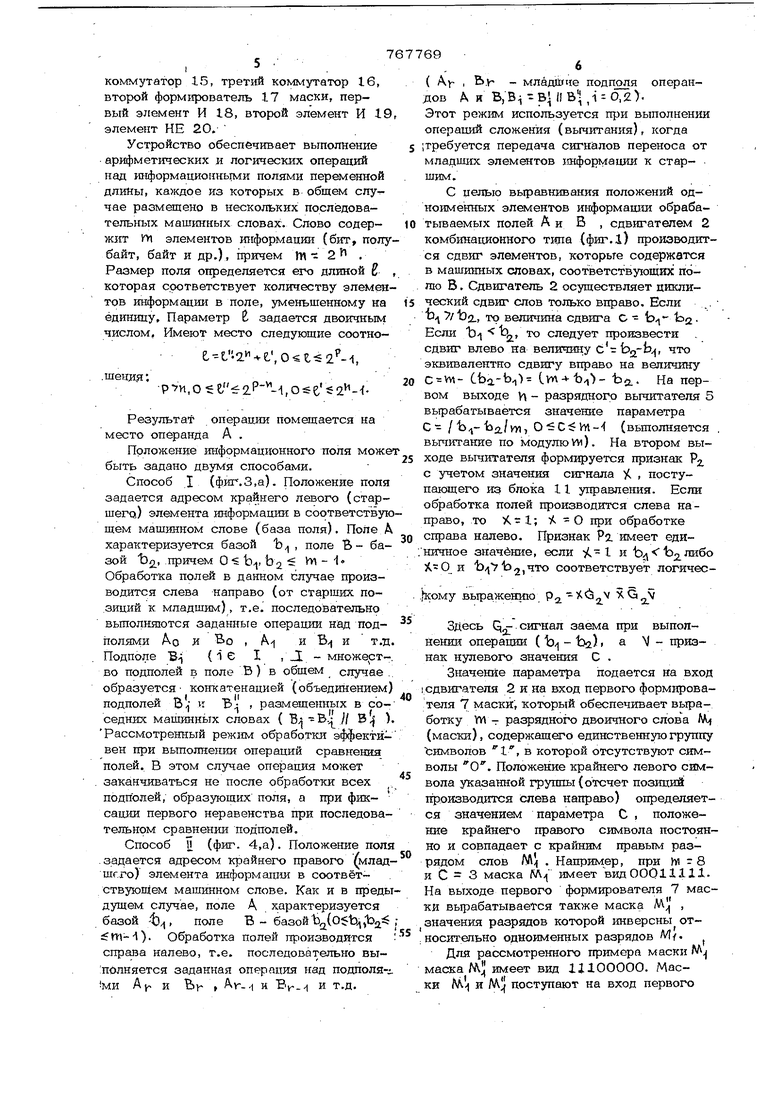

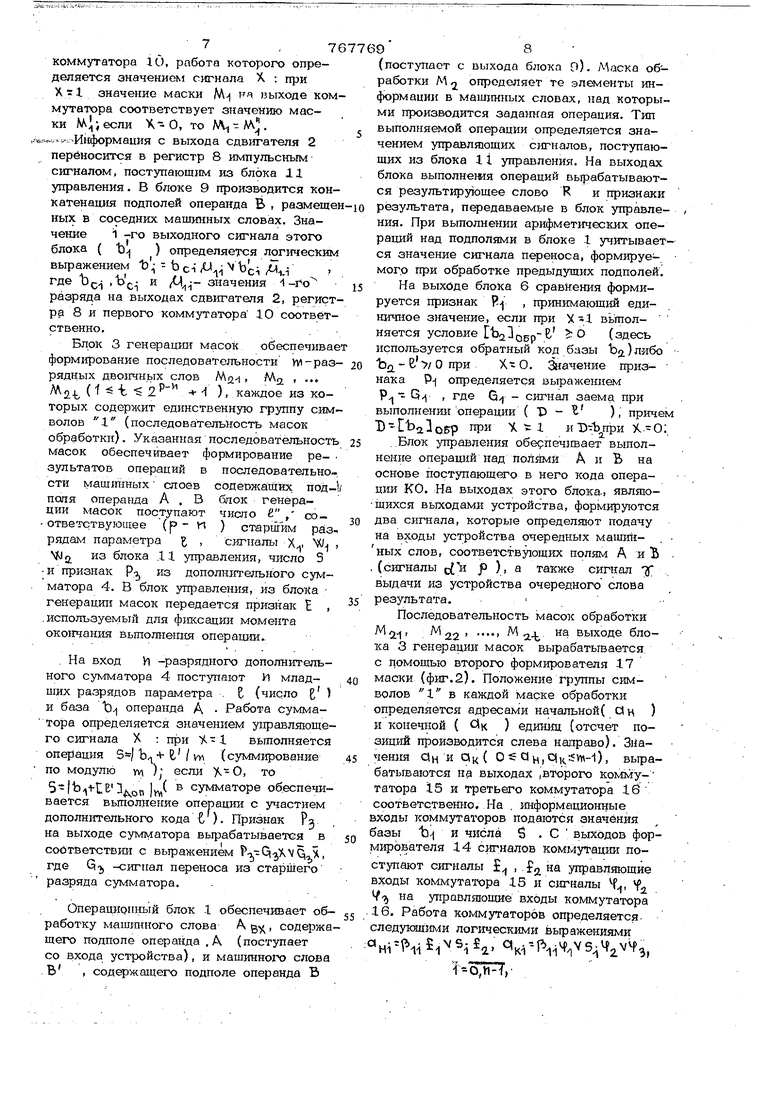

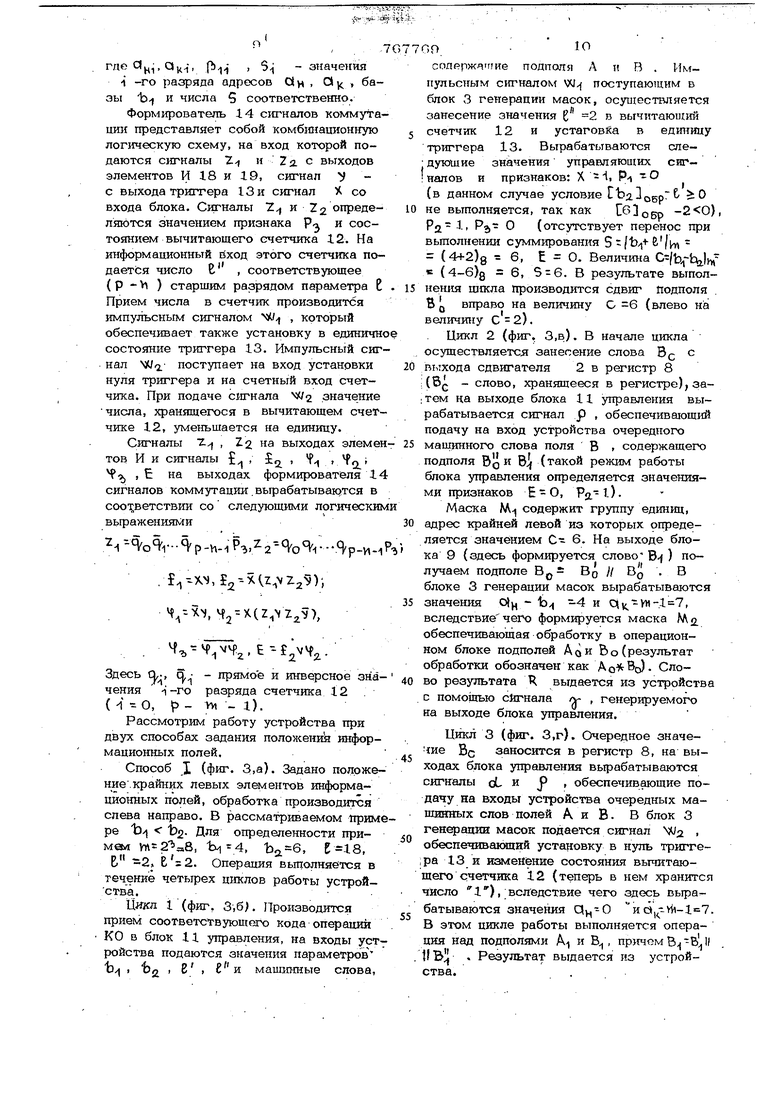

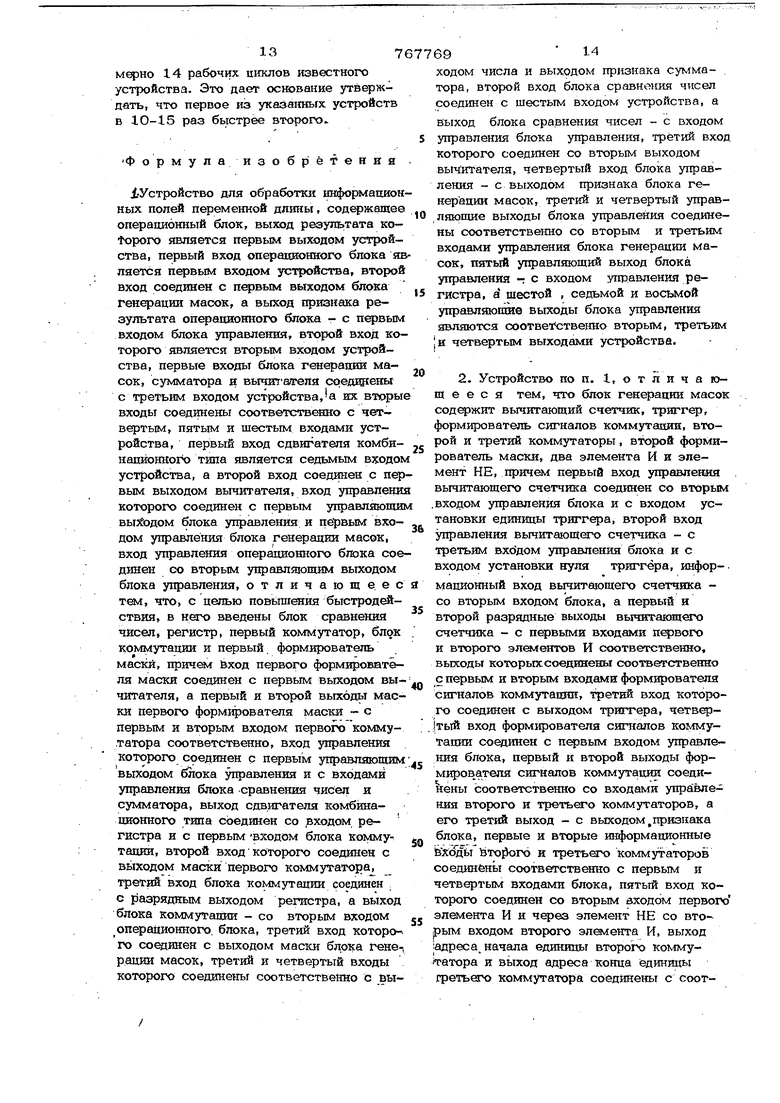

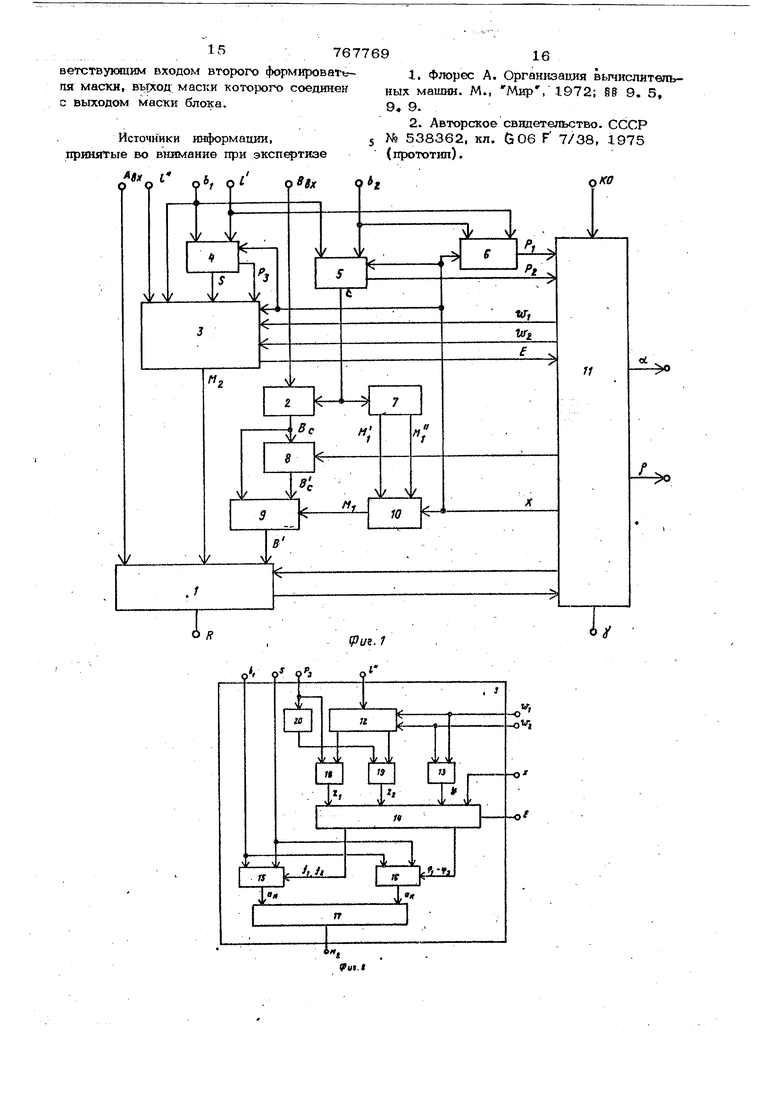

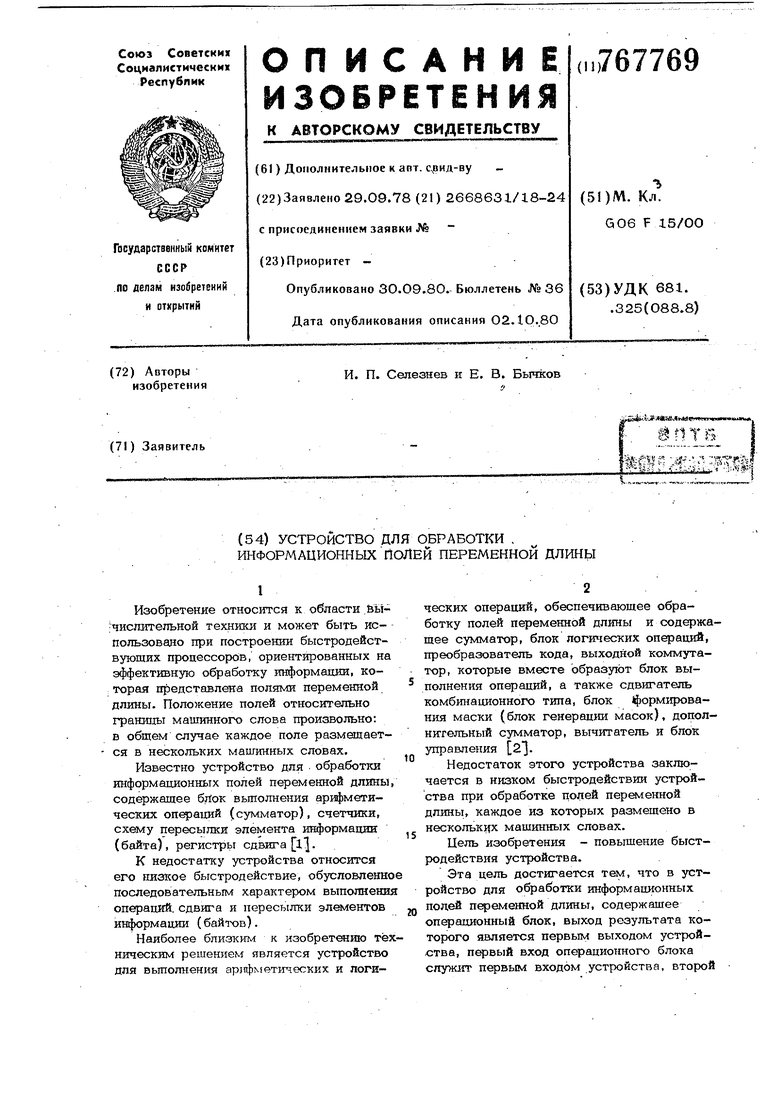

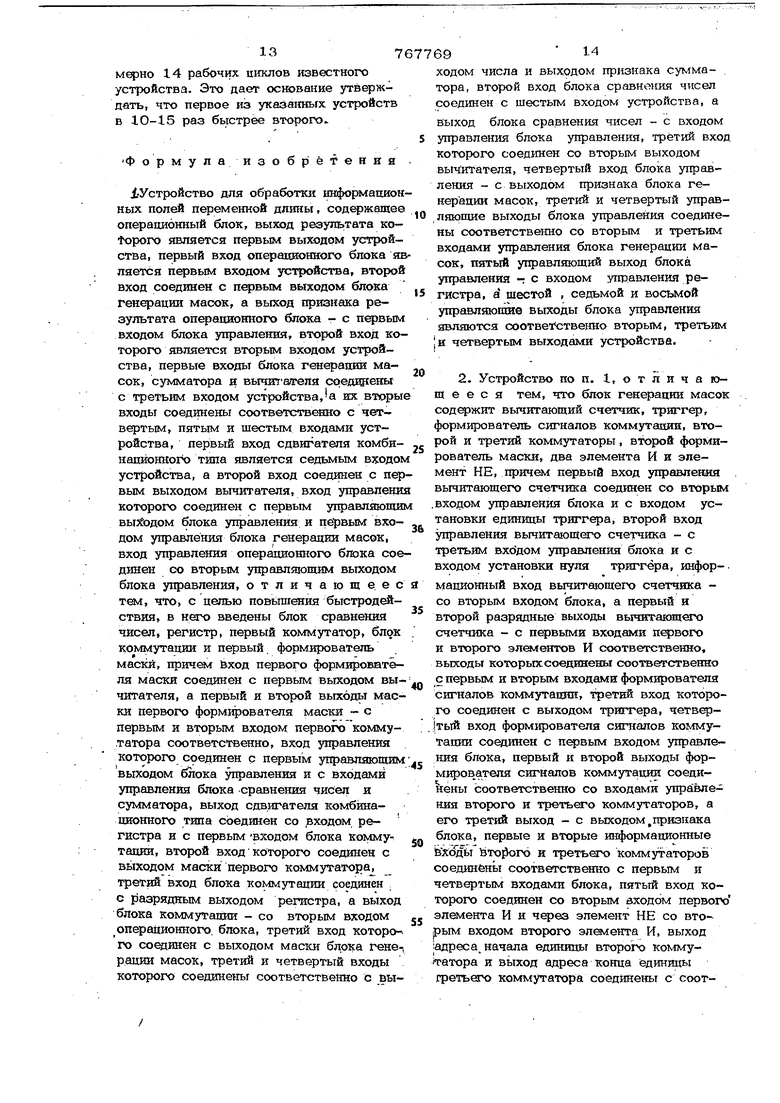

(54) УСТРОЙСТВО ДЛЯ ОБРАБОТКИ . ИНФОРМАЦИОННЫХ ПОЛЕЙ ПЕРЕМЕННОЙ ДЛИНЫ Изобретение относится к области.&ычиспитепьной техники и может быть использовано при построении быстродействующих процессоров, ориентированных на эффективную обработку ииформашш, ко: торая представлена полями переменной длиньг. Положение полей относительно границы машинного слова произвольно: в общем случае каждое поле размещается в нескольких машинных словах. Известно устройство для обработки информационных полей переменной длины содержащее бп:ок выполнения арифметических операций (сумматор), счетчики, схему пересылки элемента информации (байта), регистры сдвига l. К недостатку устройства относится его низкое быстродействие, обусловленно последовательным характером выполнени операций, сдвига и пересылки элементов информации (байтов). Наиболее близк1-гм к изобретению те ническим решением является устройство для Выполнения арш зметических и логических операций, обеспечивающее обработку полей переменной длины и содержащее сумматор, блок логических операций, преобразователь кода, выходной коммутатор, которые вместе образуют блок выполнения операций, а также сдвигатель комбинационногхэ типа, блок формирования маски (блок генерации масок), дополнигельный сумматор, вычитатель и блок управления 2. Недостаток этого устройства заключается в низком быстродействии устройства при обработке полей переменной длины, каждое из которых размещено в нескольких машинных словах. Цель изобретения - повышение быстродействия устройства. Эта цель достигается тем, что в устройство для обработки информационных полей переменной длины, содержащее операционный блок, выход результата которого является первым выходом устройства, первый вход операционного блока служит первым входом устройства, второй вход соединен с первым выходом маски блока генерашш масок, а выход признака результата операционного блока - с первьм входом блока управления, второй вход которого является вторьы входом устройства, первые входы блока генерации масок,, сумматора и вычитателя соединены с третьим входом устройства, а их вторые входы - соответственно с четвертым, пятым и шестым входами устройства; первый вход сдвигателя комбинационного типа является седьмым входом устройства, а В1чэрой вход соединен с первым выходом в гчитателя, вход управления которого связан с первым управляющем выходом блока управления и с первым входом управления блока генерации масок, а вход управления операционного блока - со вторым управлшЪщим выходом блока управления, введены блок cpaBneuiffl чисел, регистр, первь|й коммутатор, блок коммутации и первый форми.рователь мастш. При этом вход nepBoi } формирователя маски соедтшен с первым выходом вычт этеля, а первый и второй .выходы маски первого форм грователя маски - с nepsbnvt и вторым входом первого, коммутатора соответственно, вход управления которого связан с первым управляющем выходом- блока уп эавления и с входами управления блока сравнения чисел и cyi Maropa. Выход сдвга ателя комбнд ацнонно) типа подключен к входу регистра и к первому входу блотса комму тацшг,-второй вход которого .соединен с выходом маски первого коммутатора. Тр Тий вход блотса коммутациисоединен с разрядным выходом регистра, а выход блока коммутац ш - со вторьш входом опера I цио1шого блока, третий вход которого соединен-с выходом маски блока генеращшма сок, третий и четвертый входы котйрогосвя заны соответственно с выходов числа и выходом призна)ка сут лматора. Второй вход блока сравнения чисел соединен с шестым входом устройства, а выход блок сравнения чисел - с входом управления блока управления, третий вход которого соединен со вторым выходом вычитате.ля четвертый вх.од блока управления - с вы ходом признака блока генерашш масок, Третий и четвертый управлзтющие выходы блока управления соединены соответствен но со вторым и TpeTbKvi входами ущэавле НИН блока генерации масок, пятый управляющий выход блока управления - с входом управления регистра, а шестой, седЬ |мой и восьмой управляющие выходы блока :управления являются соответственно вторым, третьим и четвертым выходами устройства. Кроме того, блок гене}эацки масок содеряагг вычитающий счетчик, триггер, форм1фователь сигналов коммутации, второй и третий коммутаторы, второй форми. роватейь мас1ш, два элемента И и элемент НЕ. При этом первый вход управления вычитающего счетчмка соединен со вторым входом управления блока и с входом установки единицы триггера, второй вход управления вычитающего счетчика с третьим входом управления блока и ci входом установки нуля триггера, 1шфор- мационный вход вычитающего счётчика -. со вторьщ входом блока, а первый и второй разрядные выходы вычитающего счетчика - с первыми входами первого и второго элементов И соответственно, выходы которых соединены соответственно с . первым и вторым входами формирователя ст: налов коммутации, третий вход.которого соедшек с выходом триггера. Четвертый вход формирователя сигналов коммутации с первым входом управления блока, первый и второй выходы формирователя с налов коммутации - соответственно со входами управления второго и третьего коммутаторов, а его третий выход С выходом признака блока. Первые и. вторые информационные входы второго и I третьего коммутаторов подключены к первому и четвертому входам блока, пятый вход которого соедшен со вторым входом первого элемента.И и через элемент НЕ со вторым входом второго -рлемекта И. Выход адреса начала едшйцы второго коммутатора и выход адреса конца единицы третьего коммутатора соед1-гаены с соответствующим входом вто-, рого фopf иpoвaтeля маски, выход маски которого связан с выходом маски блока, На фиг. 1 показана блок-схема устройства; на фиг. 2 - блок-схема блока генерации масок; фиг. 3 и 4 поясняют пршщип работы устройства. Уст{зойство для обработки информационных полей переменной- длины содержит операционный блок 1, сдвигатель 2 ког.бинационного типа, блок 3 I Hepamw масок, дополнительный сумматор 4, выч.йтатель 5, блок 6 сравнения чисел, первый форм1фователь 7 маски, регистр 8, блок 9 коммутации, первый коммутатор -10 и блок -11 управления. В состав блока 3 генерации масок входят вычитающий счетчик 12, триггер 13, формирова .тель 14 сигналов коммутации, второй коммутатор 15, третий коммутатор 16, второй формирователь 17 маски, первый элемент И 18, второй элемент И 19 элемент НЕ 20. Устройство обеспечивает выполнение арифметических и логических операций над информационнь1ми полями переменной длины, каждое из которых в общем слу чае размещено в нескольких последовательных машинных словах. Слово содержит 1 элементов информации (бит, полу байт, байт и др.), причем Щ : 2 . Размер поля определяется его длиной 2 которая соответствует количеству элемен тов информации в поле, уменьшенному на единицу. Параметр t задается двоичным числом. Имеют место следующие соотноt-L.,,, .шенкя; ,,,(Результат операции помещается на место операнда А . Положение информационного поля може быть задано двумя способами. Способ I (фиг.3,а). Положение поля задается адресом крайнего левогю (старшего) элемента информации в соответствую щем машинном слове (база поля). Поле А характеризуется базой Ъ , поле В - базой Ъ, причем О b-j, b2 - ( - I Обработка полей в данном случае производится слева направо (от старших позиций к младшим), т.е. последовательно выполняются заданные операции над подполями Ло л ВО , А-1 и В и т.д Подполе B-i ( i е I , -1 - множертво подполей в поле Б) в общем случае, образуется конкатенацией (объединением подполей и В , размещенных в соседшсс машинных словах ( .// ) Рассмотренный режим обработки эффектйвен при выполнении операций сравнения полей. В этом случае операция может . заканчиваться не после обработки всех подполей, образующих поля, а при фиксации первого неравенства при последовательном сравнении подполей. Способ Ц (фиг. 4,а). Положение поля .задается адресом крайнего правого (млад шг..го) элемента информации в соответствующем машинном слове. Как и в преды душем случае, поле А характеризуется базой -t) , поле В базойЬ2(,,. Обработка полей производится справа налево, т.е. последоватепьно выпОлняется заданная операция над. подполями AJ- и Ьу- , А,г-.1 и BV-. и т.д. ( Лу- , b.V - мла/ииче подполя операндов Д и Б,В -В |1В,1 0,2. Этот режим используется при выполнении операций сложения (вычитания), когда ;требуется передача сигналов переноса от младших элементов 1шформации к стар- шим. с целью вьфавнивакия положений одноименных элементов информашш обрабатываемых полей А и Б , сдвигателем 2 комбинационного типа (фиг.1) производится сдвиг элементов, которые содержатся в машинных словах, соответствующих поnio В, Сдвигатель 2 осуществляет цикли- ческий сдвиг слов только вправо. Если Ь / Ъг. то величина сдвига С - be Если Ъ-t tij,, то следует произвести . сдвиг влево на величину , что эквивалентно сдвигу вправо на величину C vvi- Cfoi-b ) (. b-x- На первом выходе у - разрядного вьгчитателя 5 вьфабатывается значение параметра С - ./уу1, OSC Wl-f (вьшолняется . вьшитание по модулю Wi). На втором выходе вычитателя формируется признак Р с учетом значения сигнала )(. , поступающего из блока 11 управления. Если обработка полей производится слева направо, то К-1; /- - О при обработке справа налево. Признак Ро. имеет единячное значение, если и и ,4To соответствует логичес кому выражению xG,.,v Здесь сигнал заема при выполнении операции ( Ъ - bj), а М - признак нулевого значения С . Значение параметра подается на вход I сдвигателя 2 и на вход первого формирователя 7 маски, который обеспечивает вьфаботку YM - разрядного двоичного слова M (маски), содержащего единственную группу Ъимволов 1, в которой отсутствуют символы О. Положение крайнего левого символа указанной группы (отсчет позиций п:роизводится слева направо) определяется значением параметра С , положение крайнего правого символа постоянно и совпадает с крайним правым разрядом слов Mil . Например, при W - 8 и С 3 маска имеет вид0001 l.t 11. На выходе первого формирователя 7 маски вьфабатывается также маска М , значения разрядов которой инверсны относитепьно одноименных разрядов М Для рассмотренного примера маски (vv маска ГЛд имеет вид 1J100000. Мае Iti ки М и М поступают на вход первого

коммутатора 1U, работа которого определяется значением сигнала X. ; при Xrl значение маски M-i )зыходе коммутатора соответствует значению маски М ;еспи Ч О, то Л, - М . ,i,,-Информация с выхода сдвигателя 2 переносится в регистр 8 импульсным сигналом, поступающим из блока 11 управления. В блоке 9 производится конкатенация подполей операнда В , размещен-1 о ных в соседних машинных словах. Значение i -го выходного сигнала этого блока ( Ь ) определяется логическш выражением - Ь c-i Vbci Д.1 где значения -1-Го 15

разряда на выходах сдвигателя 2, регистра 8 и первого коммутатора 10 соответственно,.

Блок 3 генерашш масок обеспечивает форм1фование последовательности ш-раз- 20 рядных двоичных слов MU Mji , ... M Cf tSl - i ), каждое из которых содержит единственную группу сим волов 1 (последовательность масок обработки). Указанная последовательность 25 масок обеспечивает формирование ре- . зультатов операций в последовательности маштных слоев содержащих поля операнда А . В блок генерации масок поступают число , соответетвугощее Чр ) старшим раз, параметра I , С1 гналь Х, У ,

VJQ, из блока .11 управления, число 3

и признак Рэ, из дополнительного сумматора 4. В блок управления, из блока генерации масок передается признатс Н , .

.используемый для фиксации момента око}гчания выполнения операции..

. На вход V) -разрядного дополнительного сумматора 4 поступают И млад- 40 ишх разрядов параметра . t (число ) и база Ъ операнда А Работа сумматора определяется значением управляющего сигнала X : при A-l выполняется операция . /1 (суммирование 45

по модулю щ ) если v-0, то

5-|b ti:B3 on |уу( сумматоре обеспечивается выполнение операции с участием дополнительного кода & ). Признак РЗ на выходе сумматора вырабатывается в 50 соответствии с вьфажением Гг-G|2l Q- где QT, -сигнал переноса из старшего

разряда сумматора.

Операционный блок 1 обеспечивает об- jj работку маш1шного слова А g , содержащего подполе операнда .А (поступает со входа устройства), и машинно1х слова .Б , содержащего подполе операнда В

(поступает с выхода блока D). /Маска обработки А / определяет те элементы информации в машзганых словах, над которыми производится заданная операция. Тип выполняемой операции определяется значением управлшоЩих сигналов, поступающих из блока 11 управления. На выходах блока выполнешя операций вырабатываются результиру1ощее слово R и признаки результата, передаваемые в блок управления. При выполнении арифметических операций над подполями в блоке 1 учитывается значение сигнала переноса, формируеМОГ.О при обработке предыдущих подполей.

На выходе блока 6 сравнения формируется признак Р , прннкмающзй единичное значение, если при X 1 вьтолняется условие Ъ ЗоБр-Е (здесь используется обратный код базы Ь2.)пибо Ъд - при . Экачение признака Р-1 определяется выражением р 1 Q , где G/) - сигнал заема при выполнении операции ( 13 - ), приче

1)ЕЬ, при -1 и1)-ъ,при х-о

. .Блок управления обе(рпеч1тает выполнение операций над полями Д и Ь на основе поступающего в него кода операции КО. На выходах этого блока, явлшощихся выходами устройства, формируются два сигнала, которые определяют подачу на входы устройства очередных машш- . ных слов, соотвеаствующих полям А иЪ , (сигналы Я ), а также сигнал -у выдачи из устройства очередного слова результата. -

Последовательность масо7с обработки М, . М 22 a-t выходе блока 3 генерации масок вьфабатывается с цомощыо второго формирователя 17 маски (фиг.2). Положение группы символов 1 в каждой маске обработки определяется адресами начальной( с(н ) и конечной ( OK ) едишо (отсчет позиций производится слева направо). Зйачения Он и QK ( OS а и, ), вьфабатываются на выходах |ВТорого коммутатора 15 и третьего коммутатора 16 соответственно. На , информационные входы коммутаторов подаются значения базы b-i и числа S . С выходов форм1фЬБателя 14 сигналов коммутации поступают сигналы й управляющие входы коммутатора 15 и сигналы Ч, У,, - на управляющие входы коммутатора -16. Работа коммутаторов определяется, следующими логическими вьфажениями .,,q ;j--fb 4,,

laHIM

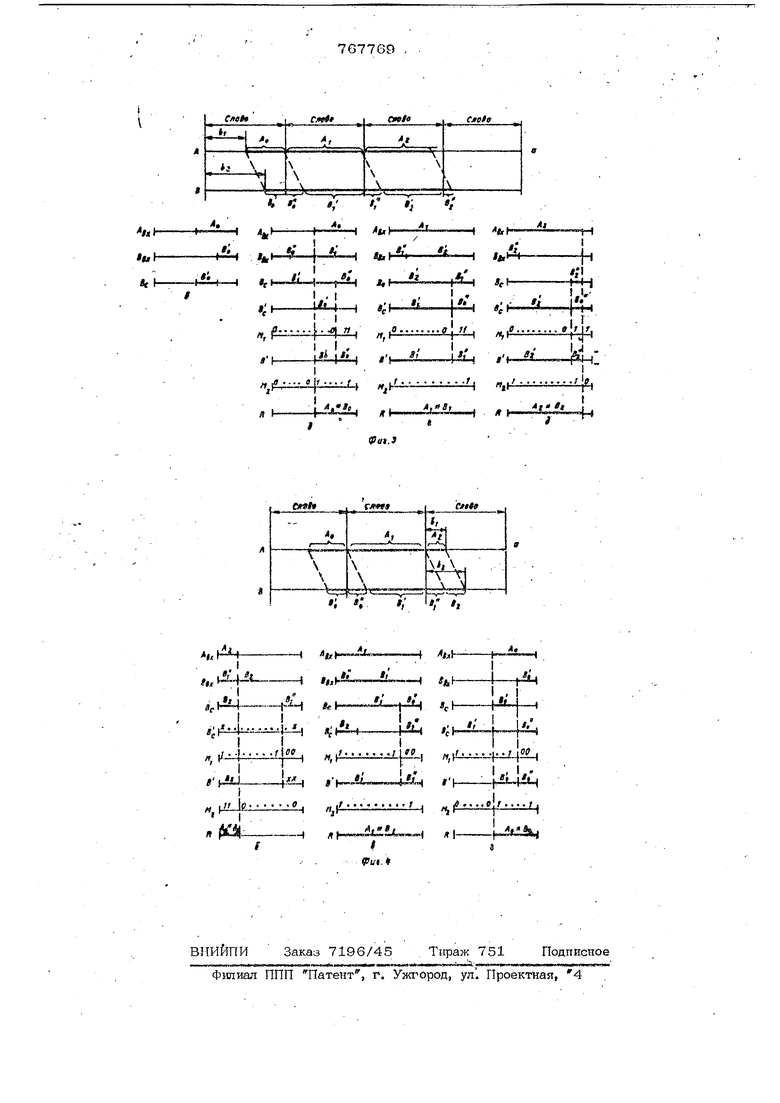

, где С(, , Р)- , S - значения i -го разряда адресов 01 м , Q ц , базы Ъ и числа 5 соответственно. Формирователь 14 сигналов коммута ции представляет собой комбшшционную логическую схему, на вход которой подаются сигналы Z-I и Za с выходов элементов И 18 и 19, сигнал V с выхода триггера 13 и сигнал со входа блока. Сигналы 1 к 22°Щ пеЛ5п6тся значением признака Р и состоянием вычитающего счетчика 12. На информационный йход этого счетчика подается число Е , соответствующее (Р -V ) старщим разрядом параметра 6 Прием числа в счетчик производится импульсным сигналом У , который обеспечивает также установку в единичн состояние триггера 13. Импульсный сиг нал NjVi- поступает на вход установки нуля триггера и на счетный вход счетчика. При подаче сигнала с/2 значение числа, хранящегося в вычитающем счет чике 12, уменьщается на единицу. Сигналы Z. , Z2 на выходах элеме тов И и сигналы , Q , , , Е на выходах формирователя 14 сигналов коммутации.вырабатыва1ртся в соо1 ;ветствии со следующими логически вьфажения ли 7 -а, о/ 557-плп Л -M o ir-Mp-h-iP.2-%Sr-.Sp-MH . , , 42-- CZ,NZ,,g), ь--... Здесь С. - прямое и инверсное зна чения -i-ro разряда счетчика 12 ( -1 - О, р- Wt - 1). Рассмотрим работу устройства при двух способах задания полохсениЬ информационных полей. Способ X (фиг. 3,а). Задано полржение.крайних левых элементов информационных полей, обработка производится слева направо. В рассматриваемом 1фим ре ID/I Для определенности примел Ут 2Ьа8, , , , Е -2, Е 2. Операция выполняется в течение четырех циклов работы устройства. Цикл 1 (фиг, 3,6). Производится прием соответствующего кода операций КО в блок 11 управления, на входы уст ройства подаются значения параметров мащинные слова. 0.1 сплрржчпие подполя Л п В . Импульсным С1п налом W поступающим в блок 3 генерации масок, осуществляется занесение значения 2 в вычитающий счетчик 12 и устаговка в едштицу триггера 13. Вырабатываются следуюшие зн1эчения управляющих сягналов и признаков: X PI -О (в данном случае условие не выполняется, так как СбЗовр ), Ра Ра- О (отсутствует перенос при выполнении суммирования S 6/hi (4+2)3 б, Е О. Величшш C-fh,-hj.lh,(4-6)g 6, S 6. В результате выполнения цикла производится сдвиг Подполя В Q вправо на величину С 6 (влево н величину С 2). Цикл 2 (фиг. 3,в). В начале цикла осуществляется занесение слова BC выхода сдвигателя 2 в регистр 8 {б - слово, хранящееся в регистре), затем на выходе блока 11 управления вырабатывается сигнал р , обеспечивающий подачу на вход устройства очередного мащинного слова поля В , содержащего подполя BQ и Bjf (такой режим работы блока управления определяется значенийми признаков Е О, ). Маска Л. содержит группу единиц, адрес крайней левой из которых рпределяется значением С- 6. На выходе блока 9 (здесь формируется слово В ) получаем подполе BO // BQ . В блоке 3 генерации масок вырабатываются значения о} - Ъ -4 и о(, вследствие чего формируется маска М 2 обеспечивающая обработку в операционном блоке подполей АО и Ьо (результат обработки обозначен как ). Слово результата R выдается из устройства с помощью сигнала fy- , генерируемого на выходе блока управления. Цикл 3 (фиг. 3,г). Очередное значе1ие БС заносится в регистр 8, на выходах блока управления вьфабатываются сигналы oL и р , обеспечивающие подачу на входы устройства очередных мащинных слов полей А и В. В блок 3 генерации масок подается сигнал fJ2 , обеспечивакяций установку в нуль тригге:ра 13 и изменение состояния вычитающего счетчика 12 (теперь в нем хранится число i), вследствие чего здесь вьфабатываются значения С|ц-0 и « ;--«1-1 7. В этом цикле работы выполняется операция над подполями А и В, причем , II . Результат выдается из устройства. Цикл 4 (фиг. 3;д). В начале цикла устройство работает так же, как и в предыдущем случае. При этом вычитающ}й счетчик 12 переходит нулевое сос тояние и в блоке 3 генерации масок выврабатывается значение 7. 1, вследствие чего -Е-1, Он . S 6. Формируется такая маска Mg. при которой осуществляется выполнение операщж над крайними правыми подполями Bj,. Значение призншса Е 1, поступающее в блок управления обусловливает око5гча ние вь1полнения операш и. В частном случае, когда каждое из полей. А и В размещено тользсо в одном машинном слове ( р 1, Е J.), операция вьгаолняэтся в течение одного цикла. Если поле А размэяено в одном машшпюм слове ( Е 1), а , - в двухсловах ( р. О), требуется два цикла работы (во втором штеле пр1П1т ается второе машинное слово поля В и выполняется операция). . U.. способ (ф11Г. 4,а). Задано положе ние крайних правых элементов i-шформапионных полей А и В , обработка производится справа налево. Для рассматриваемого примера Ъ-} bg определейности примем: m 2 - 8, , , е 1.3, Е 1, . Для выполнения операции требуется три рабо чих цшша устройства.. Пшш J. (фиг. 4,6. Производш ся прием соответствующего к;ода операций КО в блок 11 управления, на входы устройства подаются значения Ъ, Ъ, 8, Ь и машинные слова, содержатлне под поля АО. и BV, Su Сигнал.ом NJV производятся занесение значения б 1 в счетчик 12 и установка в ед1шйчное , состояние триггера 3.3. Вьфабатываются след аощие значешга управляющих слгнаX 0, Р.1-О (уело лов и признаков: вие Ъ -../О в данном примере не ...„ „ выполняется, так как 3-5 О), , Р I (отсутствует сигнал переноса при выполнении операции 5 -lb - Le3 otilhi .-|( 1+3)1 g. 4),Е - О../ Величина ( 1-3). - 6, вследствие чего подполя и 82 сдви /гаются вправо на величину С 6, (влево на велич1 ну с -2). Состояние регистра 8 (слово BC ) не определено, что ук:азывается сил-шолами X ..Маска N. на выходе первого коммутатора 10 инверсн по отношению к маске Nv| , адрес край ней левой едшгицы котврой определяется значением с 6. На выходе бло7са 9 (слово Б ) получим подполе В В блоке 3 ге герацш1 масок вырабатываются (значения - О и ,- 1, вследствие чего формируется кшска М,;, обеспечивающая обработку в операциотгом блоке 1 подполен Вд . Резул1зтат выдается из устройства. иикл 2 (фиг. 4,в). В начале цикла осуществляется занесение слова В. с выхода сдвигателя 2 в регистр 8, затем на выходах блока 11 управления выраба-т тываются сигналы cL и р , обеспечивающие подачу на входы устройства очередных машинных слов полей А и В , В блок генерации масок подается сигнал обеспечивающий установку в нуль триггера 13 и изменение состояния вычитающего, счетчика 12 (он переходит в нулевое состояние), вследствие чего здесь форм1фу1отсязначения С|ц- О и С| Упг-1-5: -7. В этом шпше работы выполняется операция над подполями B-j причем Ь . В If Б ; Результат выдается из -устройства. Цикл 3 (фиг. 4,г). В начале цикла устройство работает так же, как ив-. предыд тдем случае. При этом все разряды вьгчитающегб счетчика 12 перехо- . дят в ед1шичное состояние и в блоке 3 генерации масок: вырабатывается значение 2 1 вследствие чего QH 5 -4 и Dl, Ул-1 - 7. Формируется такая маска ЛДд, при-которой осуществляется выполнение операции над крайними левымвс подполями До .и. о Значение признака , и ; устройство завершает выполнение операции, . -. Основные этапы работы известного устройства;. производится пересылка подполя В в специально выделенную ячейку памяти К, длячего форм1фуются значения- парамет-. ров Ъ- , Ъу , t (на это затрачивается 3 рабочих цикла устройства) и вьтолняется операция пересышш (1 рабочий: никл); . -, .пересылается в ячейку К ° аналогии с предыдущей операцией, на это затрачивается 4 шпсла); формируется результат операции R A-j S-f , для Чего вычисляются зна чешта Ъ, bj и выполняется операция над содержш ым ячейки К и операндом (на все затрачивается 4. рабочих ци1ота); -. . формируется и анализируется признак окончания операции над (на это затрачивается 2 цкгша). Такил образом, одному типовому циклу данно1Х) устройства соответствует примерно 14 рабочих циклов известного устройства. Это дает основание утверждать, что первое из указанных устройств Б Ю-15 раз быстрее второго Формулаизобрёгення 1,-Устройство для обработки информацион ных полей переменной длины, содержащее операционный блок, выход результата ко- toporo $юляется первым выходом устройства, первый вход операционного блока яв ляется первым входом устройства, второй вход соединен с первым выходом блока генерации масок, а выход признака результата операционного блока - с первым входом блока управления, второй вход которого является вторым входом устройства, первые входы блока генераиии масок, сумматора и вьпштэгеля соедцрены с третьим входом устройства,а их вторы входы соединены соответственно с четвертым, пятым и шестым входами устройства, первый вход сдвигателя комбинационного типа является седьмым входом устройства, а второй вход соединен с пер вым выходом вычитателя, вход управлени которого соединен с первым управляющи блока управления и первьвл входом управления блока генерации масок, вход управления операционного блока сое динен со вторым управляющим выходом блока управления, о т л и ч а ю щ е е с тем, что, с целью повышения быстродействия, в него введены блок сравнения чисел, регистр, первый коммутатор, блок коммутации и первый, формирователь маски, причета йход первого формировнтёля маски соединен с первым выходом , читателя, а первый и второй выходьт маски первого форм1фователя маски с первьш и вторым входом первого коммутатора соответственно, вход управления которого соединен с первым управляющим выходом блока управления и с входами управления блока сравнеьшя чисел и сумматора, выход сдвигателя комбинационного типа соединен со входом регистра и с первым -входом блока коммутацки, второй вход которого соединен с выходом маски первого коммутатора, третий вход блока коммутации соединен с 1)азрядным выходом регистра, а выход блока коммутации - со вторым входом операционного, блока, третий вход которо- го соединен с выходом маски блока генерации масок, третий и четвертый входы KOTopoiX) соединены соответственно с вы769 1-4 ходом числа и выходом признака сумматора, второй вход блока сравнения чисел соединен с шестым входом устройства, а выход блока сравнения чисел - с входом управления блока управления, третий вход которого соединен со вторым выходом вы итателя, четвертый вход блока управления - с выходом признака блока генерации масок, третий и четвертый управляющие выходы блока управления соединены соответственно со вторым и третьим входами управления блока генерации масок, пятый управляющий выход блока управления - с входом управления регистра, а шестой , седьмой и восьмой управляюпше выходы блока управления являются соответственно вторым, третьим и четвертым выходами устройства. 2. Устройство по п, I, о т л и ч а ющ е е с я тем, что блок генерации масок вычитающий счетчик, триггер, формирователь сигналов коммутаоии, втоР - третий коммутаторы, второй формирователь маски, два элемента И и элемент НЕ, причем первый вход управления вычитающего счетчика соединен со вторым входом управления блока и с входом установки единицы триггера, второй вход управления вычитающего счетчика - с третьим вхйдом управления блока и с входом установки нуля триггера, инфор,1 мационный вход вьгчитающего счетчика со вторым входом блока, а первый и второй разрядные выходы вычитающего счетчика - с первыми входами нового и второго элементов И соответственно, выходы которых соединвЕсы соответственно с первым и вторым входами формирователя :....V. сигналов коммутации, третий вход которого соединен с выходом триггера, четвер тый вход формирователя сигналов коммутации соединен с первым входом управле блока, первый и второй выходы формировдтеля сигналов коммутации соединены соответственно со входами управления второго и третьего коммутаторов, а его третий выход - с выходом,признака блока, первые и вторые информационные iSxcfeH и третьего коммутаторов соединены соотве гственно с первым и четвертым входами блока, пятый вход которого соединен со вторым входом первого элемента И и через элемент НЕ со вторьш входом второго элемента И, выход |адрес а, начала единицы второго коммуiTaTopa и выход адреса конца 1эдиницы гретьетч коммутатора соединены с соот 76776916

ветствзоощим входом второго формировать-i. флорес А. Организавдя вычислительпя маскн, вьгход маски которого соединен «ых машин. М.. Мир, 1972- 85 95

с выходом маски блока,g gF . i, 8Н W. о,

Источники информашга, 538362, кл. GO6 У 7/38, 1975

принятые во внимание при экспертизе(прототип).

2. Авторское свидетельство. СССР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Устройство для выполнения арифметических и логических операций | 1977 |

|

SU674017A2 |

| Устройство для выбора и переадресации каналов | 1985 |

|

SU1341729A1 |

| Многофункциональное устройство для логической обработки бинарных изображений | 1983 |

|

SU1136179A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для определения длины строки символов | 1980 |

|

SU976438A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Устройство для связи процессора с оперативной памятью | 1978 |

|

SU750489A1 |

Риг. 1

Авторы

Даты

1980-09-30—Публикация

1978-09-29—Подача