1

Изобретение относится к области вычислительной техники.,

По основному авт. св. К 538362 известно устройство для вьшолнения ариф- .метичёских и логических о перйций, содержащее сумматор, блок логических операций, выходной коммутатор, сдвигатель комбинационно)го типа, преобразователькода и блок управления, причем выход выходного коммутатора является выходом устройства, первый вход вьщодного коммутатора соединен с выходом блока логических операций и первым, входом сумматора, а второй - с первым выходом сумматора. Вход преобразователя кода Под.ключен к первому входу устройства, а выход - к второму входу сумматора н первому входу блока логических операций, первый, второй и третий выходы блока управления соединены соответственно с управляющими входами сумматора, блока логических операций и преобразователя кода, четвертый и пятый выходы блока управления соединены с управляющими

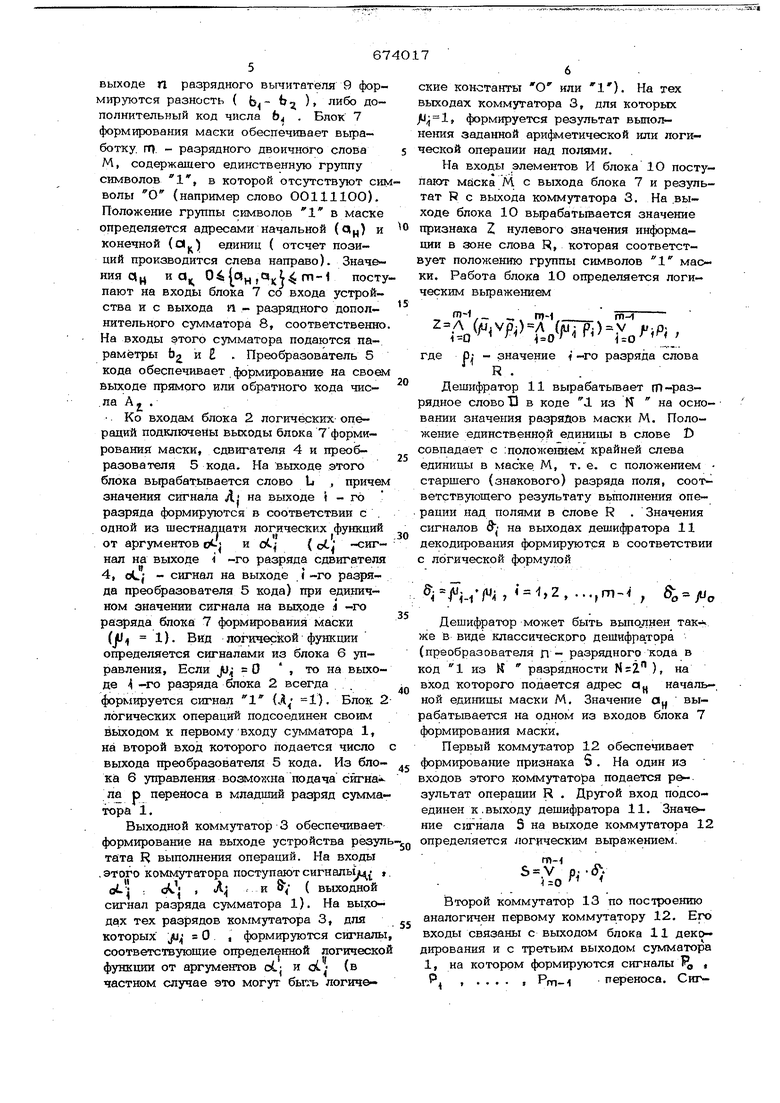

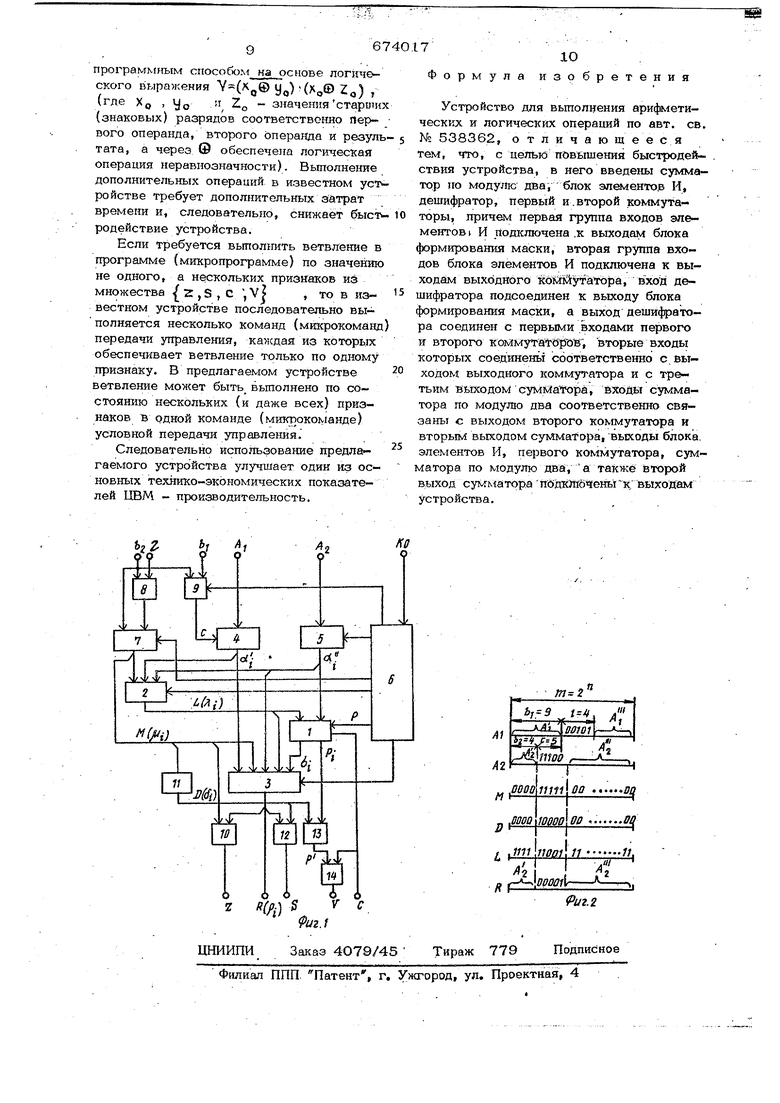

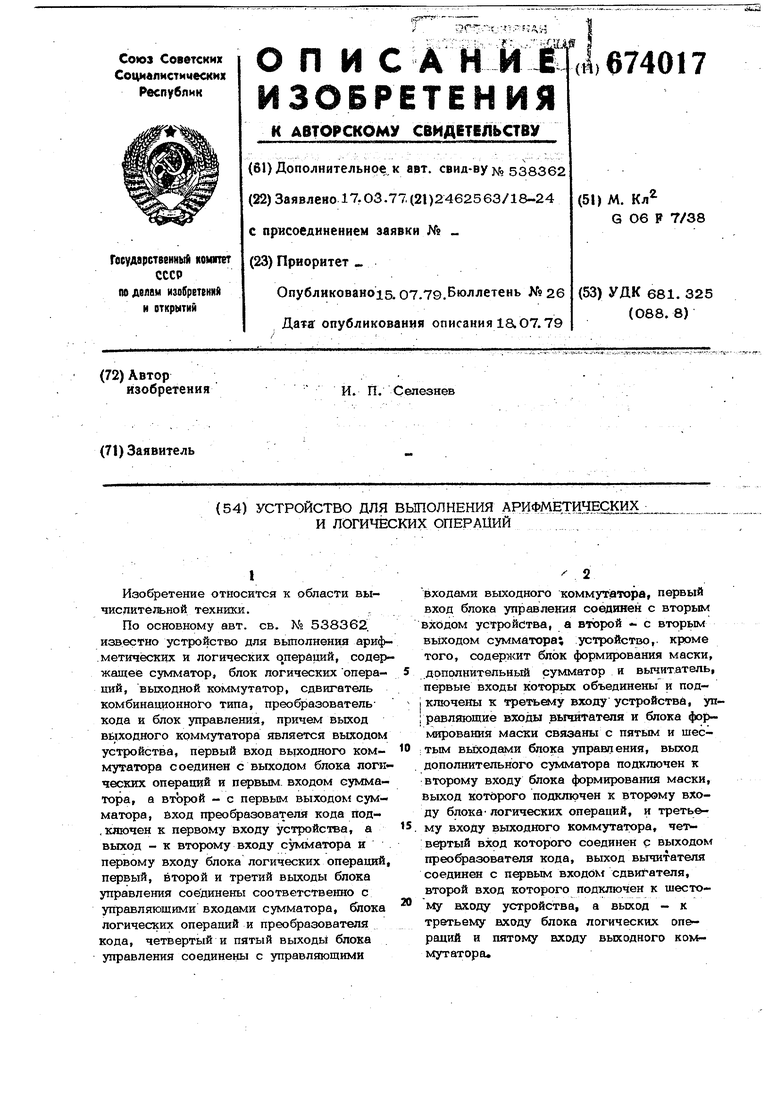

входами выходного коммутатора, первый вход блока управления соединен с вторым входом устройства, а второй - с вторым выходом сумматора; устройство, кроме того, содержит блок формирования маски, .дополнительный сумматор и вычитатель, первые входы которьпс объединены и подключены к третьему входу устройства, уп; равляющие входы вычйтателя и блока формирования маски связаны с пятым и шес;Тым вьгходами блока управления, выход дополнительного сумматора подключен к второму входу блока формирования маски, выход которого подключен к второму входу блока-логических операций, и треть&му входу выходного коммутатора, четвертый вход которого соединен с выходом преобразователя кода, выход вычйтателя соединен с первым входом сдвигателя, второй вход которого подключен к шестому входу устройства, а выход - к третьему входу блока логических операций и пятому входу выходного коммутатора. ; В известном устройстве вьфабатывается недостаточное количество признаков результата операций над полями. Эти признаки используются для реализации операторов ветвления (операций условной передачи управления) в алгоритмах задач, решаемых ycTjjpftcTBOM обработки информации, в состав которого входит такое устрбйство для выполнения арифметических и логическихопераций. При выполнении операций над числами с форсированной запятой, представленными в дополнительном коде (значение знака числа указывается в старшем разряде), обычно формируются следующие признаки результата: признак S - значе1ше знакового (старшего) рёзультата;признак Z - признак нулевого значения результата (все раз ряды результата имеют нулевое значение); признак С - признак расширения, опре деляемый значением сигнала переноса из старшего разряда при вьшолнени операшта сложения над операциями; признак V - признак переполнения, который принимает единично значение, если при сложе нии чисел имеется перено в знаковйй райряд и oTcy ствует перенос из знаконо ;го разряда (складьгоаются два поло сительных: числа) либо отсутствует перенос в знаковый разряд и имеется перенос из знакового разряда (складьюаются дв отрицательных шсла), Из всех указанных признаков в известном устройстве iannapaTypHO вырабатьшается только признак С (на втором выходе сумматора). Значения остальных признаков могут быть получены на основе этого признака в результате выполнения дополнительных операций в устройстве (реализации доподнительных циклов передачи информации через устройство)-. Это требует дополнительных затрат времени и, следовательно, снижает быстродействие устройства. Целью изобретения является повьшхение быстродействия. ЭтЬ й6стигаёТся тем, что предлагаемое устройство содержит сумматор по модулю два, блок элементов И, дешифратор, первый и второй коммутаторы, причем первая группа входов элементов И подключена к выходам блока формирования маски, торая группа входов блока элементов И подключена к выходам выходного коммутатора, вход дешифратора подсоединен к выходу блока формирования маски, а выход дешифратора соединен с первыми входами первого и второго коммутаторов, вторые входы которых соединены соответственно с выходом выходного коммутатора КС третьим выходом сумматора, вхо- . ды сумматора по модулю два связаны соответственно с выходом второго коммутатора и вторым выходом сумматора, выходы блока элементов И, первогокоммутатора, сумматора по модулю два, второй выход сумматора подключены к выходам устройства. На фиг. 1 изображена схема предлагаемого устройства; фиг. 2 поясняет принцип его работы. Устройство для выполнения ари4метических и логических операций (фиг. 1) содержит сумматор 1, блок логических операций 2, выходной коммутатор 3, сдвигатель комбинационного типа 4, преобразователь кода 5, блок управления 6, блок формирования маски 7, дополнительный- сумматор 8, вычитатель 9, блок элементов И 1О, дешифратор 11, .первый коммутатор 12, второй коммутатор 13,i сумматор по модулю два 14. Устройство обеспечивает выполнение арис метических и логических . операций над двумя информациокньщй полями, рабположенными в словах А . и А 2 . Разрядность слов m 2 , причем нулевой разряд старший, а (гт1-1)-й разряд - младший. Инс}юрмационноё поле в слове А, задается двумя параметрами: базой t , определяющей положение первого элемента (бита) поля,. и длиной , соответствующей количеству элементов в поле, уменьшенному на единицу. Аналогичным образом поло сение поля в слове А j. задается базой bl . Параметр Е одинаков для обоих полей. Сдвигатель 4 комбинационного типа обеспечивает быстрый сдвиг числа А,| с целью выравнивания положения полей в словах А и А . Сдвигатель 4 осуществляет циклический сДвиг: слов только влево. Если ,то величина сдвига С Ь - Ь 2 . Если Ь Ь2, то следует произвести сдвиг вправо на величину что эквивалентно сдвигу влево на вештчину с т-(bj,-Ь )гп (Ь|- bg)- На выходе n разрядного вычитатёля 9 формируются разность ( Ь ). либо дополнительный код числа 6,, . Блок формирования маски обеспечивает выра ботку. т - разрядного двоичного слова М, содержащего единственную группу символов 1, в которой отсутствуют сим волы О (например слово О01111ОО). Положение группы символов I в маске определяется адресами начальной (Оц) и конечной (О) единиц ( отсчет позиций производится слева направо). Значения а ц и а ,сз Д 4 m-1 посту лают на входы блока 7 ;о входа устройства и с выхода п - разрядного дополнительного сумматора 8, соответственно На входы этого сумматора подаются парамётры 0 Преобразователь 5 кода обеспечивает формирование на своем выходе прямого или обратного кода чис.ла AJ, . Ко входам блока 2 логических операций подключены выходы блока 7 формирований маски, сдвигателя 4 и преобразователя 5 кода. На выходе этого блока вьфабатывается слово L , причем значения Д на выходе - го разряда формируются в соответствии с . одной из шестнадцати логических функций от аргументов рС- и OL (oCj -сигнал на выходе i -го разряда сдвигателя 4, oLj - сигнал на выходе «-го разряда преобразователя 5 кода) при единичном значении сигнала на выходе i -го разряда блока 7 формирования маски (jU 1). Вид погкческой функции определяется сигналами из блока 6 управления, Если jU;i О , то на выходе 4 -го разряда блока 2 всегда формируется сигнал 1 {Д Г). Блок 2 логических операций подсоединен своим выходом к первомуВХОДУ сумматора 1, на второй вход которого подается число выхода преобразователя 5 кода. Из блока 6 управления возможна подача сйгна- па р перейоса в младший разряд сумматора 1. Выходной коммутатор 3 обеспечивает формирование на выходе устройства резул тата R выполнения операций. На входы . этого коммутатора поступают сигналь1 щ aL сЛ.| , Л .и SV ( выходной сигнал разряда сумматора 1). На выходах тех разрядов коммутатора 3, для которых О. , формируются сигналы соответствующие определенной логическо оС; И d (в функшш от аргументов « быть логиче- частном случае это могут 67 7 ские константы О или ). На тех выходах коммутатора 3, для которых 1, формируется результат вьшолкения заданной арифметической или логической операции над полями. На входы элементов И блока 1О поступают Миска М с выхода блока 7 и результат R с выхода коммутатора 3. На выходе блока 10 вьфабатьюается значение признака Z нулевого значения информащш в зоне слова R, которая соответстует положению группы символов 1 маски. Работа блока 1О определяется логическим вьфажением т-1 2 А (ЯЛЯ)Л,(.)У,, Р: - значение f-го разряда слова Дешифратор 11 вырабатьгоает fp-разрядное слово и в коде J. из N на основании значения разрядов маски М. Положение единственнрй единицы в слове D совпадает с :полодселйем крайней слева единицы в маске. М, т. е. с положением старшего (знакового) разряда поля, соответствующего результату выполнения one- рации над полями в слове R . Значения сигналов 8 на выходах дешифратора 11 декодирования формируются в соответствии с логической формулой , ...,т--« Дешифратор может быть выпо.лнен так-г же в виде классического дешифратора (преобразователя п - разрядного кода в код 1 из К разрядности . ), на вход которого подается адрес оц началь-, ной единицы маски М. Значение а вырабатывается на одном из входов блока 7 формирования маски. Первый коммутатор 12 обеспечивает формирование признака 5 . На один из входов этого коммутатора подается р&зультат операции R . Другой вход подсоединен к . выходу дешифратора 11. Значение сигнала 3 на выходе коммутатора 12 определяется логическим вьфажением 0;.У:. Второй коммутатор 13 по построению аналогичен первому коммутатору 12. Его входы связаны с выходом блока 11 декодирования и с третьим выходом сумматора 1, на котором формируются сигналы 1 , PfD-i переноса. Сигнал переноса из t-го разряда сумматор }юрмируется в соответствии с формулой F,. -Л- - сс УЛ .Р. , 1 0,f;..., гл- 2/ причем Ттм Л -Г ти - тнгде Р - перенос в младший разряд сумма тора, поступающий из блока 6 управления. Логическое вьфаженИе для сигнала Р на выходе второго коммутатора 13 определяется логическим выражение P-{y.o(u,- Следовательно, значение сигнала Р сЬотёетстьУет значению сигнала переноса из разряда сумматора, непосредственно следующего за старшим (знаковым) разрядом поля, которое является ресзультатом вьтолнения заданной операции. При вьшолнении арифметических операций над полямизначения сигйалов на выходах тех разрядов блока 2 логических операций, для которых JU; f . определяется -логический функцией неравнознач ности .( V Л.{ оГ| , ). На тех выходахблока-2, для которых ju -о устанавливается сигнал (). Из выражения (1) следует, чт сигнал переноса из разряда сумматора 1; соответствующего положению старшего разряда результирующего поля, распространяется до выхода переноса из нулевого (старщего) разряда этого сумматора (второй выход сумматора), так как для старших разрядов сумматора, не отНОС5ПЦИХСЯ к результирующему полю, Я: 1 . Таким образом, на етором выходе сумматора 1 всегда вьфабатывается значение признака С резуЛ1 гата вШолнения арифметических операций над полями. Ко входам сумматора по Модулю два 14 подключены ВЙ5СОД втОрбгь коМмутато ра 13 (отсюда поступает сигнал Р ) и второй выход сумматора 1 (здесь формируется признак С). На выходе сумматора по модулю два 14 формируется значение признака Т№ $ШШйеШГ% ШЯ№етст ВИИ с вьгоажением; V pcvP.C Работу устройства рассмотрим на примере вьтолнения операции сложения двух пятиразрядных полей (фиг. 2). В первом поле (слово А ) задано положительное число 5 (старший разряд - знаковый), П

6740.17 ложение поля определяется базой Ц - 9 Второе поле (слово А содержит отрипательное число 4 (число представлено в дополнительном коде). Положение поля определяется базой Ь2.4. Очевидно, что в рассматриваемом примере Е 4. Параметры Ь , bg и , операнды , А и соответствующий код операции КО поступают на входы устройства. На выходе вычи1гателя 9 формируется пара,{етра Сг Ц - Ь, 5, -рбеспечивающее сдвиг влево слова А и выравнивание полож.ения обрабатьшаемых полей. Формируемые в данном случае значения разрядов слов М и D указаны на фиг. 2. /4 ; 5 Яб Я7-|1 « 1 , 4 Здесь же -приведены значения разрядов слова L . При вьтолнении операции сложения полей сигналы переноса В результате вьшолнения заданной операции получается положительное число 1. В остальных разрядах слова результата Д для рассматриваемого примера сохранены значения соЬтвётствующих разрядов слова А (поля А и А ). Признаки результата имеют следующие значение , 1 , -о Z 0 , в предлагаемом устройстве обеспечивается одновременное формирова;кие результата вьшолнения операции над полями и значений признаков Z , S , С , .V для этого результата. Это приводит к повышению производительности предлагаёйого устройства в основном, пи двум причинам.; В устройстве по авт. св. N 538362 значения признаков 2, С и V получаются на основе признака С (второй вь$ход сзгмматора 1) в результате вьтолнения дополнительных операций в устройстве. Значение признака Z вьфабатывается на втором выходе сумматора, если из нулевого числа Бьгчесть результат вьтоянения операции над полями (едтиничное значение Z формируется при нулевом результате операции). Значение признака Z может быть получено на втором вькоде сумматора при вьтолнении дополнительной операции сложения знакового (старшего) разряда результирующего поля с единицей (единичное значение 5 формируется при единичном значении знакового разряда). Для получения значения признака Y переполнения следует вьтолнить последовательность из 4-5 дополнительных операций (например, значение 5 можно определить

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информационных полей переменной длины | 1978 |

|

SU767769A1 |

| Устройство для выполнения арифметических и логических операций над словами | 1978 |

|

SU767757A1 |

| Устройство для выполнения арифметических и логических операций | 1975 |

|

SU538362A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Микропроцессорная вычислительная система | 1975 |

|

SU674025A1 |

| Устройство для определения длины строки символов | 1980 |

|

SU976438A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

Авторы

Даты

1979-07-15—Публикация

1977-03-17—Подача