-1

Изобретение относится к области вычислительнойтекники и может быть ис- пользовано либо как законченное устройство, .либо в качестве модуля в интег- ральном исполнении для построения MHOIпоразрядных устройств, выполняющих арЧ1}зметические и логические операции как нац полноразрядными словами, так. и над отдельными группами битов, произвольно расположенными в словах.

.Известно устройство для выполнения логических и арифметических операций надполноразрядными словами или полями битов (группами рядом стоящих битов) , содержащее сумматор, блок логи , ческих операций, выходной коммутатор, сдвигатель, преобразователь кдда, формирователь маски,- дополнительные сумматор и в.ычитатель, блок управления

w«..

Это устройство не позволяет одновременно выполнять логические и арифметические операции над несколькими полями .битов в полноразрядных словах. Такие

.операции на указанном устройстве можно осуществит.ь лишь последовательно, выполняя за один раз операцию над одним полем слова или двумя полями, располо:женными каждое в своем слове. Это обусловливает низкое быстродействие указанного устройства при выполнении операций над произвольными группами битов полноразрядных слов.

Кроме этого, при выполнении опера10ций над массивами слов, когда в каждом слове поля располомсены одинаково (а это явля.ется одним из распространенных случаев обработки информации), в каждый раз требуется заново вычислять началь15ный и конечный номера разрядов обраба.тываемого поля и формировать маску. Это требует дополнительных затрат времени, а введенное в устройство оборудование (формирователь маски, дополни20тельные сумматор и вычислитель) становится излишним.

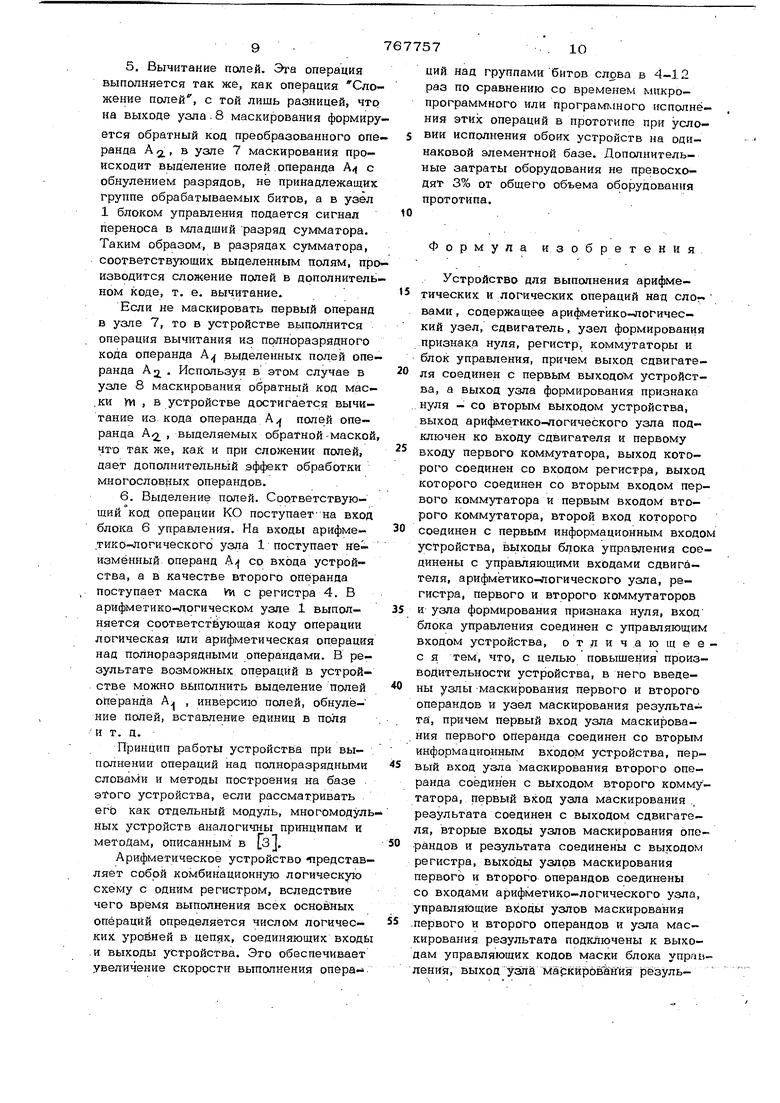

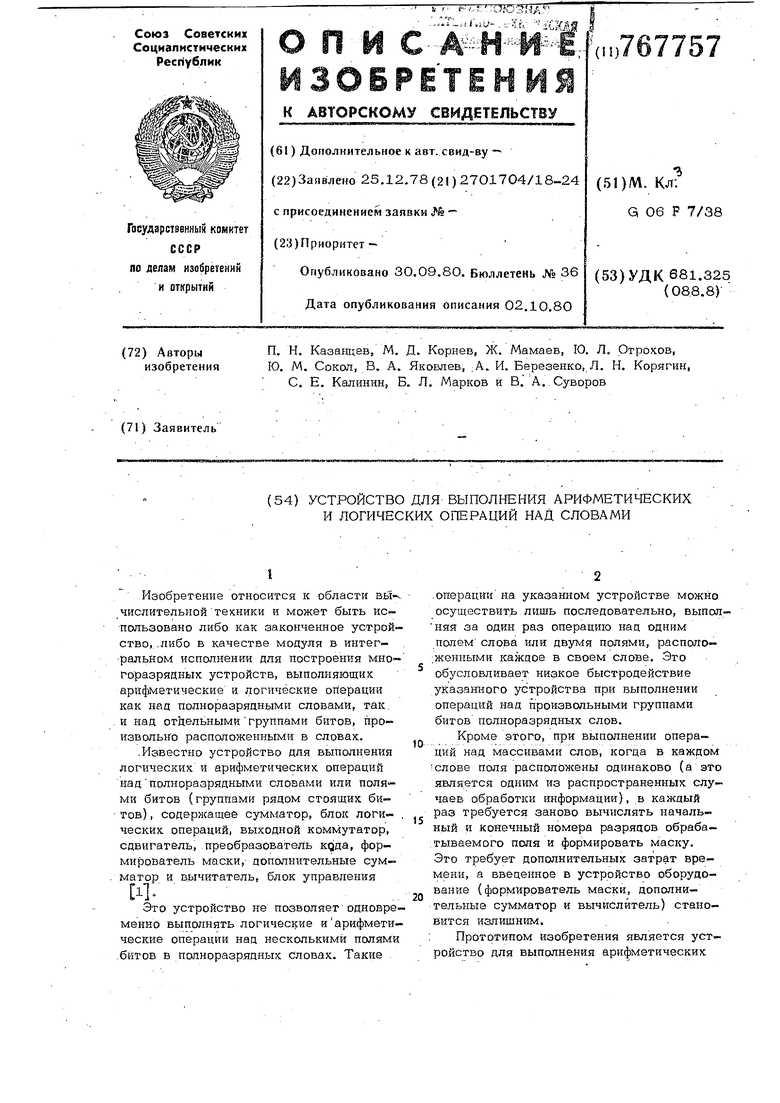

: Прототипом изобретения является устройство для выполнения арифметических и логических операций над ловами, содержащее арифметико-логич ский узел, сдвигатель, узел формиров :лия признака нуля, регистр, коммутаторы и блокуаравления. Выход сдвигателя является первым выходом устройства и входом узла формирования признака нуля, выход которого служит вторым выходом устрой- ства. Выход арифметико-логического уз ла соединен с входом сдвигателя и первым входом первого коммутатора, которого подключе: к входу регистра, выход регистра - со, вторым входом первого коммутатора и первым в кодом второго коммутатора. Второй вход второго коммутатора является первым информационным входом устройства, а выход втО рого коммутатора - входом арифметикологического узла, другой вход которого служит вторьпи информационным входом устройства, Выгсоды блока управления со- единены с управляющими входами сдвига теля, арйфметкко-логического узла, ком- мутаторов, регистра и узла формирования признака куля. Вход блока управления является управляющим входом устрой ства 2l. При выполнении операций над группам битов одного или двух слов в этом устройстве требуе предварительно е. вьтол нейие операций выделения битов, подлежа щих обработке, с помощью предварительн формируемых масок, В этом причина низкой производительности устройства при работе с группами битов. -, 1 --. . Цель изобретения - повышение npoTOводительности устройства, Эта цель достигается тем, что в устройство, содержащее арифметико-логический узел, сдвцгатель, узеп формирования признака нуля, регистр, коммутаторы И блок управления, причем выход сдвигателя соединён с первым выходом устройства, а выход узла формирования признака нуля со. вторым выходом устройства, выход арифметико-логического узла подключен ко входу сдвигателя и первому входу первого коммутатора, выход которого соединен со входом регистра, выход которого связан со вторым входом первого коммутатора и первым входом, второго коммутатора, второй вход которого соединен с первым информационным входом устройства, выходы блока управления соединены с управляющими входами сдвигателя, ариф метико-логического узла, регистра, первого и второго коммутаторов и узла фор« мирования признака нуля, вход блока управления соединен с управляющим входом устройства, введены узлы маскирования первого и второго операндов и узел маскирования результата. При этом первый вход узла маскирования первого операнда соединен со вторым информационным входом устройства, первый вход узла маскирования второго операнда. - с выходом второго коммутатора, первый вход узла маскирования результата связан с выходом сдвигателя, вторые входы узлов маскирования операндов и результата .с выходом регистра. Выходы узлов маскирования первого и второго операндов подключены к входам арифметико-логичеЪкогв узла, управляющие входы узлов маскирования первого и- второго операндов и узла маслсирования результата к выходам управляющих кодов маски блока управления, а выход узла маскирования результата - ко входу узла формирования признака нуля. На фиг. 1 представлена блок-схема устройства; на фиг. 2 показан пример выполнения логической операции над полями слов. .. , Устройство для выполнения арифметических и логических операций над слова- ми содержит арифметико-логический -узел 1, сдвигатель 2, коммутатор 3, регистр 4, коммутатор 5, блок 6 управления, узел 7 маскирования первого операнда, узел 8 маскирования второго операнда, узел 9 маскирования результата .и узел 10 формирования признака нуля. Перечисленные узлы соединены в устройство следующим образом. Входы арифметико-логического узла 1 соединены с выходами узла 7 маскирования первого операнда и узла 8 маскиро- вания второго операнда, выход его со входом сдвигателя 2 и с. одним из входов коммутатора 3. Второй вход сдвич гателя связан с выходом регистра 4, который, кроме того, соединен с одним из входов коммутатора 5, узла 7 маскирования первогооперанда, узла 8 .маскирования второго операнда и узла 9 маскирования результата, вторые входы этих узлов соединены соответственно со входами А, и А устройства, с выходом. коммутатора 5 и с выходом сдвигателя 2; выход коммутатора 3 соединен со входом регистра 4, а выход узла 9 маскирования результата - со входом узла , 10 формирования признака нуля. Выход сдвигателя 2 соединен с первым выходом устройст:)а, а; выход узла 10 фор;мирования признака - со вторым выхо

дом устройства. Работа всех перечисленных узлов и . их взаимодействие осуществляется блоком 6 управления, выходы которого соединены со всеми узлами;. вход блока 6 соединен с управляющим

входом устройства, на который подается код операции.

Устройство обеспечивает выполнение арифме-гических операций типа сложения, вычитания и логических операций как . над полноразрядными словами, так и над отдельными группами битов полноразряд- нык слов, а также при циклической работе устройства - арифметических операций типа умножения и деления над пол норазрядными словами. Разрядность словпроизвольная.

При выполнении операций над полноразрядными словами - операндами А и А2 или группами битов, расположенных в словах А и Aj , устройство работает следующим образом.

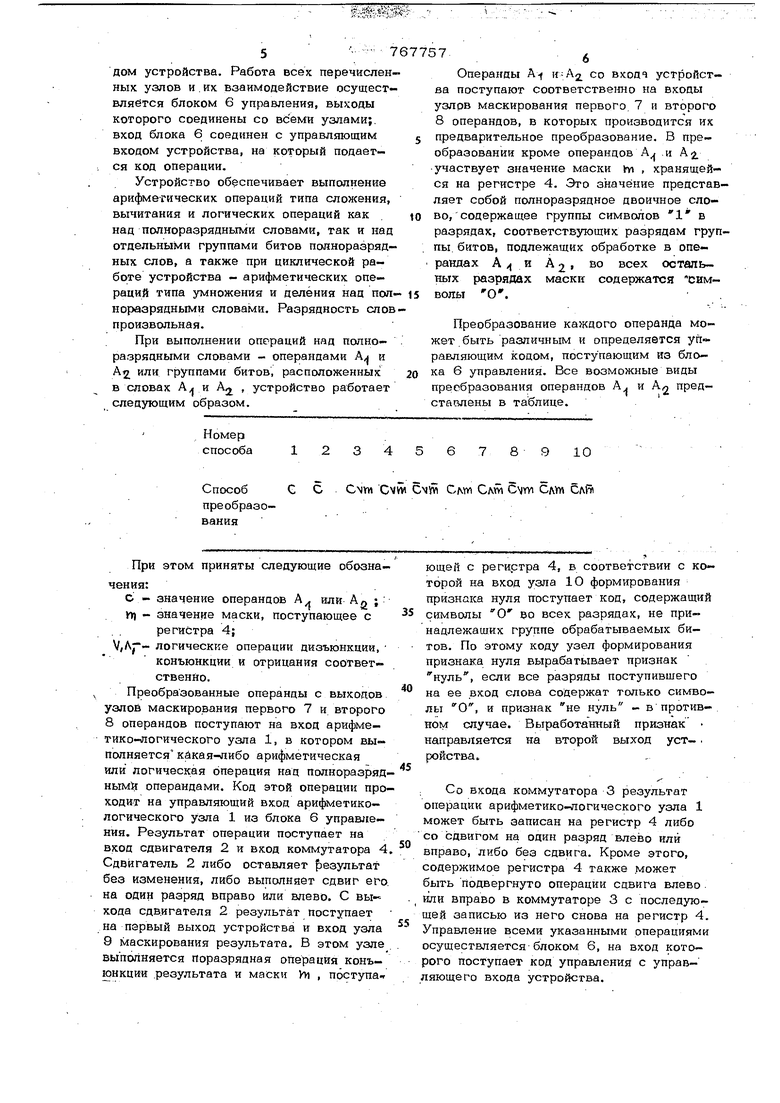

Номер способа

С CNYH Cvw CNyvi CNW Слгм CJYYI СЛУП Слй

СпособG

преобразования

При этом приняты следующие обозначения:

О - значение операндов А, или Ал ; щ - значение маски, поступающее с

регистра 4;

У,Лр- логические операции дизъюнкции, конъюнкции и отрицания соответственно.

Преобразованные операнды с выходов узлов маскирования первого 7 и второго

8операндов поступают на вход арифметико-логического узла 1, в котором выполняется кйкая-либо арифметическая

или логическая операция над полноразряднымй операндами. Код этой операции проходит на управляпющий вход арифметикологического узла 1 из блока 6 управления. Результат операции поступает на вход сдвигателя 2 и вход коммутатора 4. Сдвйгатель 2 либо оставляет результат без изменения, либо выполняет сдвиг его. на один разряд вправо или влево. С выхода сдв.игателя 2 результат поступает на первый выход устройства и вход узла

9маскирования результата. В этом узле выполняется поразрядная операция конъюнкции .результата и маски Уи , поступав

Операнды A-f со входч устройства поступают cooTBeTCTseifflo на входы узлов маскирования первого 7 и второго 8 операндов, в которых производится их предварительное преобразование. В преобразовании кроме операндов А .и А2. участвует значение маски hi , хранящейся на регистре 4. Это значение представляет собой полноразрядное двоичное слово, содержащее группы символов в разрядах, соответствующих разрядам группы, битов, подлежащих обработке в операндах А и А 2 , во всех остальных разрядах маски содержатся символы О.

Преобразование каждого операнда может быть различным и определяется уп равляющим кодом, поступающим из блока 6 управления. Все возможные виды преобразования операндов А и А2 представлены в таблице.

8 9

6

10

ющей с регистра 4, в соответствии с которой на вход узла 10 формирования признака нуля поступает код, содержащий символы О во всех разрядах, не принадлежащих группе обрабатываемых битов. По этому коду узел формирования признака нуля вырабатывает признак нуль, если все разряды поступившего на ее вход слова содержат только символы О, и признак не нуль - в противном случае. Выработанный признак направляется на второй выход уст- . ройства.

: Со входа коммутатора 3 результат операции арифметико-логического узла 1 может быть записан на регистр 4 либо со сдвигом на один разряд вле1зо или вправо, либо без сдвига. Кроме этого, содержимое регистра 4 также .может быть подвергнуто операции сдвига влево или вправо в коммутаторе 3 с последующей записью из него снова на регистр 4. Управление всеми указанными операциями осуществляется блоком 6, на вход которого поступает код управления с управляющего входа устройства.

Рассмотрим отдельно примеры, поясняющие работу устройства лишь при ewnon- нении операций над группам битов.

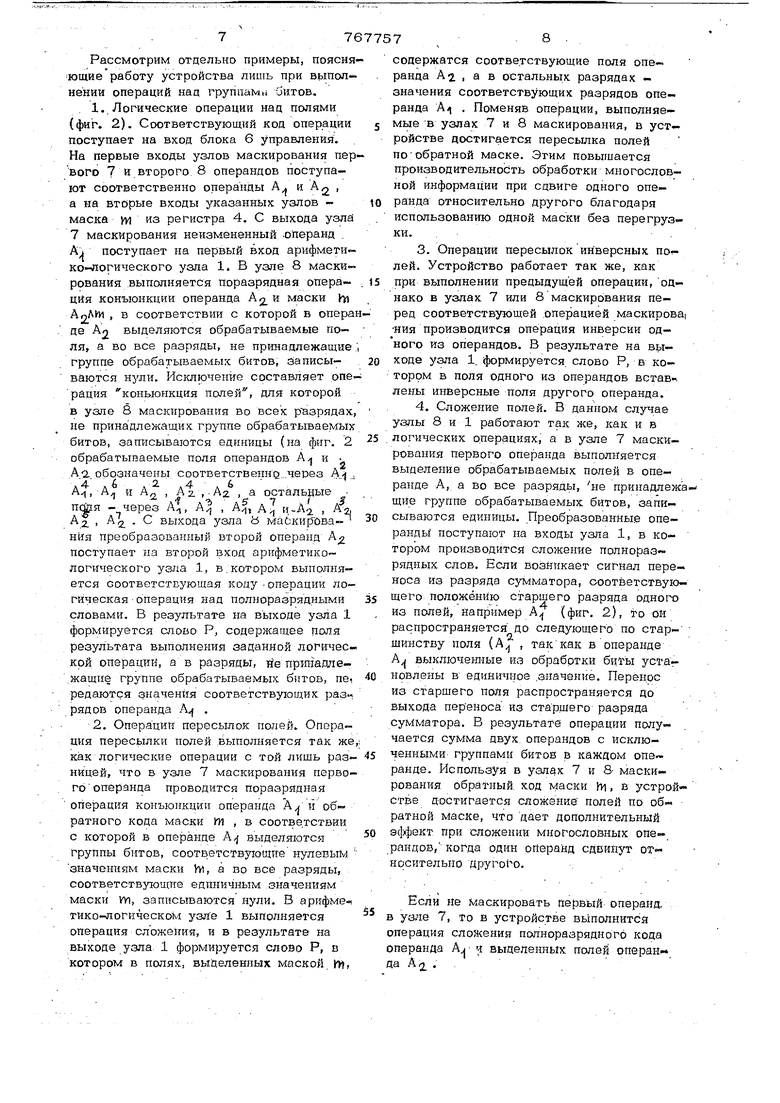

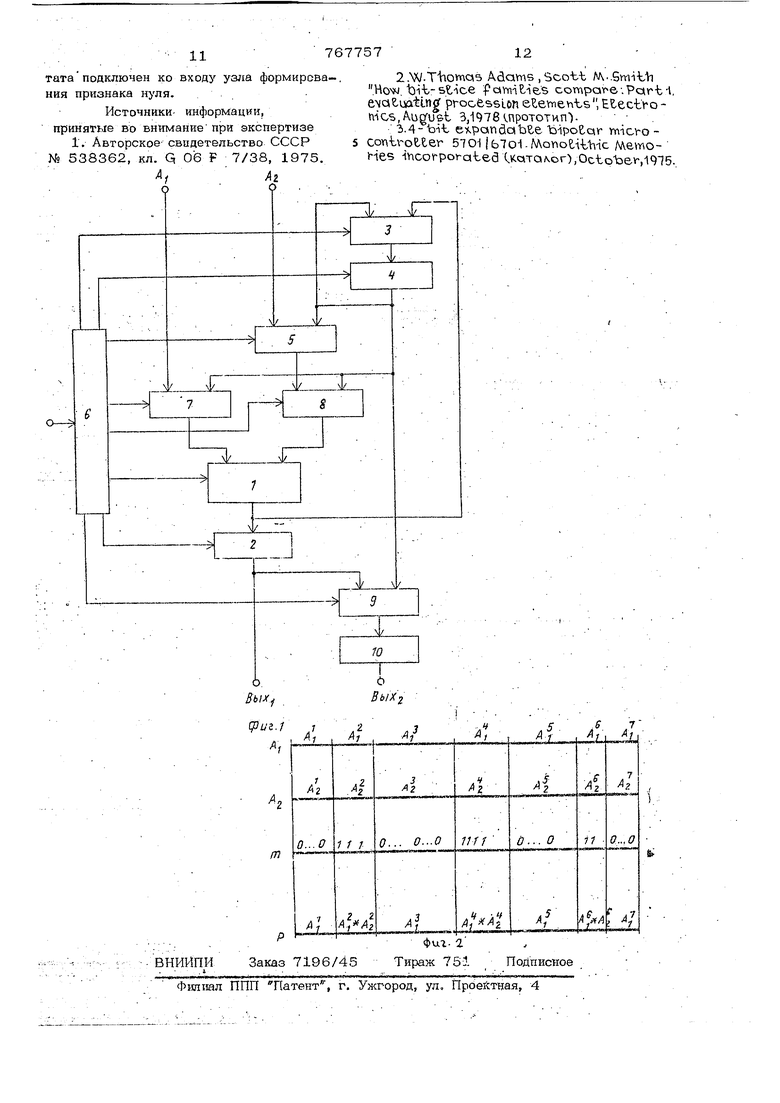

1. Логические операции над полями (фиг. 2). Соответствующий код операции поступает на вкод блока 6 управления. На первые входы узлов маскирования пер вого 7 и второго 8 операндов поступают соответственно операнды А 2 а на вторые входы указанных узлов -

маска уи из регистра 4. С выхода узлй 7 маскирования неизмененный .операнд , АI поступает на первый вход арифмети КС-логического узла 1. В узле 8 маскирования выполняется поразрядная опера цИя конъюнкции операнда Ag, и маски h) AnAVH , в соответствии с которой в операнде АО выделяются обрабатываемые по- ля, а во все разряды, не принадлежащие, группе обрабатываемых битов, йаписы- ваются нули. Исключение составляет рпе рация коньюнкция полей, для которой в узле 8 маскирования во всех разрядах, не принадлежащих группе обрабатываемых битов, записываются единицы (на фиг. 2 обрабатываемые поля операндов А и А2-. обозначены соогветственно..через А ., А, А и А , A-2.,. , а остальные . пфя - через А , А , А|, д ц.А , А а А 5 , А 2 . С выхода уапа 8 ма6кир 0ва-.

нйя преобразованный второй операнд А поступает на второй вход арифметико логического узла 1, в.котором выполняется соответствующая коду-операции логическая-операция над полноразрядными словами. В результате на выходе узла 1 формируется слово Р, содержащее поля результата выполнения заданной логической операции, а в разряды, не пртгаадле.жащие группе обрабатываемых бггтов, nei редаются значения соответствующих paa-i рядов операнда А ..

2. Операции пересылок полей. Операция пересылки полей .выполняется так же как логические операции с той лишь разницей, что в узле 7 маскирования первогооперанда проводится поразрядная операция конъюнкция операнда А / и обратного кода маски W , в соответствии с которой в операнде А выделяются

группы битов, соответствующие нулевым значениям маски hi, а во все разряды, соответствующтте единичным .значениям маски Wi, записываются нули. В арифме тико-логическом узле 1 выполняется

операция сложения, и в результате на выходе узла. 1 формируется слово Р, в котором в полях, выделенных маской, ht

содержатся соответствующие поля операнда AT. , а в остальных разрядах значения соответствующих разрядов операнда А-( . Поменяв операции, выполняемые в узлах 7 и 8 маскирования, в устройстве достигается пересылка полей пообратной маске. Этим повышается производительность обработки многословной информации при сдвиге одного операнда относительно другого благодаря использованию одной маски без перегрузки. ..

3.Операции пересылок инверсных полей. Устройство работает так же, как при выполнении предыдущей операции, однако в узлах 7 или 8 маскирования перед соответствующей операцией маскиров ния производится операция инверсии одного из операндов. В результате на вьтходе узла 1. формируется, слово Р, в котором в поля одного из операндов вcтaв лены инверсные поля другого операнда.

4.Сложение полей. В данном случае узлы 8 и 1 работают так же, как и в логических о.перациях, а в узле 7 маскирования первого операнда выполняется выделение обрабатываемых полей в операнде А, а во все разряды, не принадлежщие группе обрабатываемых битов, записываются единицы. Преобразованные операнды поступают на входы узла 1, в котором производится сложение полнораз- рядных слов. Если возникает сигнал переноса из разряда сумматора, соответствующего положению старшего разряда одного из полей, например А (фиг. 2), то ой распространяется до следующего по старшш-ютву поля ( , таккак воперанде

А выключеш-1ые из обработки биты устаг новлены в единичное .значение. Передрс из старшего поля распространяется до выхода переноса из старщего разряда сумматора. В результате операции получается сумма двух, операндов с исключенными группами битов в каждом oneранде. Используя в узлах 7 и 8- маскирования обратный, ход маски Ж, в устрой стве достигается сложение полей по об ратной маске, что дает дополнительный эффект при сложении многословных опе рандов, когда один операнд сдвинут относительно другого.

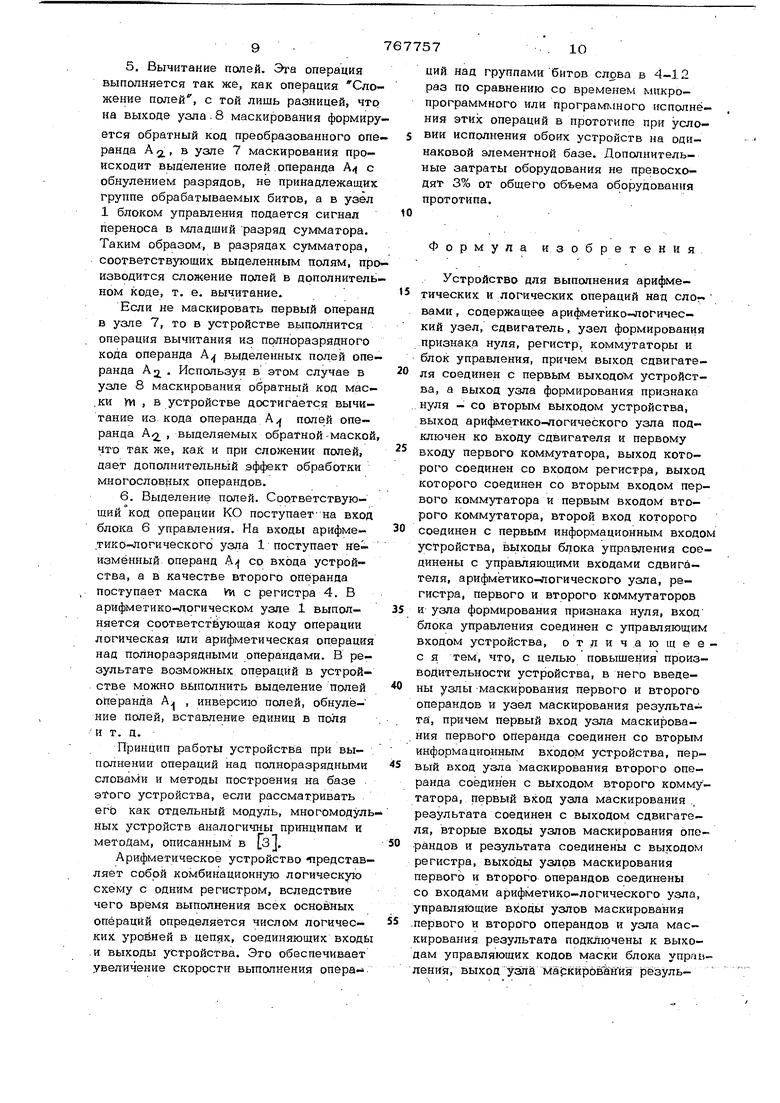

Если не маскировать первый операнд. в уапе 7, го в устройстве выполнится операция сложения полноразрядного кода операнда ч выделенных полай операи« да А. . . 5.Вычитание полей. Эта операция выполняется так же, как операция Сло жение полей, с той лишь разницей, что на выходе узла . 8 маскирования формиру ется обратный код преобразованного опе ранда А 2;, в узле 7 маскирования происходит выделение полей операнда А с обнулением разрядов, не принадлежащих группе обрабатываемых битов, а в узел 1 блоком управления подается сигнал переноса в младший разряд сумматора. Таким образом, в разрядах сумматора, соответствующих выделенным полям, изводится сложение полей в дополнитель ном коде, т. е. вычитание. Если не маскировать первый операнд в узле 7, то в устройстве выполнится операция вычитания из прлноразрядного кода операнда А выделенных полей опе ранда А 2 . Используя в этом случае в узле 8 маскирования обратный код мас.ки nt , в устройстве достигается вычитание из кода операнда А полей операнда А/2 , выделяемых обратной-маской что так же, как и при сложении полей, дает дополнительный эффект обработки миогословцых операндов. 6.Выделение полей. Соответствующий °коД операции КО поступает на вход блока 6 управления. На входы арифметико-логического узла 1 поступает неизменный операнд A,j со входа устройства, а в качестве второго операнда поступает маска 1гц с регистра 4. В арифметико-л.огическом узле 1 выполняется соответствующая коду операции логическая или арифметическая операция над полноразрядными операндами. В результате возможных операций в устройстве можно выполнить выделение полей операнда А; , инверсию полей, обнуление полей, вставление единиц в поля и т. д. Принцип работы устройства при выполнении операций над полноразрядными cлoвa fи и методы построения на базе этого устройства, если рассматривать его как отдельный модуль, многомодуль ных устройств аналогичны принципам н методам, описанным в sj. Арифметическое устройство представляет собой комбинационную логическую схему с одним регистром, вследствие чего время выполнения всех основных операций определяется числом логических, уровней в цепях, соединяющих входы .и выходы устройства. Это обеспечивает увеличение скорости выполнения опера-. ций над группами битов слова в 4-12 раз по сравнению со временем микропрограммного или програмглного исполнения этих операций в прототипе при условии исполнения обоих устройств на одинаковой элементной базе. Дополнительные затраты оборудования не превосходят 3% от общего объема оборудования прототипа. Формула изобретения Устройство для выполнения арифметических и логических операций над ело- вами, содержащее арифметико-логический узел, сдвигатель, узел формирования признака нуля, регистр, коммутаторы и блок управления, причем выход сдвигателя соединен с первым выходом устройства, а выход узла формирования признака нуля - со вторым выходом устройства, выход арифметико-логического узла подключен ко входу сдвигателя и первому входу первого коммутатора, выход которого соединен со входом регистра, выход которого соединен со вторым входом первого коммутатора и первым входом второго коммутатора, второй вход которого соединен с первым информационным входом устройства, выходы блока управления соединены с управляющими входами сдвигателя, арифметико-логического узла, регистра, первого и второго коммутаторов и узла формирования признака нуля, вход блока управления соединен с управляющим входом устройства, отличающеес я тем, что, с целью повышения производительности устройства, в него введены узлы маскирования первого и второго операндов и узел маскирования результата, причем первый вход узла маскирования первого операнда соединен со вторым информационным входом устройства, первый вход узла маскирования второго операнда соединен с выходом второго коммутатора, первый вход узла маскирования ., результата соединен с выходом сдвигателя, вторые входы узлов маскирования операндов и результата соединены с выходом регистра, выходы узлов маскирования первого и второго операндов соединены со входами арифметико-логического узла, управляющие входы узлов маскирования первого и второго операндов и узла маскирования результата подключены к выходам управляющих кодов маски блока управления, выход узла ма ;кйр6ванйя результата подключен ко входу узла формирования признака нуля.,

Источники- информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 538362, кл. Q 06 F 7/38, 1975.

l-X.Ttiomois Adams , Sco-t-t /A..SmitVi Но, tii-t-btice favYi-iWes compare-.Par-b-I ,uAtlng procession elements,E,ect on-ics, August 3,1)78 .прототипу

3.4- b-it еу.рапдаЪ.е bipoE.cir micv-o coY t -otter 5701 jblol-MonotitWc MevY oHes -incov-por-ateat.),Octobev-,19l5.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки информационных полей переменной длины | 1978 |

|

SU767769A1 |

| Устройство для обработки данных переменной длины | 1976 |

|

SU648984A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Устройство для обработки информации | 1979 |

|

SU868765A1 |

| Устройство для выполнения арифметических и логических операций | 1977 |

|

SU674017A2 |

| Процессор | 1984 |

|

SU1246108A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Процессор обработки изображений | 1988 |

|

SU1532949A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Авторы

Даты

1980-09-30—Публикация

1978-12-25—Подача