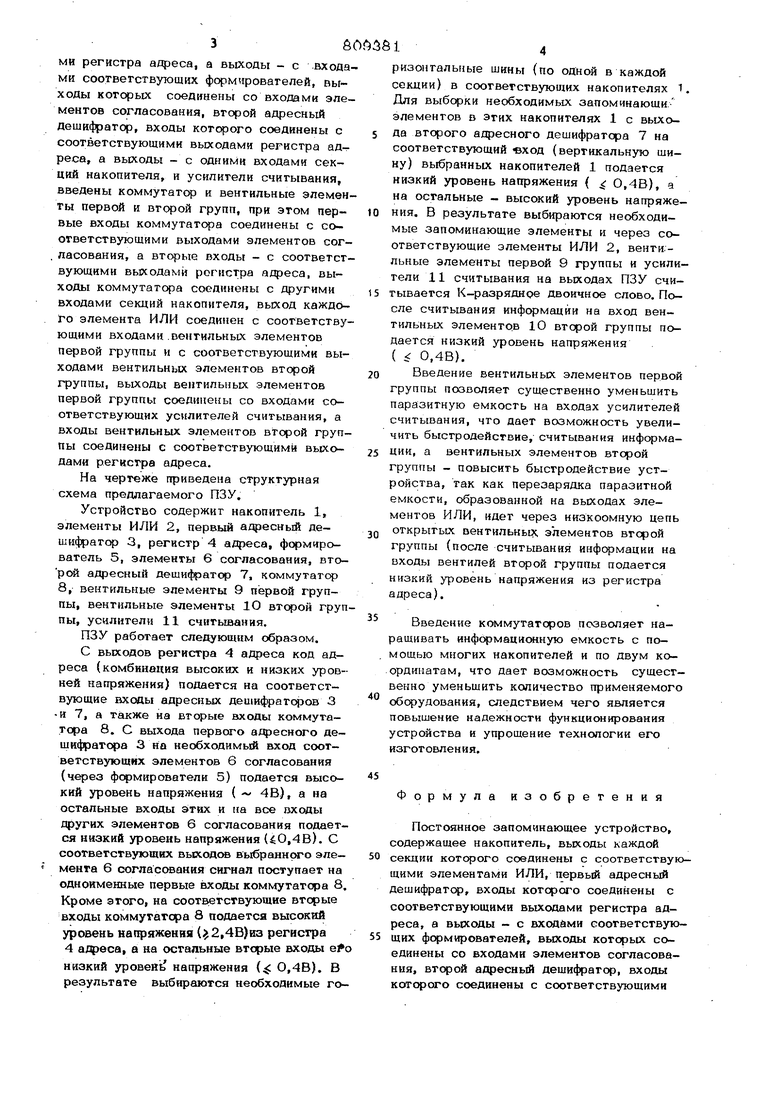

Изобретение относится к вычислитель- Hcrfi технике, в частности, к микроэлектронным запоминающим устройствам, и мо жет быть использовано в устройствах обработки цифровой информации в качестве постоянной памяти подпрограмм, табличных данных, функций и преобразователей кодов. Известно постоянное, запоминающее устройство (ПЗУ) .содержащее адресный дешифратор, диодно-матричный накопитель, разделенный на секции, вентили, шины управления и шифратор tl. Недостатками известного ПЗУ является то, что при построении большой информационной емкости необходимо использовать большое количество элементов, что приводит к усложнению устройства, снижению его надежности, увеличению паразитных емкостей, а следовательно, и уменьшению быстродействия. Наиболее близким по техническсй сущности к предлагаемому является ПЗУ, содержащее адресные дешифраторы первой и второй групп, а также элементы согласования, диодно-матричный накопитель, элементы ИЛИ (диодные сборки), усилители считывания и формирователи 12. Недостатками Данного ПЗУ явл$1ются (малое быстродействие, связанное с большой емкостью, образованной на выходах элементов ИЛИ, и .то, что при построении ПЗУ с большой информадисжнс емкостью возможно наращивание только по одной координате, что приводит к применению большсяо количества оборудования, а следовательно, к снижению надежности функционирования устройства и усложнению технологии его изготовления. Цель изобретения - упрощение устройства и повышение его быстродействия. Поставленная цель достигается гем, что в постоянное запоминающее устройство, содержащее накопитель, выходы каждой секций которого соединены с соответствующими элементами ИЛИ, первый адресный дешифратор, входы которого соединены с соответствующими выхода36ми регистра адреса, а выходы - с .входа ми соогвегствующнх формирователей, выходы которых соединены со входами эле ментов согласования, второй адресный Дешифратор, входы которого соединены с соответствующими выходами регистра адреса, а выходы - с одними входами секций накопителя, и усилители считывания, введены коммутатор и вентильные элемен ты первой и второй групп, при этом первые входы коммутатора соединены с соответствующими выходами элементов сог. ласования, а вторые входы - с соответст вующими выходами регистра адреса, выходы коммутатора соединены с другими входами секций накопителя, выход каждого элемента ИЛИ соединен с соответству ющими входами .вентильных элементов первой группы и с соответствующими выходами вентильных элементов второй группы, выходы вентильных элементов первой группы соединены со входами соответствующих усилителей считывания, а входы вентильных элементов второй груп пы соединены с соответствующими выходами регистра адреса. На чертеже приведена структурная схема предлагаемого ПЗУ. Устройство содержит накопитель 1, элементы ИЛИ 2, первый адресный дешифратор 3, регистр 4 адреса, формирователь 5, элементы 6 согласования, второй адресный дешифратор 7, коммутатор 8, вентильные элементы 9 первой группы, вентильные элементы lO второй груп пы, усилители 11 считьшания. ПЗУ работает следующим образом. С выходов регистра 4 адреса код адреса (комбинация высоких и низких уровней напряжения) подается на соответствующие входы адресных дешифратчэов 3 и 7, а также на вторые входы коммутатора 8. С выхода первого адресного дешифратора 3 на необходимый вход соответствующих элементов б согласования (через фсрмирователи 5) подается высокий уровень напряжения ( 4В), а на остальные входы ЭТих и на все входы других элементов 6 согласования подает ся низкий уровень напряжения (0,4В). С соответствующих выходов вь1браннсяго эле- мента 6 согласования сигнал поступает на одноименные первые входы коммутатора 8 Кроме этого, на соответствующие вторые входы коммутатора 8 подается высокий уровень напряжения ( 2,4В)иа регистра 4 афеса, а на остальные вторые входы е низкий ypOBeHtJ напряжения ( 0,4В). В результате выбираются необходимые го 14 ризонгальные шины (по одной в каждой секции) в соответствующих накопителях 1. Для выбелки необходимых запоминающи.элементов в этих накопителях 1 с выхода второго адресного дешифратора 7 на соответствующий «ход (вертикальную шину) выбранных накопителей 1 подается низкий уровень напряжения ( 0,4В), а на остальные - высокий уровень напряжения. В результате выбираются необходимые запоминающие элементы и через соответствующие элементы ИЛИ 2, венти.льные элементы первой 9 группы и усилители 11 считывания на выходах ПЗУ считывается К-разрядное двоичное слово. После считывания информации на вход вентильных элементов 10 второй группы подается низкий уровень напряжения ( 0,4В). Введение вентильных элементов первой группы позволяет существенно уменьшить паразитную емкость на входах усилителей считывания, что дает возможность увеличить быстродействие, считьшания информации, а вентильных элементов второй группы - повысить быстродействие устройства, так как перезарядка паразитной емкости, образованной на выходах элементов ИЛИ, идет через низкоомную цепь открытых вентильных; элементов второй группы (после считывания информации на входы вентилей второй группы подается низкий уровень напряжения из регистра адреса). Введение коммутаторов позволяет нарашивать информационную емкость с помошью многих накопителей и по двум координатам, что дает возможность существенно уменьшить количество применяемого оборудования, следствием чего является повышение надежности функционирования устройства и упрощение технологии его изготовления. Формула изобретения Постоянное запоминающее устройство, содержащее накопитель, выходы каждой секции которого соединены с соответствующими элементами ИЛИ, первый адресный дешифратор, входы которого соединены с соответствующими выходами регистра адреса, а выходы - с входйми соответствующих формирователей, выходы которых соединены со входами элементов согласования, второй адресный дешифратор, входы которого соединены с соответствующими

выходами регистра адреса, а выходы С одними входами секций накопителя, в усилители считывания, отличающееся тем, что, с целью упрощения устройства и повышения его быстродейсл ВИЯ, в него введены коммутатор, вентильные элементы первой и второй групп, при этом первые входы коммутатора соединены с соответствующими выходами элементов согласования, а Вторые входы с соответствующими выходами регистра адреса, выходы коммутатора соединены с другими входами секций накопителя, выход каждого элемента ИЛИ соединен с соответствующими входами вентильньсх элементов первой группы и с соответствующими выходами вентильных элементов второй группы, выходы вентильных эйег ментов первой группы соединены со входами соответствующих усилителей считьшания, а входы вентильных элементов второй группы соединены с соответствующим выходом регистра адреса.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 461451, кл. G 11 С 17/00, 1973.

2. Брик Е. А. Техника ПЗУ, М., Сов. радио , 1973, с. 34(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1978 |

|

SU767841A2 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU799006A1 |

Авторы

Даты

1981-02-28—Публикация

1979-05-23—Подача