подключены к соответствующим выходам блока хранения констант, а выходы элементов ИЛИ группы подсоединены к перзой группе входов комбннацнонных сумматоров 1-руппы. Выходы младших разря:(()В каждого регистра приема п передачи кода 1руппы подключены соответственно ко второй группе входов комбинационных С} мматоров группы, выходы которых подсоединены к первым входам соответствуюгцпх элементов И приема кода второй группы, вторые входы которых соединены с унравляюплей шиной округления устройства. Выходы элемеитов И приема кода второй группы подключены к информационным входам соответствуюш;их регистров приема и передачи кода группы, устаиовочпые входы которых подсоединены к шиие устаиовкп в пуль устройства. Выходы всех разрядов регистров приема и передачи кода группы являются выходными ин(fJOpмaцпoнпыми шинами, выходы младших разрядов регистра приема и передачи кода группы соединены с соответствующими входами блока хранения констант.

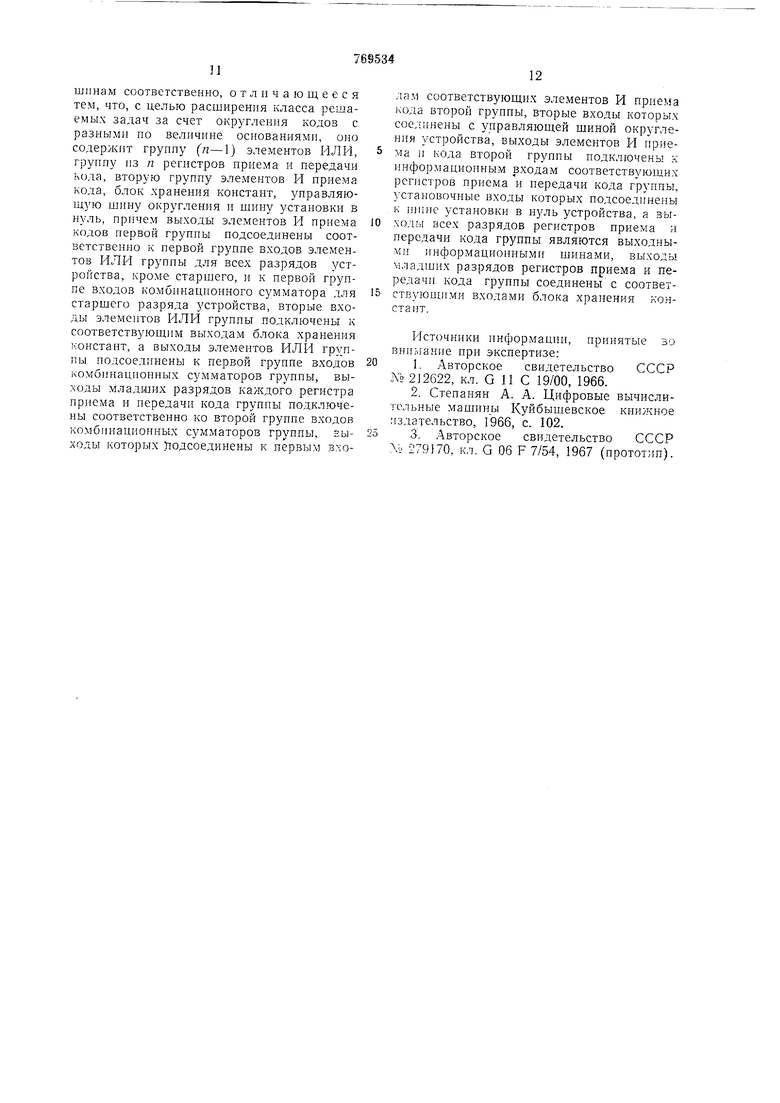

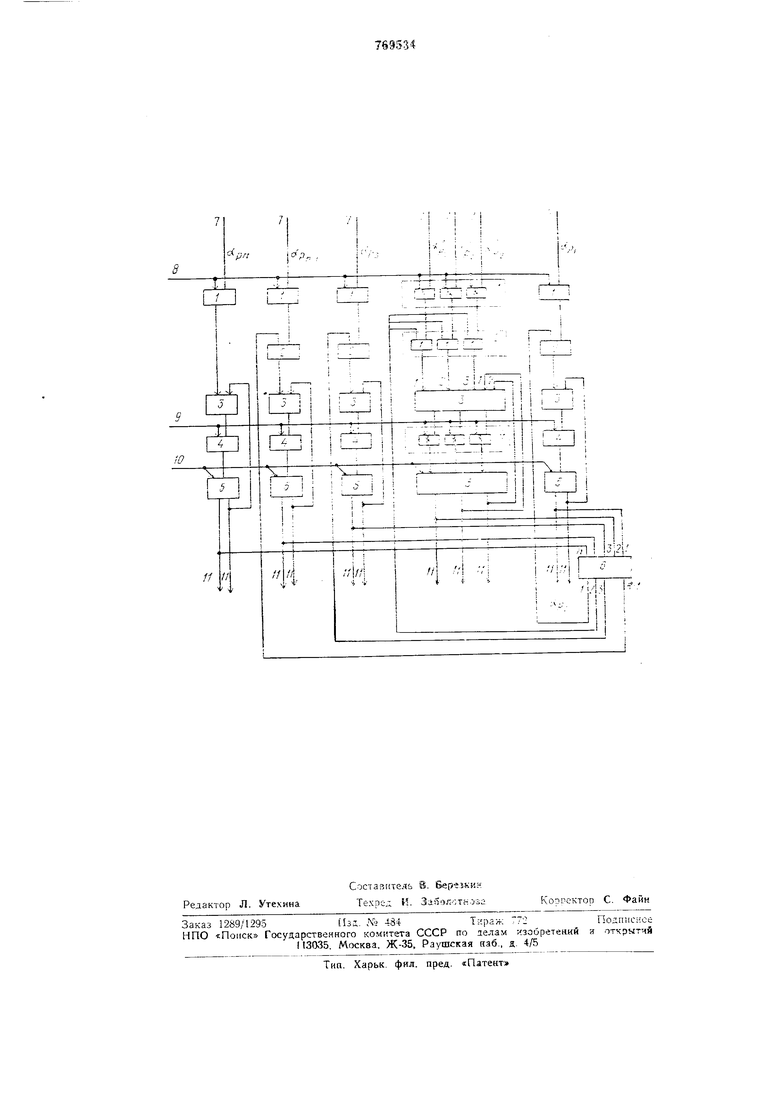

На чертеже изображена структурная схема устройства для округления кодов.

Устройство для округления код(Ш содержит первую группу элементов И приема кода /, двухвходовые элементы ИЛИ 2, комбинациоииые сумматоры 3 на два входа, с разрядностями выбранных оснований Р/ ((1,2 /7), вторую группу элемеитов И приема кода 4, регистры приема и передачи кода 5 с разрядностями выбранных оснований, блок хранения констант 6, входные информационные шины 7, управляющую шину записи 8, управляющую округления 9, управляющую шину установки в нуль 10 и выходные информационные шины //. Выходы (i-fl)-x разрядов регистра 5 основания Р,- соединены со входами г-х разрядов иервого слагаемого сумматора 3 того же основания, выходы которого соедниены через схему приема кода 4 со входо.м регистра 5 основания Pi.

Входы (f-f 1)-х разрядов регистра 5 основания РЗ соединены со входами г-х разрядов первого слагаемого сумматора 3 того же основания, выходы которого соединены через схе.м} приема кода 4 со входом регистра 5 основания Рг- Выходы fi-f-i)-x разрядов регистра 5 основания P,.,-i соединены со входами г-х разрядов первого слагаемого сумматора 3 того же осггованпя, выходы которого соединены через схему приема кода 4 со входом регистра 5 основания Р/,4-1 . Выходы (г+)-х разрядов регистра 5 основания Р„ соединены со входами /-Х разрядов первого слагаемого сумматора 5 того же основания, выходы ЕШторого соединены через элемент И приема кода 4 со в.кодом регистра 5 основания Р„. Выходы первого (младшего) разряда регистров 5 оснований Pi, Ро. Р , - , Р/--ь

РП соединены со входом блока хранения констант 6, все выходы первой выходной шины которого соединены через схемы ИЛИ 2 с соответствуюп1пми входами разрядов второго слагае.мого сумматора 3 оспования Р;. Все выходы второй выходной шины блока храиеипя констант 6 соединены через элементы ИЛИ 2 с соответствующими входами разрядов второго слагаемого сумматора 3 основания р2. Все выходы третьей выходной шииы блока хранения констант 5 соединены через элементы ИЛИ 2 с соответствующими входами разрядов второго слагаемого сумматора 3 основания РЗ. Все выходы (л-1)-й выходной шины блока хранения конетант 6 соединены через элементы ИЛИ 2 с соответствуюиигми входами разрядов второго слагаемого сумматора 5 осиования PJ-I. Вторые входы элементов ИЛР1 2 соединены через первую группу приема кода / со входными информационнымп ппгнами 7. Управляющая шина элемента И приема кода / соединена с управляющим входо.м записи 8. Управляющая nnitfa элементов И приема кода 4 соединена с з правляющей шиной округления 9. Нулевые входы триггеров регистра 5 соединены с управляюи ей шиной 10. Выходы регистров 5 соединены с выходными информационными шинами //.

Устройство для округления кодов осуществляет алгоритм округления кодов, полученный в результате следующих математических действий.

Код системы со смешанным основанием имеет вид

(I)

Л

У а,-, П PJ +0,,

1

1,2, .... nj - число оснований

и величина оснований;

1,2. . . . , п - цифры системы

со смешанным основанием, причем

a,efO,P,,j, ,2я.

Производя деление на основание позиционной системы , а затем отделяя

целые дробные части чисел ,2, - ,п), 55

получив

( 1

-f-sf V - f).

(2)

U 7 ;

где S, F - целая и дробная части числа. Ввиду тождественности запио дробной части числа F МОДХЛКгде г - остаток числа а,принимающий значение О или 1 выражение (2) принимает для дальнейшего унрощения которого используется приближенная замена выра из которого находим значение корректиру ющего кода системы со смещанным осно ванием /С,- (,...,«) по следующим за висимостям; , modPn(5

П р н м е ч а и и е. В изображении двоичных чисел первая двоичная цифра соответствует цифре старшего разряда, последняя двоичная цифра - цифре младшего разряда. Например, двоичное число 110 соответствует десятичному числу 6.

Количество сумматоров 5 и регистров 5 определяется числом исиользуемых оснований. В даином примере оно равно 4. При этом разрядность сумматора 3 н разрядность регистра 5 основания PI равны Iog2/i 2 двочиным разрядам, разрядность сумматора 3 и разрядность регистра 5 осиования PZ равиы og-2 PZ двоичиым разрядам, разрядность сумматора 3 и разрядность регистра 5 основания PZ равны log2P3 3 двоичным разрядам, а разрядность сумматора 5 и разрядность регистра 5 основать Р., равны loga 4 4 двоичным разрядам.

Блок хранения коистант 6 может быть реализован на базе постоянного запоминающего устройства, работаюи1его в режиме считывания информации, или иа базе комбинациоиной схемы. Кодом адреса блока хранения констант 6 являются состояния триггера первого (младшего) разряда всех

регистров 5. (li - значение кода системы со смешанным основанием, соответствующего числу Л; а - значение кода системы со смешанным осиоБдиисм, соответстNвующего округленному числу ; Ki - корректирующий код системы со смешанным основанием. Формула 8 устанавливает зависимость еличины кода системы со смешанным осованием а ,-, соответствующего округлен;;)ViV числу от величины кода системы со смеи 1аиным основанием а,, соответствующего числу Л% и используется в качестве алгоритма округления кодов. П р и м е р. Выберем в качестве кода с разными ио величине основаниями .код системы со смеишнным основанием со следуЮИ1ИМ11 значеииями осиований Pi 3, , , . По формулам (;5ч-7) произведем расчет величины корректирующего кода системы со смешанным основанием Л; (г 1,2,3) (см. табл. 1) и на примере кода системы со смешанным основанием {(Ц, аз, (12, а,) (0101, 110, 100, 001), соответствуюндего целому двоичиому числу Л 1001110100, иокажем методику округления кода системы со смешанным основаиием на одии двоичиый разряд, осуществляемого устройством округления кодов.

(Состояние млядпкмс разряда р регистрл с )cii(i aniii;.v

Я,. il Р

а о л и ц а

Корректируют И ЛВП Ч|1ЫЙ

кол системы со смешанным оснонанием KI но основаниям

К, Р. 3

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАКОВ ЧИСЕЛ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 2014 |

|

RU2557446C1 |

| Устройство для сравнения чисел в системе остаточных классов | 2018 |

|

RU2698413C1 |

| УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ НА ОСНОВЕ ИНТЕРВАЛЬНО-ПОЗИЦИОННЫХ ХАРАКТЕРИСТИК | 2014 |

|

RU2557444C1 |

| Устройство для обнаружения ошибок в кодовой последовательности | 1989 |

|

SU1780191A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1980 |

|

SU959062A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1984 |

|

SU1156058A1 |

| Устройство для обработки информации, представленной в системе остаточных классов | 1990 |

|

SU1743002A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1989 |

|

SU1793546A1 |

| Обратимый преобразователь координат | 1975 |

|

SU590765A1 |

| Преобразователь кода из системы остаточных классов в двоичный код | 1980 |

|

SU947850A1 |

Оби|ее число выходов, составляющие выходные шины блока хранения констант 6, определяется суммой S,,,,x l (log,.0)) где Pi (,2, . . ., п) - величины нспользуемых оснований. Количество выходных шин блока, хранения констант 6 равно (я-1), где п - число используемых оснований. Первый и второй выходы блока хранения констант 6 образуют первую выходную шину блока хранения коистаит 6, третий, четвертый н пятый выходы - вторую выходную шину блока 6, шестой, седьмой и восьмой выходы - третью выходнзю шину блока 6. В блоке хранення констант 6 хранятся двоичные слова корректнрующего кода системы со смешанным основанием, рассчитанные по формулам 65-7). Если число используемых оснований невелико, т. е. двоичный код адреса блока хранения констант 6 является малоразрядным, то двоичные слова корректнр юш,его кода системы со смешанным основанием Ki могут быть сформированы на базе комбинационной схемы. Реализация такой комбннацнонной схемы проводится по известной методике синтеза комбннацнонных схем на основании таблиц истинности булевых функций, следующей из расчетной таблицы 1, где корректирующий двоичный код системы со смешанным основанием /С, является выходом, а состояния триггеров первого (младшего) разряда регистров 5 - входом таблицы нстинности. Так, в соответствии с таблгщей 1 имеем следующие выражения для переключательных функций /г-; /8 в совершенной дизъюнктивной нормальной форме t - ч Q Q Q Q « я J. . о я J А / 5 , ч п - , 4рзр2 PI .-l . .,V-1 PI V pi /;-. . Pi/,:3 : 3, p, V 3; 3;,3,3, /3,3:;X;, , ,:.3,; /., ., . 3, ;:).,3,;(10) /.-S,3,3, 3,; Г:,-): i.,3,; /8 p4p3. Структурная схема блока хранения констант 6 реализована на базе комбинационной схемы. Предварительная работа по занесению кода системы со смешанным основанием в устройство для окрзгления кодов происходит следующим образом. Имиульсом, поданным по управляющей шине 10, производится установка регистров о в нулевое состояние. Затем подаются потенциал высокого уровня на управляющий кол записи S и с задержкой, равной времени срабатывания логических схем, импульс ио управляЕошей шине округления 9. В результате в cyM.vraTOpax 3 производится суммирование двоичного кода системы со смешанным основанием, поступающего по ишнам 7, и двоичного кода нуля регистров 5, прием кодов суммы в регистры 5. Затем управляющий потенциал на управляющей шине записи 8 снимается н застройство для округления кодов готово для округле и1я кода системы со смешанным основанием, так как в каждом регистре оснований Pi 5 находится код системы со смешанным основанием.

Округление кода системы со смешанным основанием устройство производит следуюи,им образом.

Первый импульс, поданный по управляющей iHiuie округления 9, пропзводит занссенне в регистры 5 результатов суммирования двух двоичных чисел, осуществляемые сумматорами 3. Так как в регистре 5 основания Я содержится двоичный код 01, то на входе первого разряда первого слагаемого сумматора 3 осповання Pj присутствует низкий потенциал второго разряда регистра 5 основания РЬ соответствующий нулю во втором его разряде. На входе первого разряда первого слагаемого сумматора - основания PZ присутствует низкий потенциал второго разряда регистра 5 основания Р2 и на входе второго разряда первого слагаемого сумматора 5 основания P-z - высокий потенциал третьего разряда регистра 5 основания Р (в регистре 5 этого основания содержится двоичный код 1001. На входах первого и второго разрядов первого слагаемого сумматора 3 основания РЗ присутствует высокий потенциал второго и третьего разрядов регистра 5 основания РЗ присутствует высокий иотенкиал второго и третьего разрядов регистра 5 основания РЗ (в регистре 5 этого основания содержится двоичный код 110). Нг входах первого и третьего разрядов первого слагаемого сумматора 3 основания Рл присутствует низкий потенциал второго и четвертого разрядов регистра 5 основания Pi, на входе второго разряда первого слагаемого сум,1атора 3 основания Р: - высокий потенциал третьего разряда, регистра 5 основания Р (в регистре 5 этого основания содержится двоичный код 0101). На свободных входах старшего разряда первого слагаемого сумматоров 3 присутствует постоянный низкий потенциал, т. е. на входе второго разряда первого слагаемого сумматора 3 основания Р, на входах вторых разрядов первого слагаемого сумматора 3 оснований Р-2 и РЗ и на входе четвертого разряда первого слагаемого сумматора 3 основания Р4 присутствует низкий потенциал.

Так как на выходе первого разряда регистров 5 оснований Р-, и Pi присутствует высокий потенциал, а на выходах первых разрядов регистров 5 оснований Р, РЗ - низкий потенциал, то на нервом, четвертом, luecTOM и седьмом выходах комбинационной схемы блока хранения констант 6 приС.тствует высокий потенциал, а на остальных выходах - низкий потенциал, что соответствует присутствию на входах вторых разрядов второго слагаемого сумматоров 3 оснований PI, Ра, на входе первого и на входе второго разрядов слагаемого сумматора 5 основания РЗ - высокого Пхотенциала, а на входе первого разряда второго слагаемого сумматора 5 основаПИЯ р., на входах первого и третьего разрядов второго слагаемого сумматора 5 оснозан1 я РЗ на входе третьего разряда второго слагаемого сумматора 3 основания РЗ - низкого потенциала. На выходе второго разряда сумматора 3 основания PI присутствует высокий потенциал, на выходе иервого разряда - низкий потеициал, что соответствует операции суммирования двоичного кода 00, поступившего на вход первого слагаемого, и двоичного кода 10, поступившего на вход второго слагаемого по первой выходной шине блока хранения констант 6. Высокий потенциал присутствует на выходе третьего разряда сумматора 3 основания PZ, на выходах второго и третьего разрядов сумматора 3 основания РЗ и на выходе второго разряда сумматора 3 основания Рл. На остальных выходах этих сумматоров присутствует низкий потенциал.

Переписывая первым импульсом результаты суммирования, произведенные сумматорами 3, в регистры 5, имеем в регистре 5 осиоваи1:я PI - двоичный код 10, в регистре 5 основания Pj - код 100, в регистре 5 основания РЗ - код 110. в регистре 5 основания Р - код 0010, что со .чветствует коду системы со смененным ос1 ОБаиием {я., аз- ао, а ,, (0010. ПО, 100. 10) или округленному на одии двоичный разряд двоичному числу Л 0100111010.

Для округлеи я кода на S двоичных разрядов необходимо повторить работу устройства, подавая S имиу,1ьсов по управ,тяющей шиие округления 9.

При любых других велич нах выбранных оснований и ири любом другом исходном коде системы со смешанным основанием устройство работает аналогично.

Предлагаемое устройство может быть использовано в ЦiЗ., оиерируюшей кодов позиционной системы, для округления кодов позиционной системы, а также в специализированных вычислительных устройствах, оперирующих кодами с разными по основаниями, для округления этих кодов. Частыми случаями кода с разными по величине осиованиями являются код системы со сметпанным основанием, у которого величины основания суть иростые числа, и код факториальной системы счисления, у которого величины основания подчпняются рекуррентной формуле:

-1, Р„ 1. к-1,2,,.../г) Ф о Р м }чт а изобретен ,и я

Устройство ,1ля округления чисел, содержа нго груииу из л комбинационных сумматоров, иервую группу из п элементов И кода, первые входы которых иодс;;ед;:иеиы к управляющей шине заииси, а вторые - ко входным информационным

шинам соответственно, отличающееся тем, что, с целью расширения класса решаемых задач за счет округления кодов с разными ио величине осиованиями, оно содержит групиу (п-1) элементов ИЛИ, грунпу на п регистров приема и передачи кода, вторую групиу элементов И приема кода, блок хранения констант, управляющую шину округлення и щину установки в нуль, причем выходы элементов PI приема кодов первой группы подсоединены соответственно к первой группе входов элементов ИЛИ группы для всех разрядов устройства, кроме старшего, и к первой группе входов комбпнациоиного сумматора для старшего разряда устройства, вторые входы элементов ИЛИ группы подключены к соответствуюшнм выходам блока хранения констант, а выходы элементов ИЛИ группы подсоединены к первой группе входов комбннацпопных сумматоров группы, выходы младших разрядов каждого регистра приема и передачи кода группы подключены соответственно ко второй группе входов комбинационных сумматоров группы, ЕЫходы которых .подсоединены к первым входам соответствующих элементов И приема кода второй группы, вторые входы которых соединены с управляющей шиной округления устройства, выходы элементов И приема и кода второй группы подключены к информационным входам соответствующих регистров приема и передачи кода группы, установочные входы которых подсоединены к установки в нуль устройства, а выходы всех разрядов регистров приема и передачи кода группы являются выходными информациопным т шинами, выходы младших разрядов регистров приема и передачи кода группы соединены с соответствуюпигми входами блока хранения констант.

Источники информации, принятые зо внимание при экспертизе:

Авторы

Даты

1980-10-07—Публикация

1978-07-11—Подача