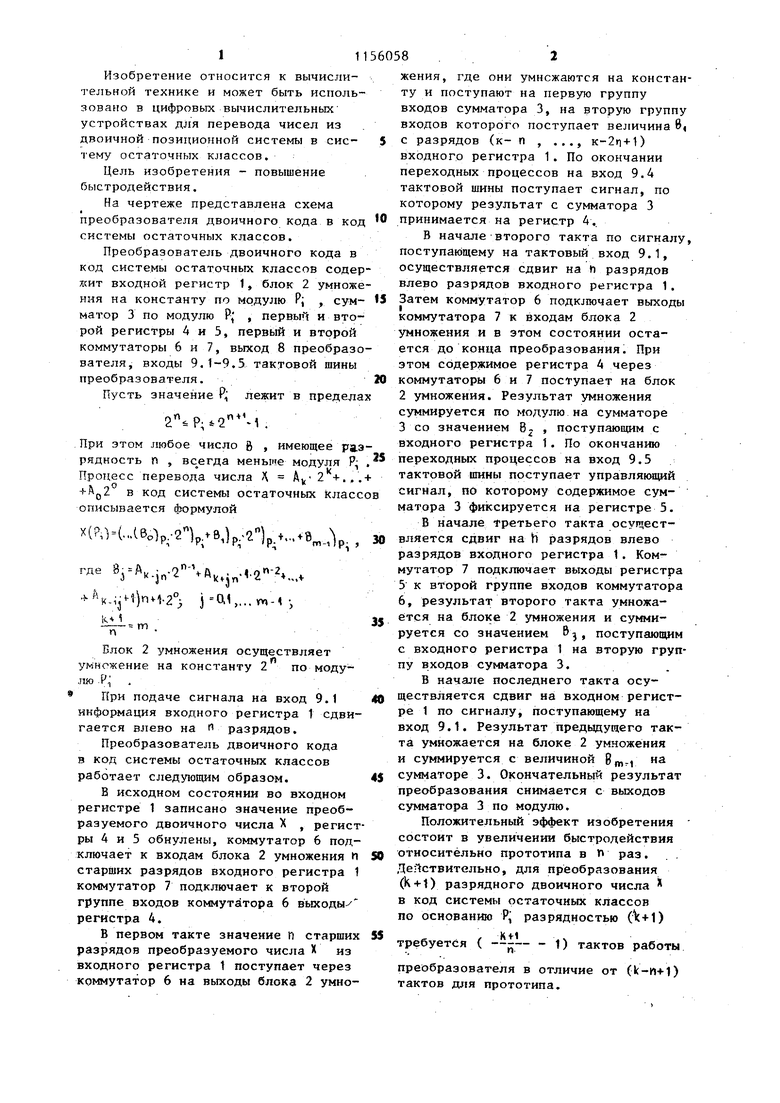

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел из двоичной позиционной cиcтe я l в сиетему остаточных классов. Цель изобретения - повышение быстродействия. На чертеже представлена схема преобразователя двоичного кода в код системы остаточных классов. npeo6pa3OBaTejrb двоичного кода в код системы остаточных классов содер жит входной регистр 1, блок 2 умноже ния на константу по модулю Pj , сумматор 3 по модулю Р , первый и второй регистры А и 5, первый и второй коммутаторы 6 и 7, выход 8 преобразо вателя, входы 9.1-9.5 тактовой шины преобразователя. Пусть значение R; лежит в предела . При этом любое число g , имеющее ра рядность п , всегда меньше модуля Р; Процесс перевода числа Д t(- 2 +., в код системы остаточных Клас описывается формулой X(M4.,.(...B,)p..2..,..v:ip,, где 8j A, - ., .„..,.. ь«к.и).2з j-u... m-4-, Блок 2 умножения осуществляет умножение на константу 2 по модулю PI . При подаче сигнала на вход 9.1 информация входного регистра 1 сдвигается влево на о разрядов. Преобразователь двоичного кода в код системы остаточных классов работает следующим образом. В исходном состоянии во входном регистре 1 записано значение преобразуемого двоичного числа X , регист ры 4 и 5 обнулены, коммутатор 6 подключает к входам блока 2 умножения И старших разрядов входного регистра коммутатор 7 подключает к второй группе входов коммутатора 6 выходы регистра 4. В первом такте значение П старших разрядов преобразуемого числа X из входного регистра t поступает через коьв утатор 6 на выходы блока 2 умножения, где они умножаются на константу и поступают на первую группу входов сумматора 3, на вторую группу входов которого поступает величина В, с разрядов (к- п , ..., к-2п+1) входного регистра 1. По окончании переходных процессов на вход 9.4 тактовой шины поступает сигнал, по которому результат с сумматора 3 принимается на регистр 4.. В начале второго такта по сигналу, поступак щему на тактовый вход 9.1, осуществляется сдвиг на И разрядов влево разрядов входного регистра 1 . Затем коммутатор 6 пoдк roчaeт выходы коммутатора 7 к входам блока 2 умножения и в этом состоянии остается до конца преобразования. При этом содержимое регистра 4 через коммутаторы 6 и 7 поступает на блок 2умножения. Результат умножения суммируется по модулю на сумматоре 3со значением 8- , поступаюпщм с входного регистра 1. По окончанию переходных процессов на вход 9.5 тактовой шины поступает управляннций сигнал, по которому содержимое сумматора 3 фиксируется на регистре 5. 8 начале третьего такта осуществляется сдвиг на Н разрядов влево разрядов входного регистра 1. Коммутатор 7 подключает выходы регистра 5 к второй группе входов коммутатора 6, результат второго такта умножается на блоке 2 умножения и суммируется со значением &з поступающим с входного регистра 1 на вторую группу входов сумматора 3. В начале последнего такта осуществляется сдвиг на входном регистре 1 по сигналу, поступающему на вход 9.1. Результат предьщущего такта умножается на блоке 2 умножения и суммируется с величиной 8тм сумматоре 3. Окончательный результат преобразования снимается с выходов сумматора 3 по модулю. Положительный эффект изобретения состоит в увеличении быстродействия относительно прототипа в раз. Де;Чствительно, для преобразования (К-ь1) разрядного двоичного числа в код системы остаточных классов по основанию Р разрядностью ( + 1) требуется ( - 1) тактов работы преобразователя в отличие от (k-n+l) тактов для прототипа.

I

.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1322483A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1985 |

|

SU1269271A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Преобразователь кодов из системыОСТАТОчНыХ КлАССОВ B дВОичНыйпОзициОННый КОд | 1979 |

|

SU813408A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЛА В КВАДРАТИЧЕСКИЕ ОСТАТКИ | 1992 |

|

RU2029436C1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В КОД СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ, содержащий первый и второй регистры, блок умножения на константу по модулю Р; ( 1,2, .. ., Р ) , сумматор по модулю Р; и (k + O-paa-рядный входовой регистр, причем выходы старших разрядов входного регист ра, где (n-t-1) г lopj Р , соединены с информационными входами первой группы коммутатора, информационные входы второй группы которого соединены с соответствующими выходами второго коммутатора, информационные входы первой и второй групп которого соединены соответственно с выходами первого и второго регистров, информационные входы которых являются выходом преобразователя и соединены с соответствующими выходами сумматора по модулю Р; , входы первого слагаемого которого соединены с выходами блока умножения на константу по модулю Р, , входы которого соединены с соответствующими выходами первого коммутатора, выход (V-n)-ro разряда входного регистра соединен с первым входом второго слагаемого сумматора по модулю Р; , вход сдвига входного регистра, входы приема информации первого и второго регистров, управляющие входы первого и второго коммутаторов соединены с тактовым вхо дом преобразователя, отличающийся тем, что, с целью повышения быстродействия, выходы разрядов с (k-rt-l)-ro по (k-2 О-й входного регистра соединены соответственно с входами с второго по второго слагаемого сумматора C7I по модулю . ф о СП 00

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1984-03-11—Подача