Изобретение относится к обласпи вычисдительиой техиики и лредиазначеио для векторного умножителя синхролно лоступающи.х 3 последовательном долол.н-ительно)М двоичном коде чисел, в которых знак содврж,ится в п-м разряде и сначала постуиают .младшие разряды.

Известно устройство для умножения двух синхронно иоступающих в последовательно донолнятельном двоичноМ коде чисел, е которых знак .содержнтся в п-М разряде и сначала nocTiyinaioT младшие разряды. Устройство содержнт сдвиговый регист/р, ра,спределитель, статический /регистр, а также элементы И ,и последовательно одно;разрядиые сум.маторы. Прн обработке больших массивов данных производительность известного устройства для умножения последовательных л-разрядных кодов значительно уменьшается, так как оно реализует т умножений за 2тп тактов, где л- разрядность последовательного двоичного |КОда, а предлагаемое устройство реализует т умножений за (тп + т + п-2) тактав, где тп тактов приходятся собственно на умножение т нар множимого и множителя, т тактов - на развязку -произведений, а п представляет собой вреМЯ начальной реакции устройства 1.

Наиболее близким техннческнм решением к изобретению является устройство для умножения последовательных «-разрядных двоичных кодов, содержаш,ее (п-1)-разрядный статический регистр, каждый единичный .разрядный вход которого соединен с выходом соответствуюш,его эле.мента И пбгрвой грунпы, а .каждый еди. разрядный выход подключен к одиаму из вхо10дов элемента И второй группы, а также (п-1)-разрядный сдвиговый регистр, нифор|Мационный вход которого соединен с шиной миожимого и другим входом первого элемента И второй , единичный

15 выход -го разряда сдвигового регистра подключен к другО(Му входу (f-M)-ro элемента И второй группы, выход каждого из которых, начиная со второго, соединен с одним из входо1В соот1ветствуюшего последо20вательного одноразрядного сум.матора группы, а также л-разрядный распределитель, ед1ин.ичный выход г-го (разряда .которого подключен .к одному из входов (f-fl)-ro элемента И первой груипы, причем о.дин из 25 входов первого элемента И первой группы и вход распределителя сое.дииены с выходом элемента ИЛИ, один из входов которого подключен к шине правления, а другой вход соединен через элемент задержки с

30 единичным выходом п-го разряда распредедктеля, другие входы элементов И первой прулпы подключены iK тияе множителя, а тзкже два Огтрйггера, .входы .силхро:низации :которых соединены с единичным выходом ()-го разряда ра-спределптеля, причем «нформациаилый вход первого Df триггера подключен к ш,И;не мнон :Н1Мого, а информациойный вход второго Дгтригге)ра соединеп с шиной множителя, единичный выход (п-1)-го (разряда распределителя соединен также с одним ,из входов первого последовательного однораэр ядного сумматора, второй вход которого .подключен к нулевому выходу лоследнего (разряда СДБИТОiBoro регистра, а выход соединен с одним из входов первого элемента И, второй вход которого подключен iK единичному выходу второго /)(-триггвра, а выход .соединен с одним из входов второго последовательного одноразрядного сумматора , Эти устройства позволяют 1реал1изовать векториое умножение синхронно поступающих в последовательном .дополнительно,м дво ичном коде чисел. Целью «зобретения является расширение функциональных возможностей устройст.ва для умножения последовательных п-разрядных ДВОИЧ.НЫХ кодов за счет р:еал|изадии векторного умножения. Эта цель достигается за счет того, что ycTipoHCTBO для умножения .последовательных «-разрядных двоичных кодов, содержит «-(разрядный распределитель, (п-1)разрядный сдвиговый 1регистр, .первую и вторую группу элементов И, группу иоследовательных одно,раз|рядных сумматоров, первый и второй ОгТрИГгеры, элемент ИЛИ, элемент задержки, иервый последовательный одноразрядный сум1мато1р, первый элемент И, второй последовательный одноразрядный сумматар, (п-1)-разрядный статический регистр, Каждый единичный разрядный вход которого соединен с выходом соответствующего элемента И первой группы, а каждый единичный разрядный выход подвключен .к иервому входу соответствующего элемента И второй группы, информаиио н:ный .вхо.д (л-1)-разрядного сдвигового регистра соединен с шииой множимого :И вторым входо:м первого элемента И второй группы, единичный выход г-го разряда сдвигового регистра подключен жо второму входу (t-t-l)-ro элемента И второй группы (,2,..., п-1), выход (t+l)-ro элемента И второй пРУПпы соединен с первым зходом t-ro последовательного одноразрядного Сумматора группы, единичный выход i-ro разряда л-разрядного распределителя подключен к первому входу (i4-l)-ro элемента И первой гр.уппы, причем первый вход парного элемента И .первой группы ,и вход распределителя Соединены с выходам элемента ИЛИ, О.Д1И.Н .из ВХОДОВ которого подключен К Щ;ине управления, а другой вход по.дсоединен к элемент} задержки, выход которого связан с единичным выходо м л-го разря.да распределителя, вторые входы элементов И первой группы подключены к К1|ине множителя, а входы синхронизации иервого и второго /)(-тр,иггеров соединены с единичным выходом (п-1)-го рааря.да распределителя, причем информационный вход первого О.триггера подключен к шине 1множ;имого. а информационный вход второго /)гтриггера соединен с шиной множителя, единичный выход (л-1)-го разряда распреде.тителя подключен к иерваму в.ходу первого после.довательного одноразрядного сумматора, второй вход которого ио.дключен к нулевому ВЫХОД) последнего раз1ряда сдв.игового регистра, а выход соединен с первым входом первого элемента И, второй вход которого подключен к единичному выходу второго Огтриггера, а выход соединен с первым выхо.дом второго ПоследОВательного одноразрядного сум матора, третью группу элементов И, группу элем-ентов НЕ, три дополнительных последовательных одноразрядных сумматора, TipiH дополнительных эле:мента PI и один дополнительный элемент НЕ, / 5-триггер и -разрядный элемент задерж1ки. Нулевой вход г-го раз1ряда статического регистра соединен с единичным выходом (i-3)-го разряда распределителя, пр(ичем нулевой вход napiBoro раз1ряда статического регистра подключен к единичному выходу (л-1)-го разряда распредел.ителя, нулевой выход второго разряда статического регистра соединен с единичны1М выходом л-го .разряда распределителя, а н левой вход третьего разряда статического регистра подключен к выходу-элемента ИЛИ. Шина множителя через последовательно соединенные л-разрядный элемент задержки и дополнительный элемент НЕ связана с иервьйм входом первого дополнительного последовательного сумматора, второй вход .которого подключен .к единичному выходу (п-1)-го разряда распределителя, а выход подключен к первому входу первого дололнительного элемента И, второй вход которого .подсоединен к единичному выходу первого / гтриггера, а его выход соединен с первым входом второго дополнительного последовательного однораз|ря:дного сумматора, второй .вход которого подключен « выход)- второго последовательного однораз1рядного сумматора, а выход соединен с первым входом третьего дополнительного последовательного одноразрядного сумматора, а (ВЫХОД соединен с первым входом третьего дополнительного .последовательного одноразрядного c MiMaTOpa, другой вход которого подключен « выходу второго дополнительного элемента И, а выход соединен с первым входом третьего дополнительного элемента И, второй вход которого подключен к единичному выходу ь/ 5-тр1Иггера, а зыход соединен с шиной произведения, Нулавой и единичный входы / 5-гр:иггера соединены соответственно с единичными выходами (п-2)-го н (п-Г)-го разрядов распределителя. Входы второго допо..ч:ительного элемента И подключены « ед1иннч,ны-м выходам /)гтриггеров и единичному выходу (п-3)-го разряда распределителя. Первый вход i-ro элемента И третьей группы лодсоединен ,ко входу соответстзующего элемента НЕ группы, выход которого соеди.нбн с единлчиым выходом (i-1)-то разряда распределителя, а другой вход подключен к выходу (i-1)-го последовательного одноразрядного су1М1матора груплы, а выход соединен со вторым входом г-го последовательного одноразрядного сумматора группы. Первый .вход первого элемента И третьей группы через соответствующий элемент НЕ группы соединен с выходом элеМента ИЛИ, другой вход подключен к выходу первого элемента И второй группы, а выход соединен со вторым входом .первого последо(вательного одноразрядного сумматора пруппы. Выход последнего элемента И третьей группы подключен .ко второму входу второго .последовательного одноразрядного сумматора. Нулевые входы Diтр:игге|ров соединены с единичным .выходом (п-2)-го разряда распределителя.

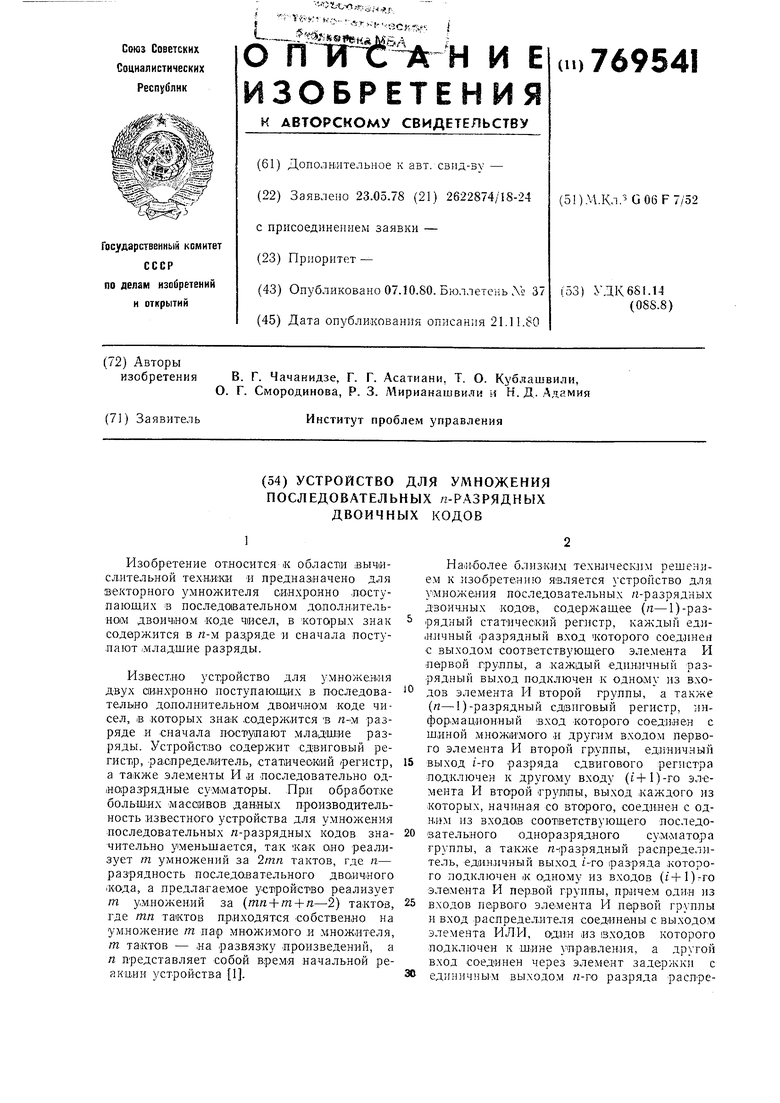

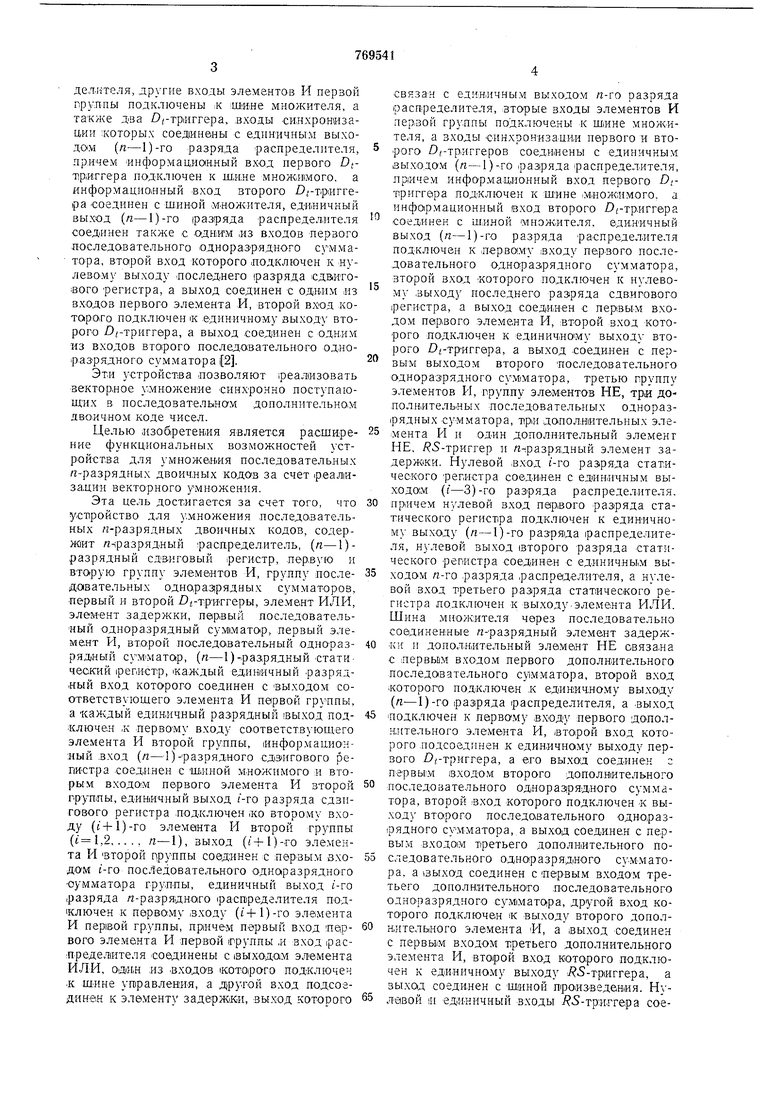

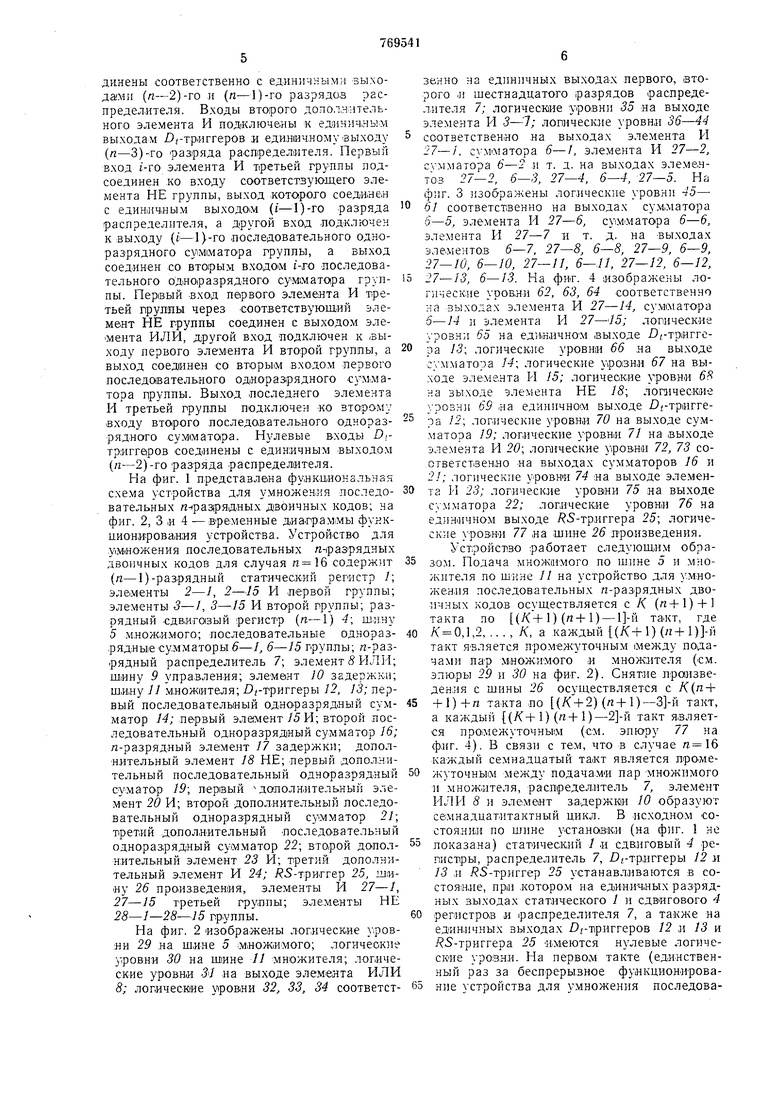

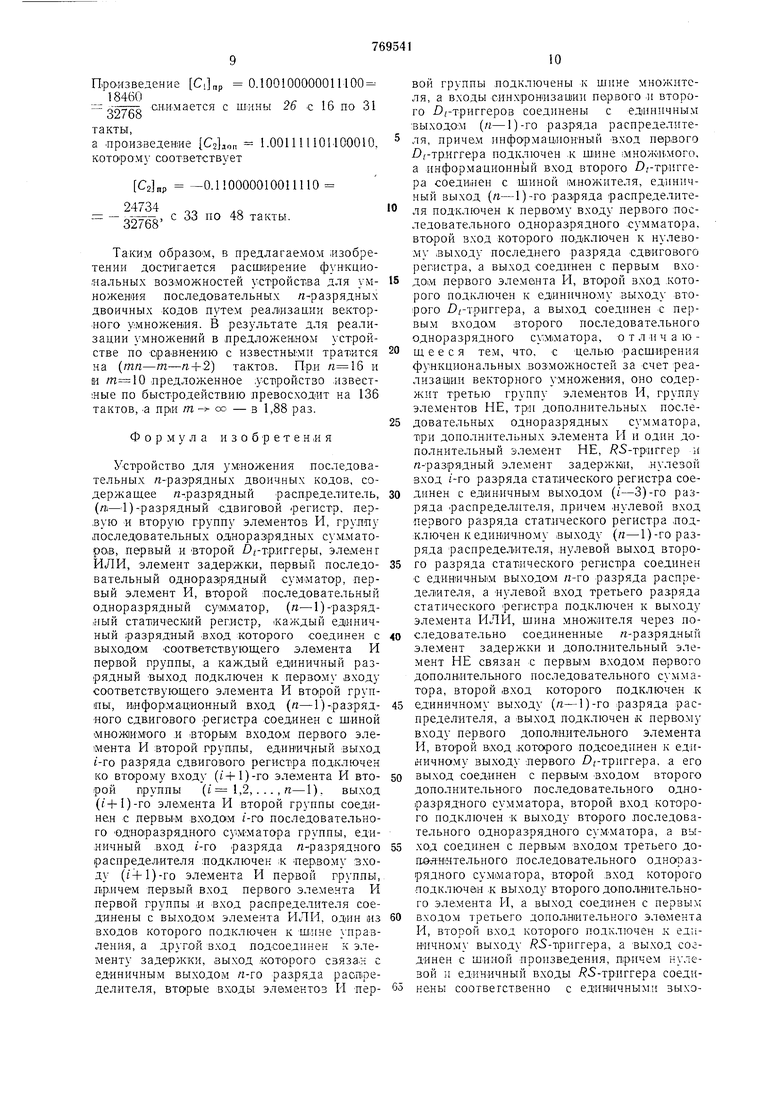

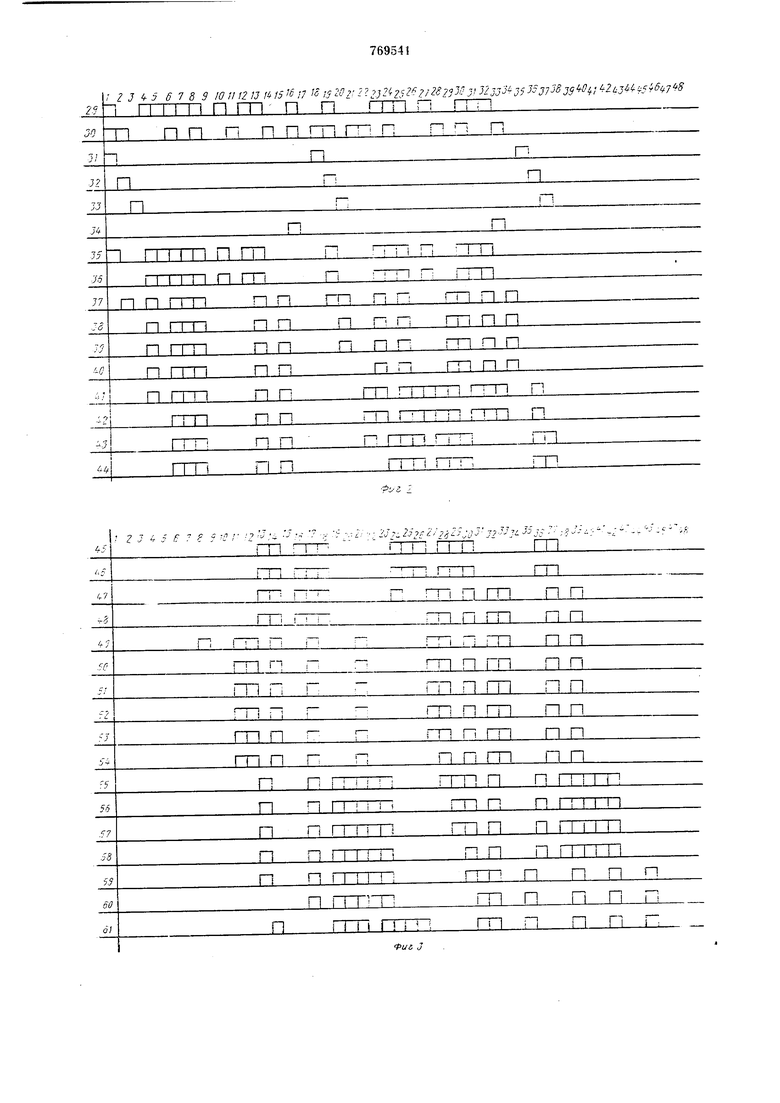

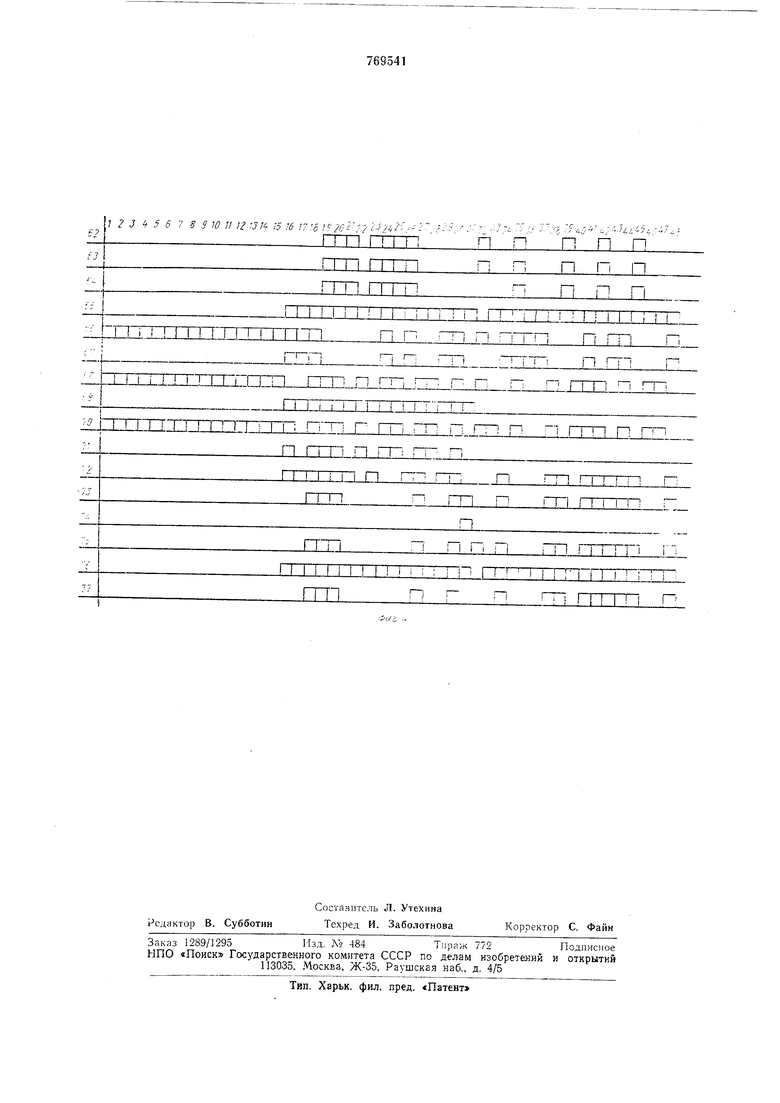

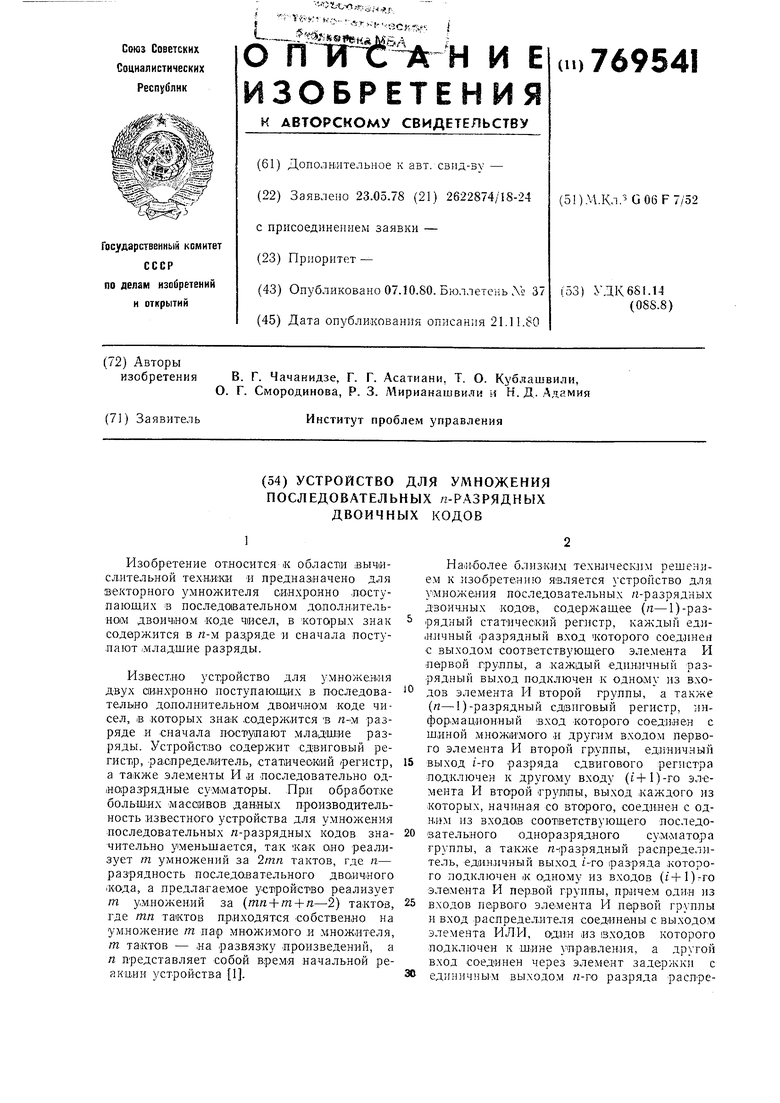

На фиг. 1 представлена функциональная схема устройства для умножен..ия последовательных п-|раз|рядных двоичных кодов; на фиг. 2, 3 и 4 - временные диа.грам1мы фу.нкционировамия устройства. Устройство для .умножения последовательных ге-разрядных двоичных кодов для случая содержит (п-1)-разрядный статический регистр /; элементы 2-У, 2-15 И первой группы; элементы 3-/, 3-15 И второй лруппы; разрядный .сдвиговый регистр (п-1) 4; ши.ну 5 М.НОЖИ.МОГО; последовательные одноразрядные сумматоры б-/, 6-75 группы; п-разрядный распределитель 7; элемент S ИЛИ; шину 9 упра.вления; элемент 10 задержки; шину 11 м.нож1ителя; Дгтриггеры 12, 13; первый последовательный одноразрядный сумматор первый эле1мент/5 И; второй последовательный одноразрядный сумматор 16; п-разрядный элемент 17 задержки; дополнительный элемент 18 НЕ; .первый допол.ннтельный последовательный одноразрядный суматор 19; первый дополнительный эле.мент 20 И; второй дополнительный последовательный одноразрядный сзмматор 21; третий .дополнительный последовательный одноразрядный сумматор 22; второй дополнительный элемент 23 И; третий дополнительный элемент И 24; / 5-три.ггер 25, длину 26 произведения, элементы И 27-/, 27-15 третьей группы; элементы НЕ 28- -28-15 лруппьь

На фиг. 2 изоб.ражены логические дровяи 29 на шине 5 ;множимого; логичеокне уровни 30 на шине 11 множителя; л.огические уровни 5/ на выходе элемента ИЛИ 8; логическ1ие уровни 32, 33, 34 соответстзенно на единичных выходах первого, (второго л шестнадцатого разрядов распределителя 7; логические уровни 35 на выходе элемента И -5-7; логические зровни 36-44 соответственно на выходах элемента И 27-/, сумматора 6-/, элемента И 27-2, сумматора 6-2 ,и т. д. на выходах элеменТО.З 27-2, 6-3, 27-4, 6-4, 27-5. На . 3 изображены логические уровни 4i)- 61 соответст1венно на выходах сум.матора 6-5, элемента И 27-6, сум матора 6-6, элемента И 27-7 и т. д. на выходах элементов 6-7, 27-8, 6-8, 27-9, 6-9, 27-10, 6-10, 27-11, 6-11, 27-12, 6-12, 27-13, 6-13. На фиг. 4 изображены логические уровни 62, 63, 64 соответственно на выходах элемента И 27-14, сум1матора 6-14 и элемента И 27-45; логические уровн; 65 на единичном выходе 1)гтриггера 13; логические уровни 66 на выходе сумматора 14; логические уровни 67 на выходе элемента И 15; логические уровни 68 на выходе элемента НЕ /5; логические ypOBHji 69 на единичном выходе Дг-триггера 12; логические уровни 70 на выходе сумматора 19; логические уровни 71 на выходе элемента И 20; лопические уровни 72, 73 соответственно на выходах сумматоров 16 и логическ;1е уровни 74 на выходе элемента И 23; логические уро.вни 75 на выходе сул матора 22; логические уровни 76 на един1ичном выходе .иггера 25; логические чровни 77 на .шине 26 про.изведения.

Устройство работает следуюшим образом. Подача множимого по шине 5 и множителя по шине //на устройство для умножен.ия последовательных /г-разрядных двоir-iHbix кодов осушествляется с К, (гг+1) + такта по () (п+1) - та.кт, где Л: 0,1,2, ... , Л , а каждый (/С-г 1)(/г+1)-й такт является промежуточным 1между подачами пар множ.имого и множителя (см. элюры 29 и 30 на фиг. 2). Снятие произведения с шины 26 осуидествляется с К(п+ }+п такта по (/( + 2) (п+1) такт, а каждый (К-}-) (п+) такт является про.мел уточным (см. 77 на фиг. 4). В связи с тем, что в случае каждый семнадцатый такт является промежуточным между подачами пар множимого и мнол ителя, распредел.итель 7, элемент Р1ЛИ 3 и элемент задержк1И 10 образуют семнадцат.итактньш цикл. В исходном состоянии по шине установки (на фиг. 1 не показана) статический / и сдвиговый 4 релист1ры, распределитель 7, /)гтриггеры 12 и 13 и jRS-триггер 25 устанавливаются в состояйие, при .котором на единичных разрядных выходах статического / и сдвигового -/ регистров и распределителя 7, а также на единичных выходах DriipHrrepos 12 и 13 и / 5-триггера 25 имеются нулевые логические урозн.и. На первом такте (единственный раз за беспрерывное функционирование устройства для умножения последовательных л-разрядных двоичных кодов), по шше 9 правлен,ия подается ед иннчный лолический уровень, -распределение которого «а единичных выходах раодределителя 7 начинается со второго такта (см. эпюры 32, 33 ,и 34 на фиг. 2). При этом на (/+1)-м такте единичный логический уровень с еди1НИЧНОГО выхода j-ro разряда раСпредел:ителя 7 через элемент И 2(i+) осуществляет зались лорического фовня (t+Г)-го разряда ;множителя ;В {г+1)-й разряд регистра / |И установку в нулевое состояние (t + 3)-ro (разряда последнего. Аналогично на каждом Л (л+1) + та,кте единичный логический уровень с .выхода элемента ИЛИ 8 через элемент И 2-/ осуществляет запись логических уровней лервых разрядов множителей в первый разряд регистра ;/ и установщ (В нулевое состояние т)ретьего разряда последнего. В результате этого лервый IMHOжитель за () тактов запишется в регистр 1. Аналолично затись .второго множителя в регистр 7 .начинается с 18-го такта и т. д. Логические уровни имножителя через регистр / и множи.мого через ;Щ;ину 5 и регистр 4 подаются на входы элементов И 3-/, И 3-2, . . ., И 3--15, с ВЫХОДОВ которых снимаются частные произведения. Последние через элементы И 27-/, И 27- 2,.. . , И 27-14 суммируются на .сумматорах 6-/, 6-2, . . ., 6-14 (см. эпюры .с 35 л о 44 ,на фиг. 2, эпюры с 45 ио 61 на фиг. 3 ,и эпюры 62 м 63 на фиг. 4). Результаты у1множений снимаются с выхода элемента И 27-15 (о.м. эпюру 64 на фиг. 4). Логические уровни с выхода элемента ИЛИ 8 и единичных .выходов распределителя 7 через эл-е.менты ИЕ , НЕ 25-2, .. . , НЕ 2S-15 управляют элементаМИ И 27-1, PI 27-2, . . ., И , осуществляя развязку между произведениями лутем отбрасывания младщих п разрядо1В. На каждом (К, + (л+1) - такте с единичного выхода 16пго разря.да распределителя 7 на вход синхронизации / г-триггера 3 подаегся единичный лопичеок1ий уро-вень. Вследствие этого .на ука.зан.ных тактах :В irTpJirreре 13 ф.иксируются знак1И множителей. В случае отрицательного .множителя .0,-триг.гер 13 устанавливается в единичное состояиие (о.м. эпюру 65 на фиг. 4). В рез льтате этого, соответствующий поправочный член, который образуется на .выходе сум.матора 14 (см. эпюру 66 на фиг. 4), через элемент И 15 (см. эпЮ|ру €7 иа .фиг. 4) .на сум.маторе 16 (см. эпюру 72 на фиг. 4) сумм.ируется с результато|М умножения, которое снимается с :выхо.да элемента И 27-15 и в этом случае представляет собой псевдопроизведение. В очередном цикле ic единичного выхо.да (п-2)-.го разряда распределителя 7 .Of-TpiHrrep 13 устанавливается в исходное (.нулевое) состояние. Аналогично на каждом (/C-f 1) (л+.1) такте с е.д.иничного выхода 16-го разряда .раСпределлтеля 7

на вход синхроЕизации / /-триггера 12 подается единичный логический уровень. Вследствие этого на указанных тактах в Огтриггере 12 фиксируется знаки множимых. В случае отр.ицательного множ1гмого irTpHrrep / уста.на;вливается в единичное состояние (см. эпюру -69 ла фиг. 4). В результате этого соответствующий попра.вочный член, который образуется на вы.ходе cvMiMaTOipa 19 (см. эпюру 70 на фиг. 4), че.рез элемент И 20 (см. эпюру 7/ на фиг. 4) на суМ.маторе 21 (см. эпюру 73 на фиг. 4) суммируется с результатом умножен.ия, который снимается с выхода сум.матора 16 и в ЭТ01М случае представляет собой псевдопроизведение. В очередно.м цикле с единичного выхо.да (д-2)-го разряда раслределителя 7 .0;-триггер 12 устанавливается з ис.од:ное (нулевое) .состояние. Элемент И

23(см. эпюру 74 на ф.иг. 4) на каждом (/С+2) (n-f.l)-3J-M в случае отрицательных :.множителей и .мпож.имых вььрабатывают единичный логический урове;1Ь, который на сумматоре 22 (см. эпюру 75 на фиг. 4) суммируется с результатам умножения, который снимается с выхода сум.матора 21 н в этом случае представляет собой |Псевдопроизведен.ие. С единичного выхода (п-;1)-го разряда распределителя 7 RSтриггер 25 на каждо.м {К(п+1) такте устанавдив.ается .в единичное состоя.ние (см. эпюру 76 на фиг. 4) и через элемент И

24разрещает подачу логических уровней произведен|ИЙ на ш..ину 26 (см. эпюру 77 на ф.иг. 4). Возврат 5-тр.иггера 25 в исхо.дное (нулевое) состояние .и осуществление тем caiMbiM развязки .между произведен1ИЯ МИ осуществляется на каждом (К+1)(п + + такте с единичного выхода {п-2)-го разряда распределителя 7. Для примера на фиг. 2, 3 и 4 даны временные д.иаграм1мы функционирования устройства для )г :ножения последовательных л paзрЯДНЫХ двоичных кодов для случая VMKO25863

жения множи.мого .7-6 на .множиo.i/bo

23389,„

S| заданных 16-разоядкыми

тель DI - оИ/оо

дополн.ительными .кодами

А,до„ 1.001101011111001 и 1.010010010100011,

.множ.имого .2 nnvTTo множитель

27557

.„, заданных 16-разрядньгми дополов/оо

п-ительными кода.ми

0.111004011100010 и l.OOlOilOOOiOllOll. Про.изведение 0.100100000011100 8460-. -- oovco снимается с zo с Ib по 31 о//об а .произведение 1С,до1т 1.00111 ПОЫОООЮ, котором}- соответствует 2 „р -0.110000010011110 24734 .. - 32768 ° 48 такты. Таким образОМ, в предлагаемом изобретении достигается расширение функциональных возможностей устройства для умножения последовательных «-разрядных двоичных кодов путем реализации векторного умножения. В результате для реализации умножений в предложенном устройстве по сравнению с известными на (тп-т-п+2) такто.в. При и и иредложенное Лст1ройство извест1ные по быстродействию превосходит на 136 тактов, -а при m - ее. - в 1,88 раз. Формула изобретеН|ИЯ Устройство для умножения последовательных л-разрядных двоичных кодов, содержащее «-разрядный распределитель, (п-4)-разрядный сдвиговой регистр, пер.вуЕО и вторую группу элементов И, группу последовательных одноразрядных сумматоров, первый и Второй гтриггеры, элемент ИЛИ, элемент задержки, первый последовательный однораз)рядный сумматор, первый элемент И, второй последовательный одноразрядный сумматор, (п-1)-разрядный статический регистр, каждый единичный разрядный .вход которого соединен с выходом соответст.вующего элемента И перв.ой лруппы, а каждый единичный разрядный .выход подключен к первому входу соответствующего элемента И второй группы, информационный вход («-1)-разрядного сдвигового .регистра соединен с щ.иной множимого и .вторым входом первого элеМента И второй группы, единичный выход t-ro разряда сдвигового регистра подключен ко второму входу (t+l)-ro элемента И второй группы (,2, ...,п-1). вы.ход (t-bl)-ro элемента И второй группы соединен с первым входам /-го последовательного одноразрядного сумматора группы, единичный вход г-го .разряда л-разрядного |распреде.л.ителя подключен ;к -первому входу (г+1)-го элемента И первой группы, причем первый вход первого элемента И первой группы и вход распределителя соединены с выходом элемента ИЛИ, один из входов которого подключен к ш.ине управления, а другой вход подсоединен к элементу задержки, выход которого связа.н с единичным выходом л-го разряда распределителя, вторые входы элементов И первой группы подключены к щине множителя, а входы синхрона зац1Ш первого и второго jDrTpnrrepOB соединенны с единичным выходом (п-1)-го разряда распределителя, причем информационный вход первого Z rTpHrrepa подключен .к щине ;множ..и.мого, а информационный вход второго /)гтр.пггера соединен с шиной множителя, единичный выход (п-1)-го разряда распределителя подключен к первому входу первого последовательного одноразрядного сумматора, второй вход которого поД|Ключен к нулевому выходу последнего разряда сдвигового регистра, а выход .соединен с первым входом первого элемента И, второй вход .которого подключен к единичному выходу второго 1)/-триггера, а выход соединен с первым входам второго последовательного одноразрядного сумматора, о т л и чающееся тем, что, с целью .расщирения функциональных возможностей за счет реалнзашни векторного умножения, оно содержит третью группу элементов И, группу элементов ИЕ, дополнительных последовательных одноразрядных сум.матора, три дополнительных элемента И и один дополнительный элемент НЕ, / S-Tpairrep и «-разрядный элемент задержки, нулевой вход г-го раз.ряда статического регистра соединен с единичным выходом (г-3)-го разряда .распределителя, причем .нулевой вход первого разряда статического регистра .подключен к единичному выходу (п-1)-го разряда расиределителя, нулевой выход второго разряда статического регистра соединен с един1ич.ным выходом п-го разряда распределителя, а нулевой вход третьего разряда статического регистра подключен к выходу элемента ИЛИ, щина множителя через последовательно соединенные «-разрядный элемент задержки и дополнительный элемент ИЕ связан с первым входом первого дополнительного последовательного сумматора, второй вход которого подключен к единичному выходу (п-1)-го разряда распределителя, а выход подключен к первому входу первого дополнительного элемента И, второй В.ХОД .котсхрого подсоединен к единичному выходу первого гтриггера. а его выход соединен с первым входом второго дополнительного последовательного одноразрядного сумматора, второй в.чод которого подключен -к выходу второго последовательного одноразрядного сум.матора, а выход соединен с первым входом третьего дополнительного последовательного одноразрядного суммагора, второй вход которого подключен -к выходу второго дополнительного элемента И, а выход соединен с первым входом третьего допол1Н1Ительного элемента И, второй вход которого подключен к единичному выходу / 5--11риггера, а вы.ход соединен с щиной произведения, причем нулевой и единичный входы 5-триггера соединены соотвегственно с единичными выхои

да-мя ()-го и (га-1)-го разрядов распределителя, входы второго дополнительного элемента И подключены к единичдЫМ выходам irTp.Hrrepa и единичному выходу («-3)-го разряда распределителя, первый вход 1-го элемента И третьей группы подсоединен ко входу соответствующего элемента НЕ группы, выход которого соединен с единичным ВЫХОДО.М (i-1)-го разряда расп.ределителя, а другой вход подключен к выходу (i-1)-го последовательного одноразрядного cyMMaToipa группы, а выход соединен €0 вторым входом i-ro последовательного одноразрядного сум1матора группы, П1ричем первый вход лер.вого элемента И третьей группы через соотеетствующий элемент НЕ группы соединен с выходом элемента ИЛИ, другой вход подключен к вы769541

12

ходу первого элемента И второй группы, а выход соединен со вторым входам первого последовательного одноразрядного суММатора группы, выход последнего элемента И третьей группы подключен ко второму входу второго последовательного одноразрядного сумматора, причем нулевые входы Df триггеров соедине1ны с единичным выходом (л-2)-го разряда расвределителя.

Источники информации, принятые во внимание при экспертизе:

1,R. F. Lyon. Twos Complement pipeline multipliers, IEEE Trans. Commun, 24 № 4 1976.

2.Авторское свидетельство по заявке 2409122/18-24, кл. G 06 F 7/39, 29.09.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения п-разрядных двоичных кодов | 1976 |

|

SU690478A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для умножения чисел | 1979 |

|

SU817702A1 |

| Устройство для умножения п-разрядных чисел | 1978 |

|

SU734683A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения | 1978 |

|

SU769540A1 |

П ППП П ГЛ ГП П

П

JQ.

J

П

J4

тп П m

.И

J5

Л1

I м I i I П ГП

J.5

П П ГП П

J7

П П ГГП

П П

П rm

П П

и

П П

JIL

П п.

jn.

П П

п

4Х1

LEL

ГП П Г

П

П ГГ

П

П Mill

П

П

П П г

и

и

П

П

JIL

П

JILEL

1 П П

m П П

П п.

лп

Г П

ГП.

П П

m П ГП П П

-П П m П П

m П П

ПП П ГТ

JZLEL

П ГЛ П П

П г.

м м I 1

П П г

П

1 П

П П П

П

Пd

П

по.

i i Г I iTTTTTn li: П ; D

ixn

П

n

m П rri

П n г

I I

II

Авторы

Даты

1980-10-07—Публикация

1978-05-23—Подача