(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел | 1980 |

|

SU920713A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

Изобретение относится к вычисли тельной технике и может быть ИСПОЛЬ зовано при построении цифровых вычи лительных машин последовательного действия. Известно устройство для умножени последовательного типа, содержащее регистры множителя, множимого и про изведения, одноразрядный сумматор последовательного.действия, блок управления, логические элементы Ни ИЛИ И . Однако принцип работы такого уст ройства не позволяет в полной мере использовать в нем динамические регистры с большой степенью интеграции, что приводит к росту аппаратур ных затрат и габаритов. Наиболее близким -к предлагаемому является устройство для умножения чисел, содержаще - регистры множителя множимого и произведения, одноразрядный сумматор последовательного действия, триггеры, логические элементы И и ИЛИ. В этом устройстве пр изведение и знак формируются на двух шинах, что требует дополнительной схемы для формирования последователь ного кода результата на одной шине ИНедостатки устройства - низкое быстродействие и большие аппаратурные затраты. Цель изобретения - упрощение устройства и увеличение быстродействия его. Поставленная цель достигается тем, что устройство для умножения чисел содержит регистры, сумматор, триггер, элементы И и элемент ИЛИ, причем вход первого регистра соединен с выходом сумматора, выход первого разряда второго регистра соединен с первым входом триггера, второй вход которого соединен с первой тактовой шиной устройства, а выход - с первыми входами первого и второго элементов И, выходы которых подключены соответственно к первому и второму входу сумматора, выход второго разряда первого регистра соединен с первым входом третьего элемента И и первым входом четвертого элемента И, выход которого соединен со вторым входом сумматора, выход третьего элемента И соединен с первым входом элемента ИЛИ, выход которого подключен ко входу второго регистра; второй разряд которого соединен с первым входом пятого элемента И, выход которого соединен со вторым . входом элемента ИЛИ, вход третьего регист-ра соединен со вторым входом второго элемента И, первым входом шестого элемента И и выходом третьего регистра, выход шестого элемента И соединен с первым входом сумматора, второй вход четвертого элемента И соединен с выходом седьмого элемента И, первый вход которого соединен со вторыми входами соответственно первого, второго, третьего, пятого и шестого элементов И и второй тактовой шиной устройства, третьи входы второго и третьего элементов и второй вход седьмого элемента И соединены с управляющим входом устройства

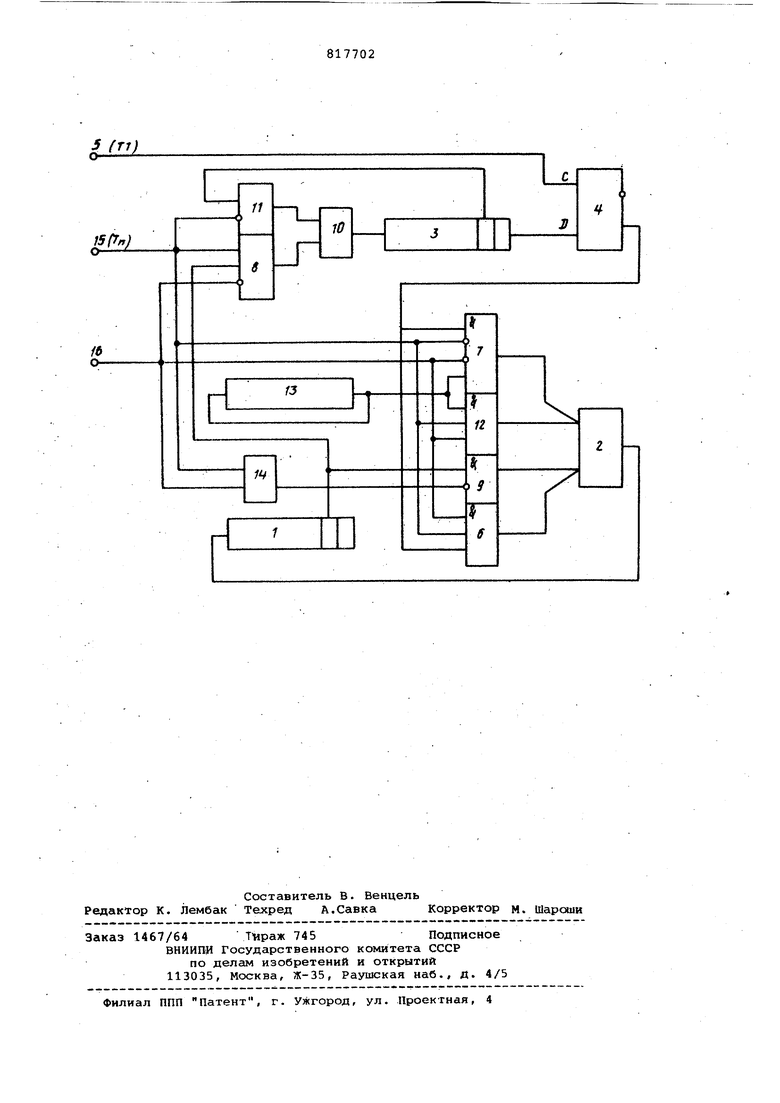

В таблице представлено состояние регистров и элементов устройства при вычислении произведения 0,110 х X 1,011 1,010010; на чертеже функциональная схема предлагаемого устройства для умножения чисел.

Устройство содержит первый регистр 1 (произведения), сумматор 2, второй регистр 3 (множителя).триггер 4, первую тактовую шину 5, первый второй, третий и четвертые элементы И 6, 7, 8 и 9, элемент ИЛИ 10, пятый и шестой элементы И 11 и 12, третий регистр 13 (множимого), седьмой элемент И 14, вторую тактовую шину 15 и управляющий вход 16 устройства.

Устройство содержит п-разрядные регистры 1 произведения, множителя

3и множимого 13 (п-разрядность сомножителей, включая знаковый разряд) одноразрядный сумматор 2 последовательного действия, выход которого соединен со входом регистра 1 произведения, синхронизируемый D-триггер

4умножения, D-вход которого подключен к выходу первого разряда регистра 3, С-вход - к первой тактовой шине 5. Выход триггера 4 через элемент И 6 подключен ко второму входу сумматора 2, а через второй элемент.И 7 связан с первым входом сумматора 2, выход второго разряда регистра 1 через элемент И 8 соединен со входом элемента ИЛИ 10, выход которого подведен ко входу регистра 3. Первый вход элемента И 11 связан с выходом второго разряда регистра 3,выход и вход регистра 13 объединены и через элементы И 7 и 12 соединены с первым .входом сумматора 2, выход второго разряда регистра 1 через элемент И

:9 подключен ко второму, входу сумматора 4, вход ЗАПРЕТА элемента И 9 к Выходу элемента И 14, входы элементов И б, 8, 12и14и входы ЗАПРЕТА элементов И 7 и 11 - к тактовой шине 15, входы элементов И б, 12 и 14 и входы ЗАПРЕТА элементов И 7 и 8 подведены к управляющему входу 16 устройства.

Работа устройства осуществляется по циклам, равным циклам циркуляпии

информации в регистрах 1, 3 и 13, i длительность которых равна п тактов. Когда на выходах первого разряда динамических регистров в режиме хранения находятся первые разряды записанных в них чисел, на первой тактирующей шине 5 появляется единичный сигнал Т1, соответствующий началу цикла Когда на выходах первого разряда находятся последние разряды чисел, на второй тактирукмцей шине 15 появляется единичный сигнал Т, соответствующий концу цикла.

Умножение двух чисел осуществляется за п циклов. На время последнего п цикла умножения на управляющем входе 16 устройства действует единичный сигнал. В исходном состоянии в регистрах 1, 3 и 13 записаны прямые коды множителя и множимого младшими разрядами вперед, знаки в последних п-х разрядах,, в регистре 1 записан нулевой код .(цепи записи и хранения кодов в регистрах на .чертеже не показаны) . На время умножения цепь циркуляции регистра 3 замыкается со второго разряда через эле.менты 11 или 10 на свой вход. В последнем такте каждого цикла цепь циркуляции размыкается сигналом Tf, (шина 15), поступающим на вход ЗАПРЕТА элемента И 11. Такая ко 1утация цепи циркуляции регистра 3 обеспечивает поступление на D-вход триггера 4 умножения в первом такте каждого 1-го цикла умножения (i 1,2,...,п) i-го разряда множителя и записи его по сигналу Т1 (шина 5) на триггер 4, который управляет выдачей на вход сумматора 2 кода множимого в i-м цикле умножения. В первых (п-1) циклах умножения по единичному состоянию триггера 4 на первый вход сумматора 2 через элемент И 7 поступает код множимого, по нулевому- состоянию - нулевой код, в пос-. ледних тактах сигналом Т (шина 15) блокируется поступление на вход сумматора 2 знака множимого.

Цепь циркуляции регистра 1 в пер-вых (п-1) циклах умножения замыкается со второго разряда через элемент И 9 и через сумматор 2 на свой вход. Такая коммутация регистра 1 обеспечивает запись в нем сформированных на сумматоре 2 частичных произведений и подачу на второй вход сумматора 2 в каждом i-м цикле (i-l)-ro частичного

произведений, сдвинутого на (i-l) разрядов вправо. Вьщвигаемая вправо младшая цифра i-го частичного произведения в п-м такте каждого i-го цикла (кроме последнего п-го цикла)

О через элементы И 8 и ИЛИ 10 записывается в освобождающиеся разряды регистра 3 . Блокировка такой записи в п-м цикле осуществляется сигналом с шины 16, поступающим на вход ЗАПРЕТИ

5 элемента И 8, и объясняется тем, что последний n-ый цикл является циклом обработки знаков. В последнем п-м цикле подача мно жимого на первый вход сумматора 2 ч рез элемент И 7 блокируется единичным сигналом с шины 16, подаваемым на вход ЗАПРЕТА элемента И 7, в п-м такте по сигналу Т f, через элемент И 12 на первый вход сумматора 2 посту пает знак множимого. Знак множителя в п-м такте п-го цикла поступает на второй вход суглматорб 2 с выхода триггера 4 умножения через элемент И 6. Следовательно, на выходе сумматора 2 в п-м такте последнего цикла формируется знак результата как сумма по модулю два знаков множителя и множимого, при этом в п-м такте последнего цикла переноса из (n-l)-ro разряда быть не может, так как на первый вход сумматора в первых (п-1) тактах поступают нули, а цепь циркуляции регистра 1 в п-м такте п-го цикла блокируется сигналом с выхода элемента И 14, поступающим на вход ЗАПРЕГГА элемента И 9 Таким образом, п первых (п-1) циклах умножения формируется произЧ ведение, ьдлгщшие разряды которого з писаны в регистре, множителя, старшие в регистре произведения, в п-м цикле - знак произведения. Эффективность предлагаемого устройства заключается в упрсяцении его за счет сокращения аппаратурных затрат и повышении быстродействия устройства. Известное и предлагаемо устройство содержат примерно равное количество логических элементов И и ИЛИ. В известном устройстве испол зуются три динамических регистра ра рядностью (п+1), в предлагаемом уст ройстве разрядность регистров равна п. Кроме того, в предлагаемом устройстве отсутствуют триггеры знака запоминания младших разрядов произведения. .Следовательно выигрьня в Оборудовании по сравнению с известным устройством составляет величину L 2W pt3WpH-NW, где аппаратурные затраты на триггер) WP - аппаратурные затраты на один разряд динамического регистра; Wф - затраты на схему объединения кодов знака и результа та. Цикл работы схемы известного уст ройства составляет (п+1) такт и не равен циклу хранения информации в других регистрах вычислительного устройства, в состав которого оно мо жет входить, т.е. цикл работы схемы известного устройства отличается от машинного цикла. Это потребует допол нительных аппаратурных затрат при построении блока управления, в частности на построение счетчика тактов. В предлагаемом устройстве цикл работы схемы совпадает с машинным циклом, что дает возможность использовать общие для вычислительного устройства тактирующие сигналы Т и Tf. Умножение в известном устройстве осуществляется за (п+1)п такт, в предлагаемом...устройстве - за п тактов. Таким образом, время выполнения операции умножения в предлагаемом устройстве уменьшается на один цикл. Формула изобретения Устройство для умножения чисел, содержащее регистры, сумматор,триггер, элементы И и элемент ИЛИ,о т личающееся тем, что, с целью упрощения устройства и увеличения быстродействия, вход первого регистра,соединен с выходом сумматора, выход первого разряда второго . регистра соединен с первым входом триггера, второй вход которого соединен с первой тактовой шиной устройства, а выход - с первыми входами первого и второго элементов И, выходы которшх подключены соответственно к первому и второму входу сумматора, выход второго разряда первого регистра соединен с первым входом третьего элемента И и первым входом четвертого элемента И, выход которого соединен со вторым входом сумматора,выход третьего элемента И соединен с первым входом элемента ИЛИ, выход которого подключен ко входу второго регистра, второй разряд которого соединен с первым входом пятого элемента И, выход которого соединен со вторым входом элемента ИЛИ, вход третьего регистра соединен со вторым входом второго. элем« нта И, первым входом шестого элемента И и выходом третьего регистра, выход шестого элемента И.соединен с первым входом сумматора, второй вход четвертого элеме 1та И оединен с выходом седьмого элемента , первый вход которого соединен со торыми, входами соответственно перого, второго, третьего, пятого и естого элементов И и второй тактоой шиной устройства, третьи входы торого и третьего элементов И и вто- ; ой вход седьмого элемента И соедиены с управляющим входом устройства. Источники информации, ринятые во внимание при., экспертизе 1. Авторское свидетельство СССР 608157, кл, Q 06 F 7/39, 1976. 2. Соловьев Г.Н. Арифметические стройства ЭВМ. М., Энергия, 1978, . 123 (прототип).

L(n

1Ь

I 7

LTf

n

Авторы

Даты

1981-03-30—Публикация

1979-05-04—Подача