1

Изобретение относится к облас-. ти вычислительной техники и может быть использовано для автоматического контроля больших интегральных схем. 5

Известны устройства для больших интегральных схем и Г2 , содержащие управляющую вычислительную машину , блок управления, устройства статических воздействий, блок 10 коммутации, измеритель токов и напряжений, генератор тактовой частоты, накопители слов, блок синхронизации, блок памяти, формирователи сигналов, компараторы, изме- 5 ритель временных интервалов.

Недостатками таких устройств является их сложность, необходимая для обеспечения заданной точности и быстродействия.20

Наиболее близким по технической сущности к предлагаемому является устройство для контроля больших интегральных схем 3, содержащее последовательно соеди- 25 ненные блок ввода-вывода информации, вычислитель, блок управления и измерительный блок, второй аыход блока управления подключен ко зходу блакэ цифроанашоговых преоб- 30

разователей, а также блок контактирования и блок синхронизации, первый выход которого подсоединен к первым входам компараторов и первому входу блока памяти уставок, выходом подключенного ко вторым входам ког-лпараторов, а вторым входом - к первому входу генератора тестовых последовательностей и входу блока синхронизации,второй выход; которого соединен со вторым входом генератора тестовых последовательностей, а третий выход - с первым входом логического блока, второй вход которого подключен к выходам компараторов ,выходы генератора тестовых последовательностей соединены со входами соответствующих формирователей сигналов,

Недостатками известного устройства являются сложность и пониженная надежность,

Целью изобретения является повышение надежности и упрощение устройства для контроля больших интегральных схем,

. Цель достигается тем, что формирователи сигналов, компараторы, блок Памяти уставок, блок синхронизации, логический блок и генератор

тестовых последовательностей размещены на одном кристалле; с большой интегральной схемой, причем входы блока контактирования соедине ны с выходами логического блока, блока управления и блока цифроаналоговых преобразователей соответственно, а выходы - соответственно с третьими входами компараторов, певым входом генератора тестовых последовательностей и входом измерительного блока.

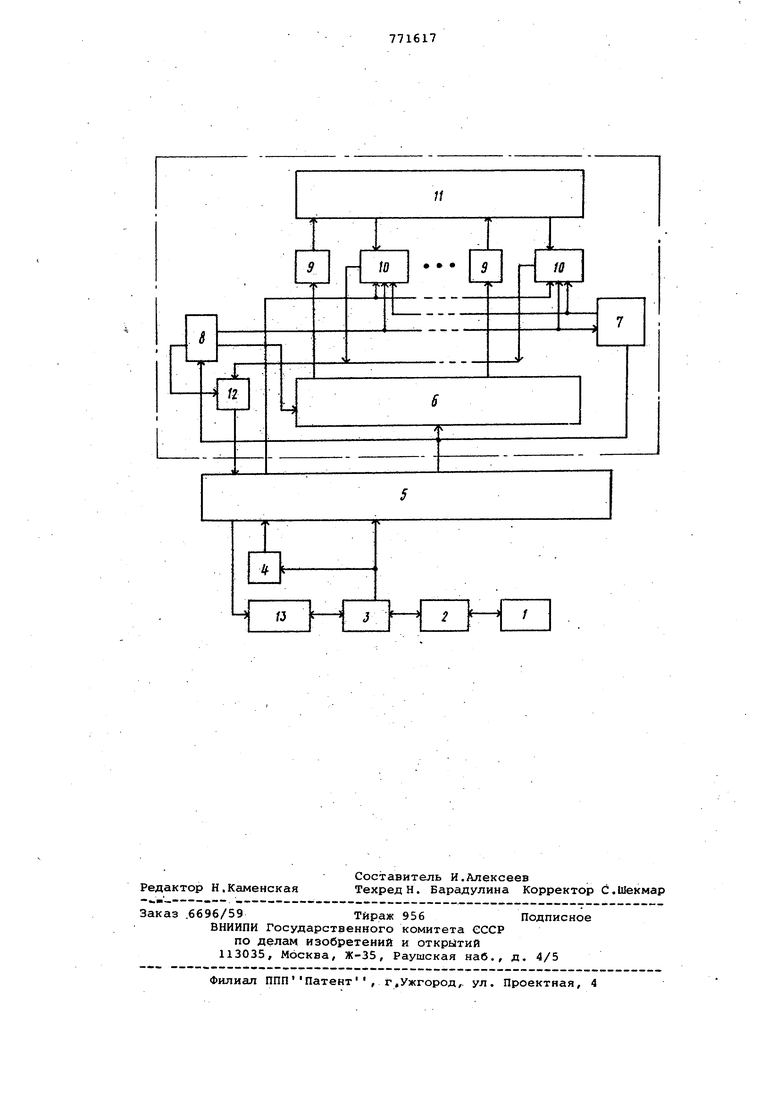

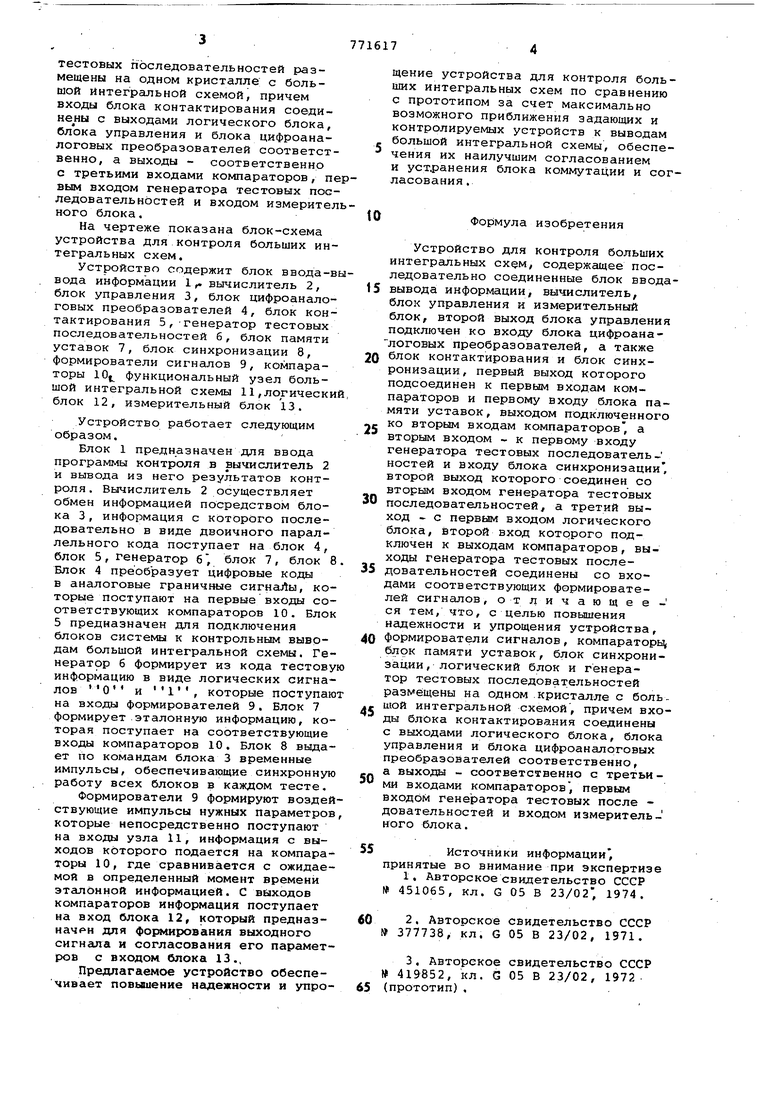

На чертеже показана блок-схема устройства для контроля больших интегральных схем.

Устройство содержит блок ввода-вывода информации 1,. вычислитель 2, блок управления 3, блок цифроаналоговых преобразователей 4, блок контактирования 5, генератор тестовых последовательностей б, блок памяти уставок 7, блок синхронизации 8, формирователи сигналов 9, компараторы 10| функциональный узел большой интегральной схемы 11,логически блок 12, измерительный блок 13.

Устройство работает следующим образом.

Блок 1 предназначен для ввода программы контроля в вычислитель 2 и вывода из него результатов контроля. Вычислитель 2 осуществляет обмен информацией посредством блока 3, информация с которого последовательно в виде двоичного параллельного кода поступает на блок 4, блок 5, генератор 6, блок 7, блок 8 Блок 4 преобразует цифровые коды в аналоговые граничные сигнаЛы, которые поступают на первые входы соответствующих компараторов 10. Блок 5 предназначен для подключения блоков системы к контрольным выводам большой интегральной схемы. Генератор б формирует из кода тестову информацию в виде логических сигнаО

которые поступаю

лов

на входам формирователей 9. Блок 7 формирует эталонную информацию, которая поступает на соответствующие входы компараторов 10. Блок 8 выдает по командам блока 3 временные импульсы, обеспечивающие синхронную работу всех блоков в каждом тесте.

Формирователи 9 формируют воздействующие импульсы нужных параметров которые непосредственно поступают на входы узла 11, информация с выходов которого подается на компараторы 10, где сравнивается с ожидаемой в определенный момент времени эталонной информацией. С выходов компараторов информация поступает на вход блока 12, который предназначен для фор шрования выходного сигнала и согласования его параметров с входом, блока 13.,

Предлагаемое устройство обеспечивает повышение нгщежности и упрощение устройства для контроля больших интегральных схем по сравнению с прототипом за счет максимально возможного приближения задающих и контролируемых устройств к выводам большой интегральной схемы, обеспечения их наилучшим согласованием и устранения блока коммутации и согласования .

Формула изобретения

Устройство для контроля больших интегральных схем, содержащее последовательно соединенные блок вводавывода информации, вычислитель, блок управления и измерительный блок, второй выход блока управления подключен ко входу блока цифроаналоговых преобразователей, а также блок контактирования и блок синхронизации , первый выход которого подсоединен к первым входам компараторов и первому входу блока памяти уставок, выходом подключенного ко вторым входам компараторов а вторым входом к первому входу генератора тестовых последовательностей и входу блока синхронизации второй выход которого соединен со вторым входом генератора тестовых последовательностей, а третий выход - с первым входом логического блока, второй вход которого подключен к выходам компараторов, выходы генератора тестовых последовательностей соединены со входами соответствующих формирователей сигналов, отличающее ся тем, что, с целью повышения надежности и упрощения устройства, формирователи сигналов, компараторц блок памяти уставок, блок синхронизации, логический блок и генератор тестовых последовательностей размещены на одном .кристалле с большой интегральной схемой , причем входы блока контактирования соединены с выходами логического блока, блока управления и блока цифроаналоговых преобразователей соответственно, а выходы - соответственно с третьими входами компараторов , первым входом генератора тестовых после довательностей и входом измерительного блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 451065, кл. G 05 В 23/02, 1974.

60 2. Авторское свидетельство СССР 377738, кл. 6 05 В 23/02, 1971.

3. Авторское свидетельство СССР ( 419852, кл. G 05 В 23/02, 1972 65 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Программируемое постоянное запоминающее устройство с контролем | 1979 |

|

SU951398A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНЫХ СТАНЦИЙ СЕТИ СПУТНИКОВОЙ СВЯЗИ, УСТРОЙСТВО РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНОЙ СТАНЦИИ И ФОРМИРОВАТЕЛЬ УПРАВЛЯЮЩЕГО СИГНАЛА | 2001 |

|

RU2214682C2 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Устройство для автоматического кон-троля больших интегральных схем намоп структурах | 1974 |

|

SU508788A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И ВОССТАНОВЛЕНИЯ ТЕХНИЧЕСКИХ СРЕДСТВ МЕДИЦИНСКОГО НАЗНАЧЕНИЯ | 1992 |

|

RU2072788C1 |

Авторы

Даты

1980-10-15—Публикация

1978-05-18—Подача