(Б) ПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с автономным контролем | 1979 |

|

SU855739A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1619347A1 |

| Система передачи и приема сигналов контроля | 1981 |

|

SU999081A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство для контроля памяти | 1985 |

|

SU1367045A1 |

1

Изобретение относится к вычислительной технике и может быть исполь зовано в создании больших интеграль-ных схем - запоминающих устройств.

Известны полупроводниковые запоминающие устройства, которые имеют различные объемы и Лункциональные схемы матриц памяти р .

Наиболее близким к изобретению по технической сущности является запо- JQ минающее устройство, содержащее дешифратор строк, матрицу памяти, устройство синхронизации и управления, устройство ввода-вывода, дешифратор ч столбцов и буферный регистр, усилите-is ли столбцов Г2,

Недостатками этого устройства являются сложность и большое время контроля за счет большого объема контрольно-испытательной аппаратуры при про- 20 изводстве, испытаниях и входном контроле изделий. Кроме того, контрольно-испытательная аппаратура значительно усложняется при проведении динамических испытаний и контроле функциониропания на предельных частотах изза необходимости введения в систему контроля сложных контрольно-испытательных схем, формирователей сигналов, компараторов, динамических коммутато-: ров и других согласующих устройств, которые необходимо предельно приближать к выводам контролируемой интегральной схемы, для исключения влияния механических контактирующих устройств и длинных связей между выводами интегральной схемы и выводами системы при динамических испытаниях и контроле функционирования на предельных частотах.

Цель изобретения - повышение надежности устройства за счет устранения влияния механических контактирующих устройств и длинных связей между выводами интегральной схемы и выводами системы при динамическом контроле и контроле функционирования на предельных частотах, что приводит к

упрощению аппаратурных средств автоматического контроля при производстве, испытаниях и входном контроле изделий.

Поставленная цель достигается тем, 5 что F3 программируемое постоянное запоминающее устройство с контролем, содержащее буферный регистр, выходы которого через дешифратор подключены к выходам блока усилителей, выходы 0 которого соединены с соответствующими входами и выходами матричного на опителя, блок синхронизации, выходы которого соединены с тактовыми входами буферного регистра, блок усилителей и блок ввода-вывода, ннформационный вход-выход которого соединен с входом-выходом дешифратора, первый вход - с входной шиной, выход - с выходной информационной шиной, генератор, выход которого соединен с входом формирователя импульсов управле-ния и первым входом счетчика-регистра, выходы которого соединены с первыми адресными входами блока коммута-25 контролем. ции, выходы которого соединены с входами буферного регистра, введены блок сравнения и два блока ИЛИ, первые вхо ды которых соединены с первым и вторым выходами формирователя импульсов управления, вторые входы блоков ИЛИ являются соответственно входами разрешения и записи-считывания устройства, а выходы блоков ИЛИ соединены соответственно с вторым входом блока синхронизации и вторым входом блока ввода-вывода, первый вход блока сравнения является входом контроля устройства, второй вход блока сравнения соединен с третьим входом формировате ля импульсов управления, третий вход блока сравнения является входом-задания режима и соединен с вторым входом счетчика-регистра и с управляющим входом блока коммутации, четвертый вход блока сравнения соединен с выходом блока ввода-вывода, а выход соединен с входом генератора импульсов и является выходом результата контроля устройства, а вход генератора импульсов является выходом синхронизации устройства. Выше перечисленные блоки и связи, выполненные по единой технологии и на одном кристалле с известным, обеспечивают автономную работу устройства при подаче на устройство сигналов Выбор режима, Контроль, Запись-считывание, в режиме смитывания и Выбор режима, Информация и Запись-считывание в режиме записи, при этом нет жестких требований к Фронтам данных сигналов, поэтому механическое контактирующее устройство и длинные связи не оказывают паразитных влияний. Остальные сигналы (адреса, служебные ) максимально приближены и полностью согласованы с входами функциональных блоков устройства.

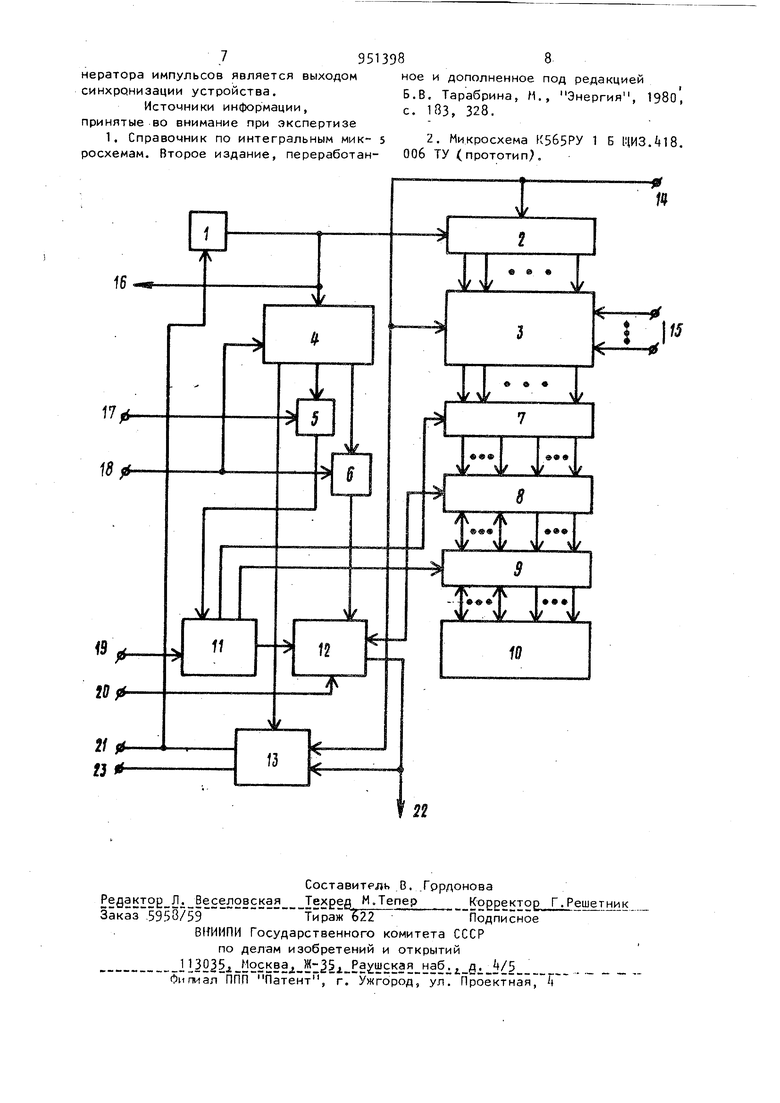

Кроме того, при производстве интегральных схем отпадает необходимость в сложных автоматизированных системах контроля типа Визир, Элекон-ФЗУ при климатических испытаниях, испытаниях на надежность и долговечность и входном контроле, су(дественно упрощаются нестандартные аппаратурные средства, обеспечивающие функционирование и контроль изделий. На чертеже приведена блок-схема предлагаемого программируемого постоянного запоминающего устройства с Устройство выполнено в виде интегральной схемы и функционально состоит из генератора и |пульсов 1 , счетчика-регистра 2, блока коммутации 3, формирователя импульсов управления k, первого 5 и второго 6 блоков ИЛИ,.буферного регистра 7, дешифратора 8, блока усилителей 9, матричного накопителя 10, блока синхронизации 11, блока ввода-вывода 12, блока сравнения 13. Устройство содержит также выводы управления . Устройство при контроле работает следующим образом. В режиме считывания на вход 18 поступает соответствуЮ1ций сигнал, а на выход И подается сигнал Выбор режима, который открывает внутренние шины адреса блока коммутации 3, сбрасывает счетчик-регистр 2 в начальное состояние и устанавливает выходной триггер блока сравнения 13 в состояние, которое запускает генератор импульсов 1, Импульсы с генератора 1 поступают на вход счетчика-регистра 2, выходы которого используются в качестве внутренних шин адреса, поступающих на блок коммутации 3 и далее на адресные входы регистра 7- Одновременно с управляемого генератора импульсов 1/на вывод 1б поступают импульсы которые могут быть использованы в качестве синхросигнала для внешних устройств контроля. Кроме того, импульсы поступают на вход формирователя и пульсов управления k. Формирователь k выдает импульсы Разрешение, Запись-считывание и строб анализа информации. Импульсы Разрешение и Запись-считывание поступают через блоки ИЛИ 5 и 6 на блоки синхронизации 11 и ввода-вывода 12 соответственно. Строб анализа информации поступает на блок сравнения 13, где происходит сравнение инф мации , выдаваемой матричным накопителем 10, и контрольной, которая поступает с внешнего устройства на вывод 23. В случае неравнозначности информации, схема анализа выдает сигнал ре зультата контроля на внешний вывод 2 и на вход генератора импульсов, который останавливается. При контроле постоянных запоминающих устройств, программируемых запоминающих устройств в матрице памяти, как правило, ин(| рмация во всех ячейках одинаковая: либо логический О, либо логическая 1, в зависимости от тех нологии изготовления, при этом контрольный сигнал представляет собой просто постоянный уровень либо логическЬго О, либо логической 1. При контроле запоминающих устройс с записанной информацией контрольный сигнал может быть сформирован внешним устройством, синхронизация которого осуществляется импульооМ Синхр. с внешнего вывода 16. В режиме записи на вывод 18 подается соответствующий сигнал с внешнего устройства. Затем на внешний вывод k подается сигнал Выбор режима, после чего включается генератор импульсов 1 и выдает импульс синхронизации на внешний вывод 16, запускает счетчик-регистр 2 и формирователь импульсов управления Ц, который выдает импульсы Разрешение и Считывание-запись на блоки синхронизации и ввода-вывода через блоки ИЛИ 5 и 6. На вход блока ввода-вы вода 12 с внешнего устройства через вывод 20 подается входная информация синхронно с работой счетчика-регистра 2. В рабочем режиме устрюйство работает аналогично прототипу за исключе нием того, что на вывод Т подается запрещающий сигнал. Применение предлагаемого устройства значительно удешевляет процесс контроля при производстве, испытаниях и входном контроле за счет упрощения аппаратурных средств контроля, а также значительно снижает затраты на эксплуатацию оборудования и разработку программно-математического обеспечения. Формула изобретения Программируемое постоянное запоминающее устройстве с контролем, содержащее буферный регистр, выходы которого через дешифратор подключены к входам блока усилителей, выходы которого соединены с- соответствующими входами и выходами матричного накопителя, блок синхронизации, выходы которого соединены с тактовыми входами буферного регистра, блок усилителей и блок ввода-вывода, информационный вход-выход,которого соединен с входом-выходом дешифратора. первый вход - с входной шиной, а выход - с выходной информационной шиной, генератор, выход которого соединен с входом формирователя импульсов управления и первым входом счетчика-регистра, выходы которого соединены с первыми адресными входами блока коммутации, выходы которого соединены с входами буферного регистра, отли чающееся те«ч, что, с целью повышения надежности устройства, в него введены блок сравнения и два блока ИЛИ, первые входы которых соединены с первым и вторым выхедами формирователя импульсов управления, вторые входы блоков ИЛИ являются соответственно входами разрешения и записи-считывания устройства, а выходы блоков ИЛИ соединены соответственно с вторым входом блока синхронизации и вторым входом feripка ввода-вывода, первый ЁХОД блока сравнения является входом контроля устройства, второй вход блока сравнения соединен с третьим входом формирователя импульсов управления, третий вход блока сравнения является входом задания режима и соединен с .вторым входом счетчика-регистра и с управляющим входом,блока коммутации, четвертый вход блока сравнения соединен с выходом блока ввода-вывода, а выход соединен с входом генератора импульсов и является выходом .результата контроля устройства, а вход ге

Авторы

Даты

1982-08-15—Публикация

1979-06-04—Подача