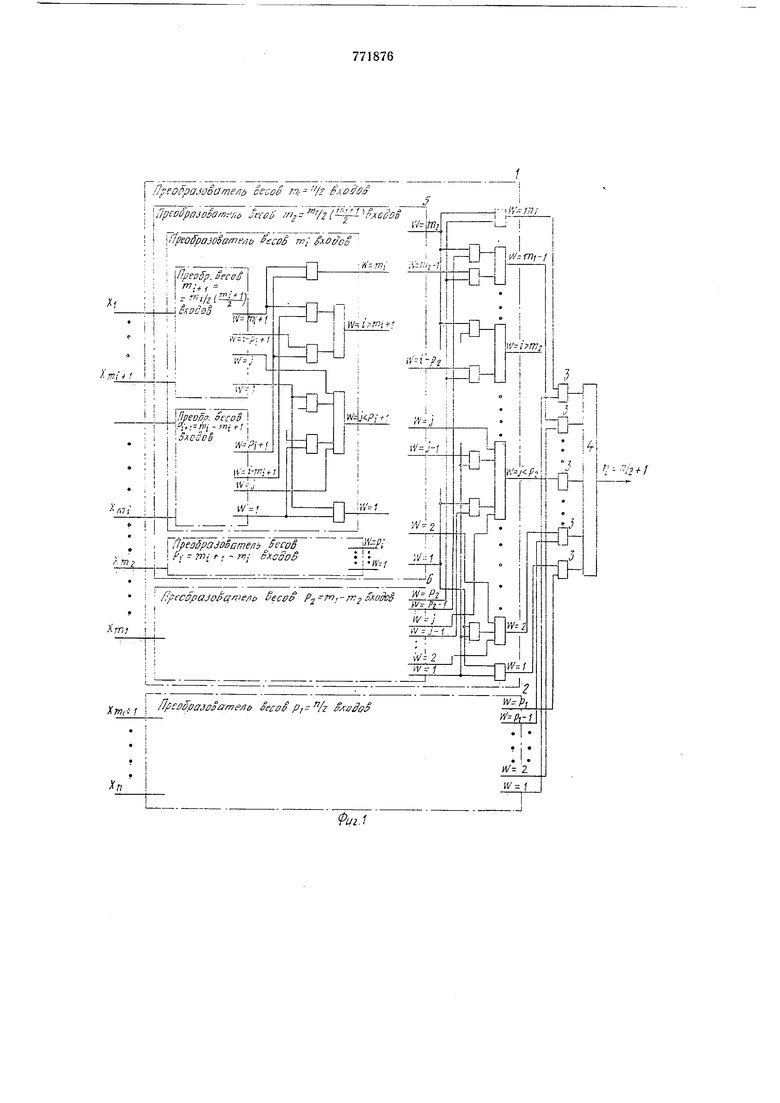

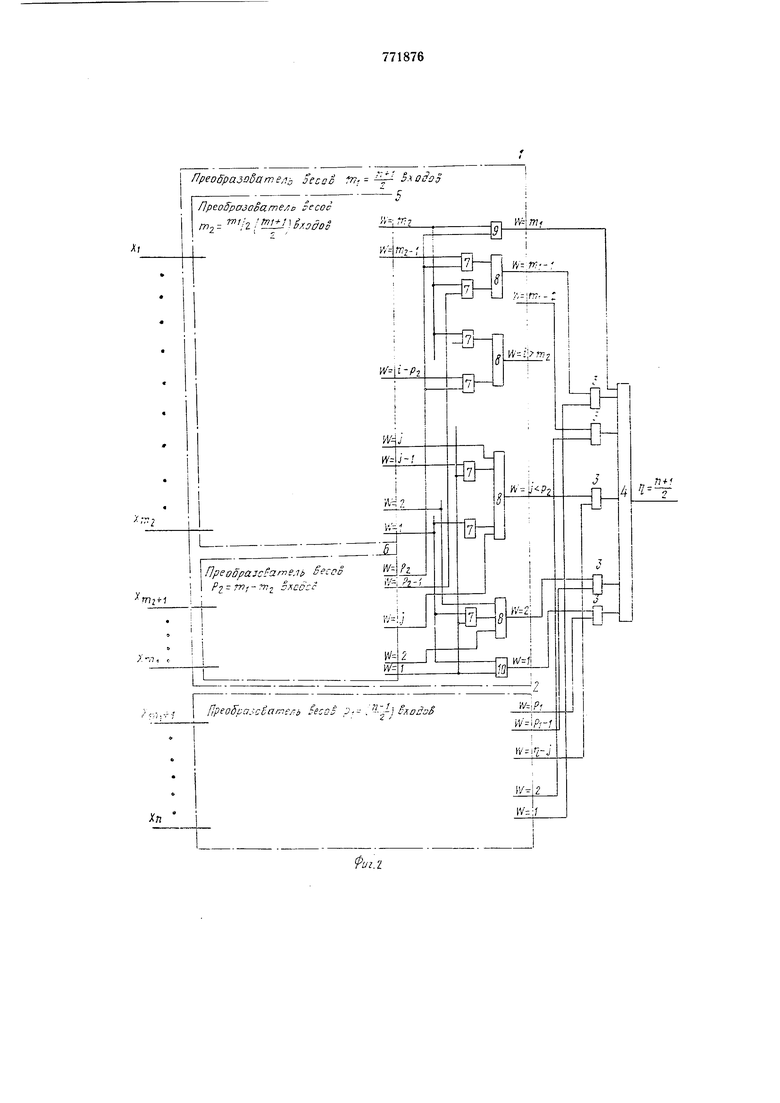

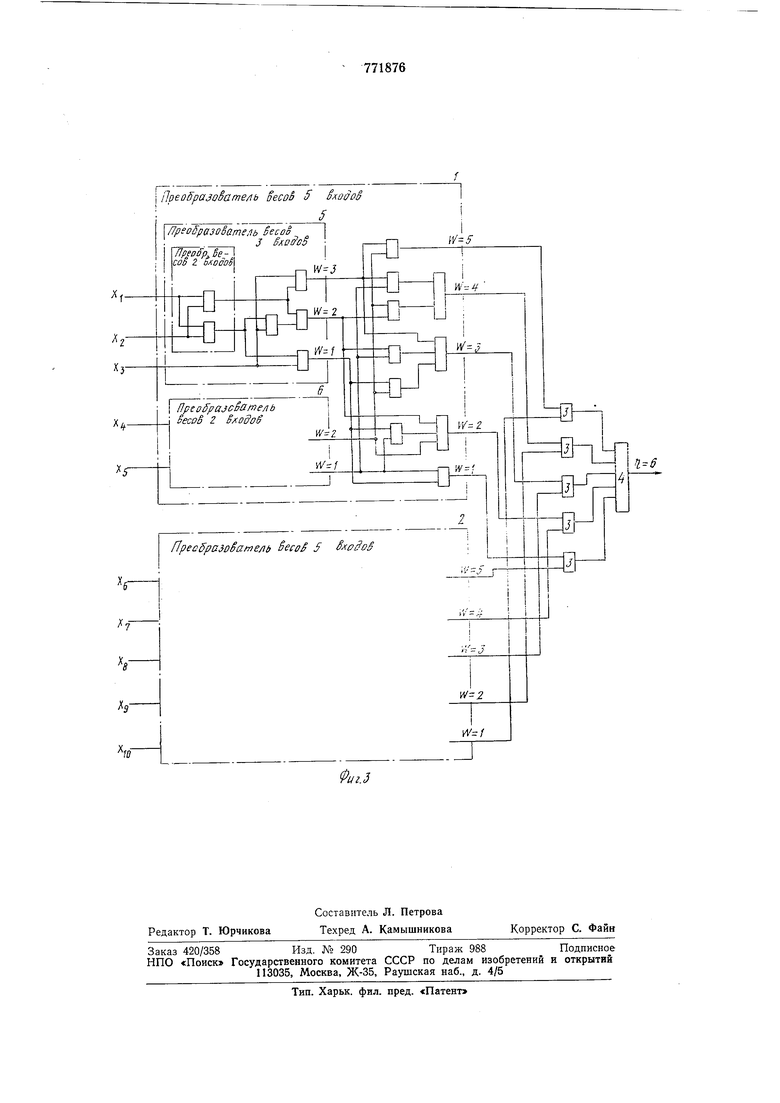

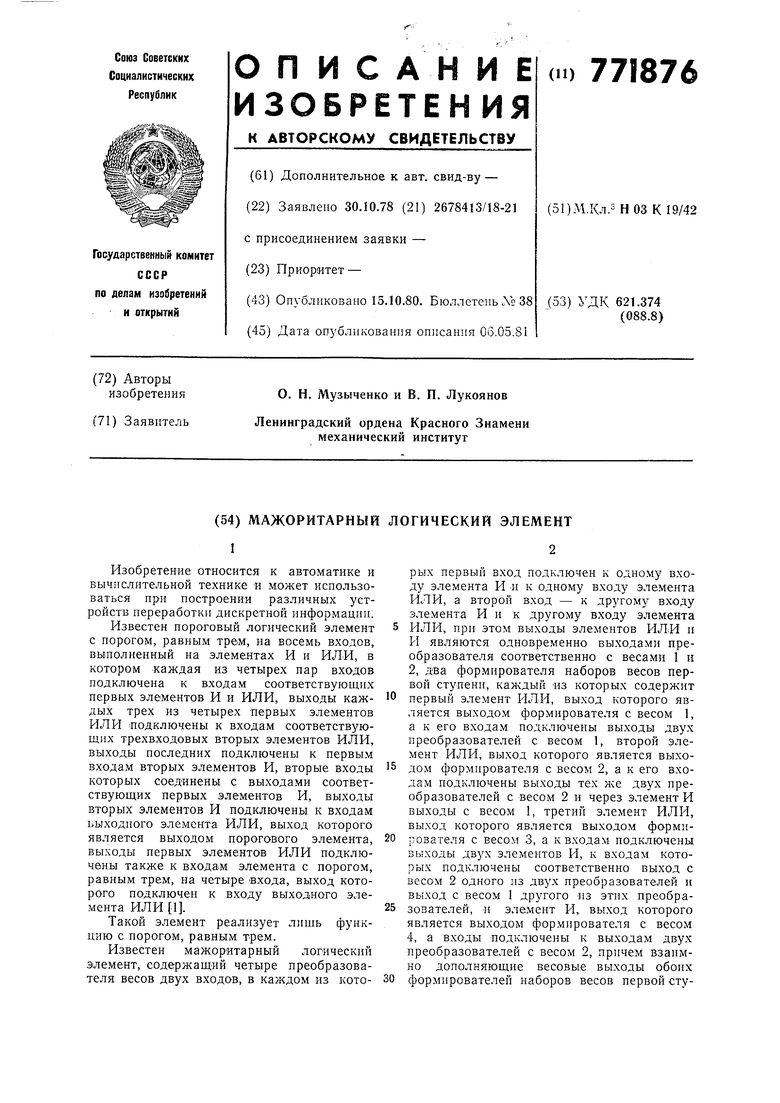

пени попарно подключены к входам формирователя заданного порога второй ступени, выходы которого подключены попарно к входам элементов И с выходами, .подключенными к входам выходного элемента ИЛИ 2. Недостаток данного мажоритарного логического элемента заключается в ограниченном числе его входов, что сужает функциональные возможности элемента. Целью изобретения является расширение функциональных возможностей логического элемента. Для достижения цели в мажоритарный логический элемент, содержащий преобразователи весов двух входов, формирователи наборов весов первой ступени и выходной элемент ИЛИ, выход которого является выходом элемента, введены два преобразователя весов /2 входов или входов при нечетном п (п - число .входов мажоритарного элемента), имеющих выходы с весаМИ от 1 до величины, равной числу входов преобразователя, подключенные попарно к входам элементов И, число которых на единицу меньше величины порога элемента, образуя все неповторяющиеся комбинации весов выходов этих преобразователей, сумма которых равна -величине порога элемента, причем выходы элементов тлfя 4- 1 И и выход преобразователя весов -входов с весом - подключены к входам ВЫХОДНОГО элемента ИЛИ, а также преобразователя весов mi и р; входов, -имеюЩие выходы с весами от 1 до величины, равной числу входов преобразователя. Пр,и этом каждый из введенных преобразователей содержит два преобразователя весов mj и р входов с равным и отличающимся на единицу числом входов, сумма которых равна числу входов данного преобразователя, выходы преобразователей весов mi и Pi входов подключены попарно к входам групп элементов И, образуя в группе все «еповторяющиеся комбинации весов выходов преобразователей весов mi и р, входов, сумма которых одинакова и равна весу одного из выходов данного преобразователя в пределах от 2 до величины, на единицу меньшей числа его входов, выходы элементов И каждой груплы и выходы преобразователей весов nii и Pi входов, вес которых равен сумме весов выходов, подключенных к входам каждого элемента И данной группы, подключены к входам элемента ИЛИ, выход которого является одним яз выходов данного преобразователя с соответствующим весом, выходы преобразователей весов /П{ и Pi входов с единичными весами подключены к входам элемента ИЛИ, выход которого является выходом данного преобразователя с единичным весом, а выходы с весами, равными числу входов,- к входам элемента И, выход которого является выходом данного преобразователя с весом, равным числу входов данного преобразователя. Иа фиг. I представлена структурная схема мажоритарного логического элемента для случая четного числа входов; на фиг. 2 - для случая нечетного числа входов; на фиг. 3 - схема его реализации для десяти входов. Малшритарный логический элемент состоит из двух преобразователей / и 2 -Ы весов mi /2 ( нечетном п - число входов элемента) входов и р; /2 п- при нечетном п | входов, имеющих выходы с весами от и;мип 1 до 1 макс mij преобразователя / и от w „|,и 1 ДО tw макс PI у преобразователя 2. Выходы преобразователей 1 } 2 подключены попарио к входам элементов И 3, число которых т - 1, где 11 - величина порога мажоритарного логического элемента, образуя все неповторяющиеся комбинации весов их выходов, сумма которых одинакова и равна г - величине порога. |Выходы элементов 3, а также выход преобразователя / при нечетном я с весом ж Ш т) ---подключены ,к входам выходного элемента ИЛИ 4, выход которого является выходом мажоритарного лопического элемента. Каждый из преобразователей весов т и PI входов и все последующие состоят из двух преобразователей 5 и 6 весов гпг и PJ входов С равным или отличающимся на единицу числом входов, сумма которых равна числу входов данного преобразователя, и с выходами с весами от I до величины, равной числу входов. Выходы преобразователей весов m-i и р; входов попарно подключены к входам групп элементов И 7, число групп определяется числом выходов данного преобразователя (/) с весами от 2 до (mi + p-;-1), образуя в каждой группе все неповторяющиеся комбинации весов выходов преобразователей весов mi и р входов (5 и 6), сумма которых одинакова и равна весу одного из выходов данного преобразователя (;/) в пределах от 2 до (Шг + рг-1). Выходы элементов И 7 каждой группы и выходы преобразователей весов гПг и PJ- входов (5 и б) с весом, равным сумме весов выходов преобразователей, подключенных к входам каждого элемента И данной группы, подключены к входам элемента ИЛИ 8, выход которого является одним из выходов данного преобразователя (/) с соответствующим весом. Для образования выхода данHoro преобразователя 1 с весом nii + pi выходы преобразователе весов т, п р, входов с весами т; и pi соответственно подключены к входам элемента И 9, выход которого и является выходом данного преобразователя (/) с весом tni + pi, а выходы преобразователей весов т :и pi входов (5 п б) с весами, р|а.в«Ы|Ми 1, подключены к входам элемента ИЛИ 10, выход которого является выходом данного преобразователя (:/) с единичным весом. Устройство работает следующим образом. При поступлении на его входы d единичных сигналов, из которых di поступает на входы преобразователя 1 весов Ш входов / и - на ВХОДЫ преобразователя 2 весов PI входов, на всех выходах преобразователя 1 с весами, меньшими или равными di, и на всех выходах преобразователя 2 с весами, меньш-ими или равнымИ d, появляются единичные сигналы. Если величина порога мажоритарного элемента d, то единичные сигналы появляются на обоих входах только одного элемента 3, подключенного к выходу преобразователя / с весом di и к выходу иреобразователя 2 с весом d, что вызывает на его выходе и на выходе элемента ИЛИ 4 появление единичного сигнала. Если d больше величины порога «мажоритарного элемента, то единичные сигналы появляются на обоих входах нескольких элементов И 3, что вызывает на их выходах и на выходе элемента ИЛИ 4 появление единичного сигнала. Если все единичные сигналы поступают на входы преобразова( . теля 1 с числом входов (при нечетном п), то единичный сигнал появляется на выходе мажоритарного элемента только при появлении единичного сигнала на его выходе с весом, равным числу входов. При этом число единичных си1гналов равно порогу мал оритарного элемента. Таким образом, каждый раз, когда число единичных сигналов на входах мажоритарного логического элемента больше «ли равно величип + I не его порога (т при нечетном п и Т1 /2+1 при четном п) на выходе элемента ИЛИ 4 появляется единичный сигнал. Таким образом, данный мажоритарный логический элемент имеет большие функциональные возможности по сравнению с прототипом за счет увеличения числа его входов. Формула изобретения Мажоритарный логический элемент, содержаш,ий преобразователи весов двух входов, формирователи наборов весов первой ступени и выходной элемент ИЛИ, выход которого является выходом элемента, о тл и ч а ю ш, и и с я тем, что, с целью расширения его функциональных возможностей, в него введены два преобразователя весов и 1 /2 ВХОДОВ ИЛИ -л- ВХОДОВ при нечетном п (п - число входов мажоритарного элемента) , имеюших выходы с весами от 1 до величины, равной числу входов преобразователя, подключенные попарно к входам элементов И, число которых на единицу меньше величины порога элемента, образуя все неповторяюш,иеся комбинации весов выходов этих Преобразователей, сумма которых равна величине порога элемента, причем выходы элементов И и выход преобра11+1fi + зователя весов входов с весом -х- подключены к входам выходного элемента ИЛИ, а преобразователи весов mi и Pi входов, имеющие выходы с весами от 1 до величины, равной числу входов преобразователя, при этом каждый из введенных преобразователей содержит два преобразователя весов tHi и Pi входов с равным или отличающимся на единицу числом входов, сумма которых равна числу входов данного преобразователя, выходы преобразователей весов т,- и р входов подключены попарно к входам групп элементов И, образуя в каждой группе все неповторяющиеся комбинации весов выходов преобразователей весов Ш; и Pi входов, сумма которых одинакова И равна весу одного из выходов данного преобразователя в пределах от 2 до величины, на единицу меньшей числа его входов, выходы элементов И каждой группы и выходы преобразователей весов гщ и pi входов, вес которых равен сумме весов выходов, подключенных к входам каждого элемента И данной группы, подключены к входам элемента ИЛИ, выход которого является одним из выходов данного преобразователя с соответствующим весом, выходы преобразователей весов mi и pi входов с единичными весами подключены к входам элемента ИЛИ, выход которого является выходом данного преобразователя с единичным весом, а выходы с весами, равными числу входов, - к входам элемента И, выход которого является выходом данного преобразователя с весом, равным числу входов данного преобразователя. Источники информации, принятые во внимание при экспертизе: 1.Ф. Селлерс, Методы обнаружения ошибок в работе ЭЦВМ, пер. с англ., М., «Мир, 1972, с. 85, фиг. 4.20. 2.Заявка 1945420/18-21, кл. Н 03 К 19/42, 1973, по которой принято решение о ыдаче авторского свидетельства.

Af S.

X,

f

ГГ:,

Wm

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1977 |

|

SU1078620A1 |

| Устройство для обнаружения ошибокВ пАРАллЕльНОМ -РАзРядНОМ КОдЕС пОСТОяННыМ BECOM | 1979 |

|

SU830390A1 |

| Пороговый элемент | 1981 |

|

SU1046932A1 |

| Многопороговый логический элемент (его варианты) | 1983 |

|

SU1261106A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом @ | 1981 |

|

SU1027729A1 |

| Пороговый логический элемент | 1981 |

|

SU991612A1 |

| Пороговый логический элемент | 1980 |

|

SU974588A1 |

| Пороговый логический элемент | 1981 |

|

SU1005317A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1988 |

|

SU1525746A1 |

| Пороговый логический элемент | 1979 |

|

SU818016A1 |

Щг-Рг

npeoSpa c ame.-jt, SecoS

P - Ш; №2

т2г1

,;,,;..,.. I i peo5pa.,-b ecoS p--Xn

fl + 1

t- 2|

|УЦ г-

L

.-,.- S(

w ifrJ

IV 2 I ilpeoffpajoSame/ib SecoS 5 SxoaoS

Авторы

Даты

1980-10-15—Публикация

1978-10-30—Подача