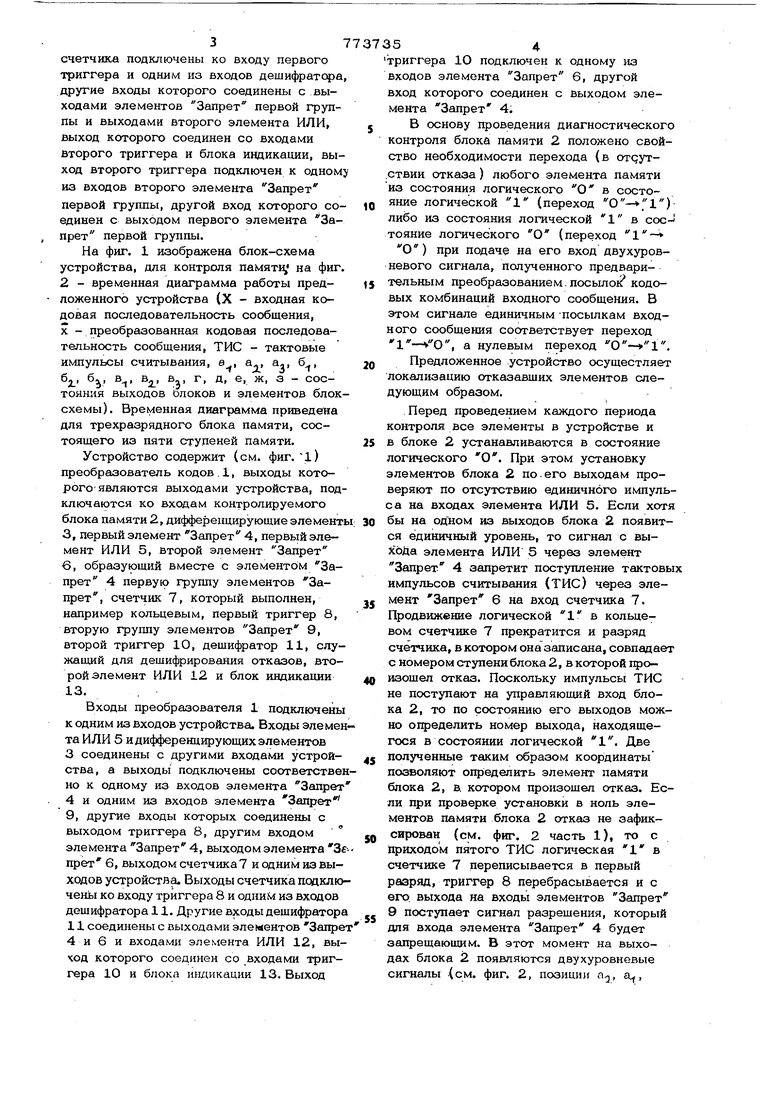

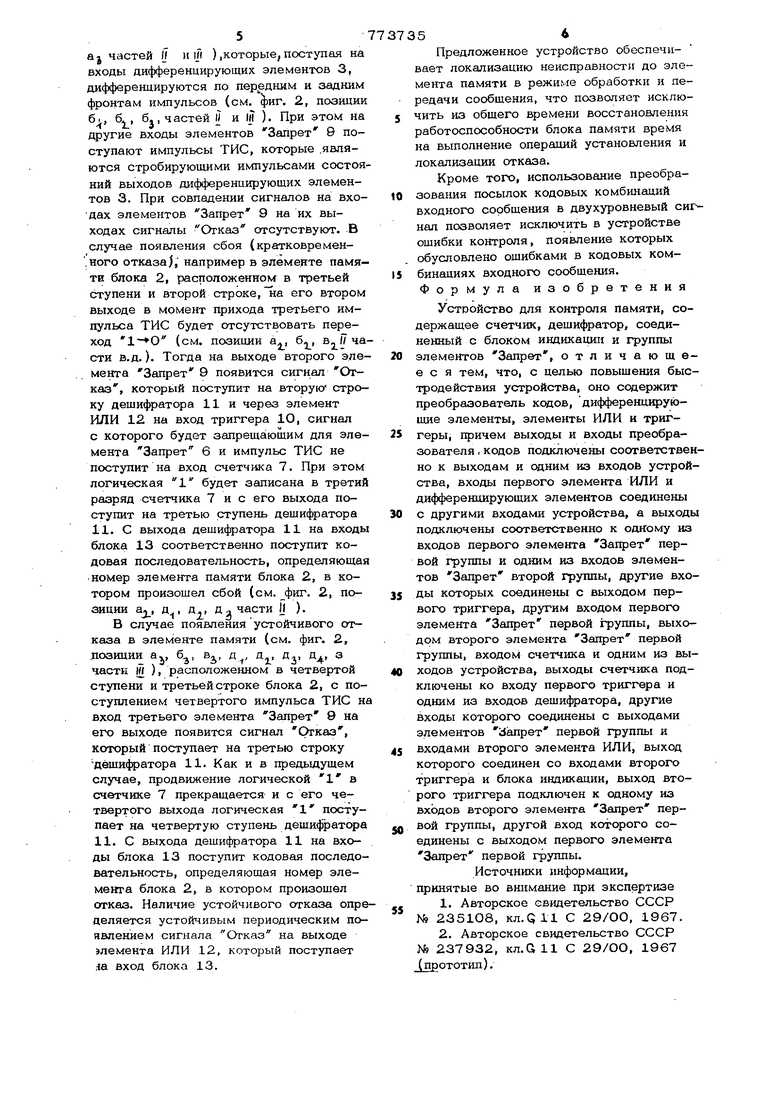

Изобретение относится к запоминающим устройствам и может быть использовано для диагностики накопителей. Известно устройство, содержащее: фор мирователи токов записи и считывания, логические элементы 1. С хнако это .устройство предназначено только для контроля блоков памяти с ма гнитным дешифратором, что ограничивает область его применения. Наиболее близким по технической сущности к предложенному является устройство для контроля памяти, содержащее счетчик, дешифратор соединенный с блоком индикации, и группы элементов Запрет 2. Недостатками этого устройства являются отсутствие локализации отказа- и сбоя в элементах блока памяти в режиме обработки информации, принципиальная невозможность разделения по результатам контроля ошибок первого и второго рода (при появлении в испытательной кодовой комбинации посылок с ошибками), а также невысокая скорость работы устройства. Цель изобретения - повышение быстродействия устройства и достоверности контроля. Поставленная цель достигается тем, чтоустройство содержит преобразователь кодов, дифференшфуюоше элементы, элементы ИЛИ и триггеры, причем выходы и входы преобразователя кодов подключен соответственно к выходам и одним из входов устройства, входы первого элемента ИЛИ и )ференцирующих элементов соединены с другими входами устройства, а выходы подключены соответственно к одному нз входов первого элемента Запрет первой групы и одним из входов элементов Запрет второй группы, другие входы которых соединены с выходом первого триггера, другим входом первого элемента Запрет первой группы, выходом второго элемента Заррет первой группы, входом счетчика д одним из выходов устройства, выходы счетчика подключены ко входу первого триггера и одним из входов дешифратора другие входы которого соединены с выходами элементов Запрет первой группы и выходами второго элемента ИЛИ, выход которого соединен со входами второго триггера и блока ивдикации, вы ход второго триггера подключен к одном из входов второго элемента Запрет первой группы, другой вход которого со единен с выходом первого элемента За прет первой группы. На фиг. 1 изображена блок-схема устройства, для контроля памяти, на фиг 2 - временная диаграмма работы предложенного устройства (X - входная кодовая последовательность сообщения, X - преобразованная кодовая последовательность сообщения, ТИС - тактовые импульсы считывания, а , а., а, б, г. Ъ 2. 3 ® тояния выходов Ьлоков и элементов бло схемы). Временная диаграмма приведена для трехразрядного блока памяти, состоящего из пяти ступеней памяти. Устройство содержит (см. фиг. Ч) преобразователь кодов . 1, выходы которого являются выходами устройства, по ключаются ко входам контролируемого блока памяти 2, дифференцирующие элементы: 30 бы 3, первый элемент Запрет 4, первый элемент ИЛИ 5, второй элемент Запрет 6, образующий вместе с элементом Запрет 4 первуЕ9 группу элементов Запрет, счетчик 7, который выполнен, например кольцевым, первый триггер 8, вторую группу элементов Запрет 9, второй триггер 1О, дешифратор 11, служащий для дешифрирования отказов, второй элемент ИЛИ 12 и блок индикации 13.. Входы преобразователя 1 подключены к одним из входов устройства. Входы элемен та ИЛИ 5 и дифференцирующих эле ментов 3соединены с другими входами устройства, а выходы подключены соответствен но к одному из входов элемента Запрет 4и одним из входов элемента Запрет 9, другие входы которых соединены с выходом триггера 8, другим входом элемента Запрет 4, выходом элемента Зг прет б, выходом счетчика 7 и одним из выходов устройства. Выходы счетчика подключень ко входу триггера 8 и одним из входов дешифратора 11. Другие входы дешифратора 11 соединены с выходами элементов Запре 4 и 6 и входами элемента ИЛИ 12, выкод которого соединен со входами триггера 10 и блока индикации 13. Выход 54 триггера 1О подключен к одному из входов элемента Запрет 6, другой вход которого соединен с выходом элемента Запрет 4. В основу проведения диагностического контроля блока памяти 2 положено свойство необходимости перехода (в отдутствии отказа) любого элемента памяти из состояния логического О в состояние логической 1 (переход .) либо из состояния логической 1 в coc-J тояние логического О (переход О) при подаче на его вход двухуровневого сигнала, полученного предварительным преобразованием.посылок кодовых комбинаций входного сообщения. В этом сигнале единичным -посылкам входного сообщения соответствует переход , а нулевым переход . Предложенное устройство осущестляет локализацию отказавших элементов следующим образом. Перед проведением каждого периода контроля все элементы в устройстве и в блоке 2 устанавливаются в состояние логического О. При этом установку элементов блока 2 по.его выходам проверяют по отсутствию единичного импульса на входах элемента ИДИ 5. Если хотя на одном из выходов блока 2 появится единичный уровень, то сигнал с выЗсода элемента ИЛИ 5 через элемент Запрет 4 запретит поступление тактовых импульсов считывания (ТИС) через элемент Запрет 6 на вход счетчика 7. Продвижение логической 1 в кольцевом счетчике 7 прекратится и разряд счётчика, в котором она записана, совпадает с номером ступени блока 2, в которой произошел отказ. Поскольку импульсы ТИС не поступают на управляющий вход блока 2, то по состоянию его выходов можно определить номер выхода, находящегося в состоянии логической 1. Две полученные таким образом координаты позволяют определить элемент памяти блока 2, в. котором произошел отказ. Если при проверке установки а ноль элементов памяти блока 2 отказ не зафиксирован (см. фиг. 2 часть 1), то с приходом пятого ТИС логическая 1 в счетчике 7 переписывается в первый разряд, триггер 8 перебрасывается и с его. выхода на входы элементов Запрет 9 поступает сигнал разрешения, который для входа элемента Запрет 4 будет запрещающим. В этот момент на выходах блока 2 появляются двухуровневые сигналы .(см. фиг. 2, позиции е(, а.

5

aj частей iT HI ).которые,поступая на входы дифференцирующих элементов 3, дифференцируются по передним и задним фронтам импульсов (см. иг. 2, позиции бг, б. , б, .частей Н и W ). При этом на другие входы элементов Запрет 9 поступают импульсы ТИС, которые .являются стробирующими импульсами состояний выходов дифференцирующих элементов 3. При совпадении сигналов на входах элементов Запрет 9 на их выходах сигналы Отказ отсутствуют. В случае появления сбоя (кратковремен.ного отказа), например в элемерте памяти блока 2, расположенном в третьей ступени и Второй строке, на его втором выходе в момент прихода третьего импульса ТИС будет отсутствовать переход (см. позиции а., б, в./7 части в,д.). Тогда на выходе второго элемента Запрет 9 появится сигнал Отказ, который поступит на вторую строку дешифратора 11 и через элемент ИЛИ 12 на вход триггера 10, сигнал с которого будет запрещающим для элемента Запрет 6 и импульс ТИС не поступит на вход счетчика 7. При этом логическая 1 будет записана в третий разряд счетчика 7 и с его выхода поступит на третью ступень дешифратора 11. С выхода дешифратора 11 на входы блока 13 соответственно поступит кодовая последовательность, определяющая номер элемента памяти блока 2, в котором произошел сбой (см. фиг. 2, позиции а, а , р., д части 1| ).

В случае появления устойчивого отказа в элементе памяти (см. фиг. 2, .позиции ау 6.J, в, а, п., д, Д., з части |« ), расположенном в четвертой

ступени и третьей строке блока 2, с поступлением четвертого импульса ТИС на вход третьего элемента Запрет 9 на его выходе появится сигнал Отказ, который поступает на третью строку

дёщи(|ратора 11. Как и в предыдущем случае, продвижение логической 1 в счетчике 7 прекращается и с его четвертого выхода логическая 1 поступает на четвертую ступень дешифратора 11. С выхода дешифратора 11 на входы блока 13 поступит кодовая последовательность, определяющая номер элемента блока 2, в котором произощел отказ. Наличие устойчивого отказа определяется устойчивым периодическим появлением сигнала Отказ на выходе злемента ИЛИ 12, который поступает да вход блока 13.

354

Предложенное устройство обеспечивает локализацию неисправности до элемента памяти в режиме обработки и передачи сообщения, что позволяет исключить из общего времени восстановления работоспособности блока памяти время на выполнение операций установления и локализации отказа.

Кроме того, использование преобразования посылок кодовых комбинаций входного сообщения в двухуровневый синал позволяет исключить в устройстве ошибки контроля, появление которых обусловлено ошибками в кодовых комбинациях входного сообщения. Формула изобретения

Устройство для контроля памяти, содержащее счетчик, дешифратор, соединенный с блоком индикации и группы элементов Запрет , отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит преобразователь кодов, дифференцирующие элементы, элементы ИЛИ и триггеры, причем выходы и входы преобразователя , кодов подключены соответствено к выходам и одним из входой устройства, входы первого элемента ИЛИ и дифференцирующих элементов соединены с другими входами устройства, а выходы подключены соответственно к одному из входов первого элемента Запрет первой группы и одним из входов элементов Запрет второй группы, другие входы которых соединены с выходом первого триггера, другим входом первого элемента Запрет первой группы, выходом второго элемента Запрет первой группы, входом счетчика и одним из выходов устройства, выходы счетчика подключены ко входу первого триггера и одним из входов дешифратора, другие входы которого соединены с выходами элементов аапрет первой группы и входами второго элемента ИЛИ, выход которого соединен со входами второго триггера и блока индикации, выход второго триггера подключен к одному из входов второго элемента Запрет первой группы, другой вход которого соединены с выходом первого элемента Запрет первой группы.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 2351О8, кл.С511 С 29/ОО, 1967.

2.Авторское свидетельство СССР № 237932, кл.СИ С 29/ОО, 1967 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приоритетного обслуживания сообщений | 1981 |

|

SU1012257A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Оптическое устройство распознавания номера движущегося объекта | 1980 |

|

SU907564A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Микропрограммный процессор | 1986 |

|

SU1365091A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| Устройство для передачи данных с самотестированием | 1988 |

|

SU1702376A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

Авторы

Даты

1980-10-23—Публикация

1978-01-05—Подача