Изобретение относится к импульсной технике, в частности к логическим устройствам, снабженным схемами встроенного контроля, и может применяться в ответственных устройствах обработки информации, например в устройствах управления движением поездов, содержащих блоки памяти на регистрах и Д-триггерах.

Цель изобретения - повышение достоверности работы путем обнаружения отказов блоков памяти.

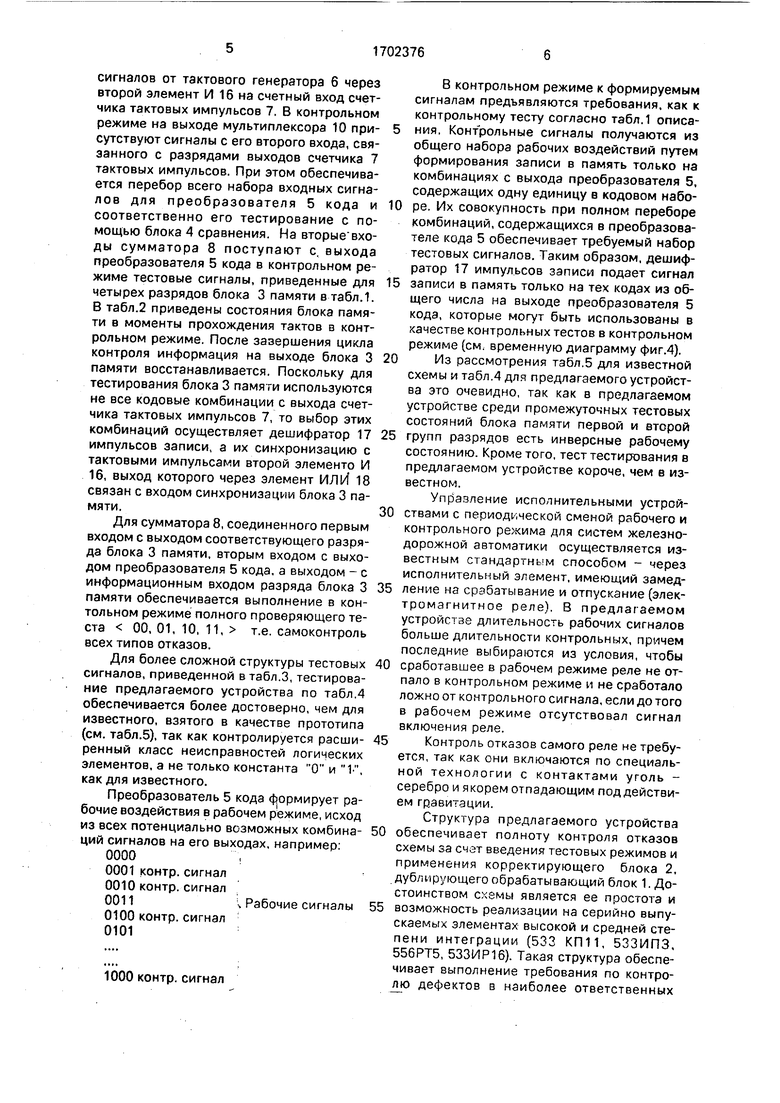

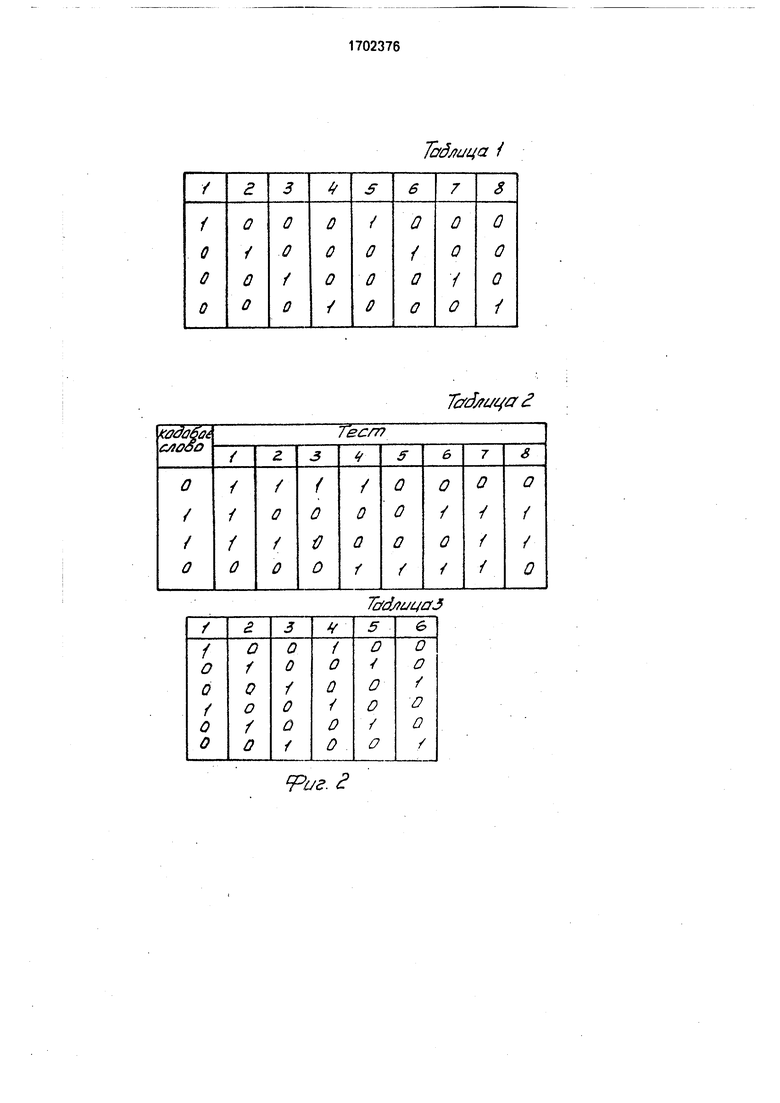

На фиг.1 приведена структурная схема устройства; на фиг.2 и 3 - приведены таблицы, поясняющие динамику работы цепей

контроля логического устройства; на фиг.4- временная диаграмма

Устройство содержит обрабатывающий 1 и кррректирующий 2 блоки, объединенные входы которых являются входом устройства. Выходы блоков 3 памяти обоих блоков 1 и 2 х подключены к первым входам блока 4 сравнения, вторые входы которого подключены к выходам преобразователей 5 кода обоих блоков 1 и 2. Выходы блока 3 памяти обрабатывающего блока 1 являются выходом устройства, а выход блока сравнения 4 является контрольным выходом устройства. Устройство содержит тактовый генератор бив обоих блоках 1 и 2 счетчик 7 тактовых имVJ о ю со VI о

пульсов и сумматор 8 по модулю два, первые входы которого подключены к выходам блока 3 памяти. Кроме того, устройство содержит датчик 9 режимов, а также в каждом из обрабатывающих 1 и корректирующих 2 блоков - мультиплексор 10, схему сравнения 11, дешифратор режима 12, коммутатор 13, блок 14 задержки, первый 15 и эторой 16 элементы И, дешифратор импульсов записи 17, элемент ИЛИ 18 и третий элемент И 19, Выход управления датчика режимов 9 в каждом из обрабатывающих 1 и корректирующих 2 блоков подключен к соответствующему входу управления мультиплексором 10, входу сброса счетчика 7 тактовых импульсов и первому входу управления дешифратора 12. Синхровход дешифратора 12 соединен с вторым входом второго 16 и первого 15 элементов И и выходом тактового генератора 6. Входы обрабатывающего 1 и корректирующего 2 блоков соединены соответственно в каждом блоке с первой группой входов мультиплексора 10, вторая группа входов которого подключена к выходам счетчика 7 тактовых импульсов и входам дешифратора 17 импульсов записи. Выход дешифратора импульсов записи соединен с первым входом второго элемента И 16, выход которого через первый элемент ИЛИ 18 связан с входом синхронизации блока 3 памяти, а второй вход элемента ИЛИ 18 каждого из блоков 1 и 2 подключен к выходу третьего элемента И 19, первый вход которого соединен с выходом записи в рабочем режиме датчика 9 режимов, а второй вход - с вторым выходом дешифратора 12.

Выходы мультиплексора 10 в каждом из блоков 1 и 2 соединены с входами преобразователя 5 кода, выходы которого соедине- ны с вторыми входами сумматора 8, первыми входами схемы 11 сравнения и входами блока 14 задержки. Выходы блока 14 задержки подключены к первым входам коммутатора 13, вторые входы которого подключены к выходам сумматора 8. Выходы коммутатора 13 подключены также в обоих блоках 1 и 2 к информационным входам блока 3 памяти, выходы которого соединены с вторыми входами схемы сравнения 11, выход которой соединен с вторым входом дешифратора 12, первый выход которого соединен с управляющим входом коммутатора 13. Выход переполнения счетчика 7 тактовых импульсов соединен с первым входом первого элемента И 15, выход которого соединен с счетным входом счетчика тактовых сигналов.

Устройство работает следующим образом.

Информация поступает одновременно на рходы обрабатывающего 1 и корректирующего 2 блоков, а результат ее обработки с выхода блока 3 памяти обрабатывающего

блока 1 управляет устройствами железнодорожной автоматики, например локомотивным светофором. Сигнал управления является достоверным, если отсутствует сигнал ошибки на выходе блока 4 сравне0 ния. Как обрабатывающий 1,таки корректирующий 2 блоки работают в двух режимах - рабочем и контрольном. Эти режимы определяют датчик 9 режимов сигналом на своем выходе управления, обеспечивающем в ра5 бочем режиме в каждом из блоков 1 и 2 поступление входной информации через первый вход мультиплексора 10 на его выход и соответственно на вход преобразователя кодов 5, Одновременно

0 осуществляется возврат в нулевое состояние счетчика тактовых импульсов 7. Преобразователь 5 кода выполняет функцию входного логического преобразователя для блока 3 памяти в структуре логичесокого

5 устройства, реализуемого схемой обрабатывающего и корректирующего блоков. Запись входных сигналов, преобразованных преобразователем кода 5 в триггере блока 3 памяти осуществляется по фронту сигналов

0 с выхода записи в рабочем режиме датчика 9 режимов. Запись осуществляется в блок 3 памяти через элемент ИЛИ 18, соединенный с входом синхронизации блока 3 памяти. Информация на информационные входы

5 блока 3 памяти поступает с выхода преобразователя 5 кода через блок 14 задержки, коммутатор 13 в случае, если в рабочем режиме схема 11 сравнения фиксирует отличие информации на выходе

0 преобразователя 5 кода и на выходе блока 3 памяти, В этом случае дешифратор 12 обеспечивает подключение к выходу коммутатора 13 его входа, связанного с выходом блока 14 задержки. Если в рабочем режиме

5 не фиксируется отличие информации, записанной в блок 3 памяти и вновь поступившей, то сигналом с второго выхода дешифратора 12 снимается единичный сигнал с входи третьего элемента И 19, что

0 соответственно приводит к запрету появления на его выходе сигнала записи от датчика 9 режимов, соединенного с вторым входом третьего элемента И 19. Тем самым обеспечивается режим хранения информации в ра5 бочем режиме.

8 контрольном режиме начинает работать счетчик тактовых импульсов 7, цикл работы которого завершается по сигналу переполнения на его выходе, обеспечивающем прекращение поступления тактовых

сигналов от тактового генератора б через второй элемент И 16 на счетный вход счетчика тактовых импульсов 7, В контрольном режиме на выходе мультиплексора 10 присутствуют сигналы с его второго входа, связанного с разрядами выходов счетчика 7 тактовых импульсов. При этом обеспечивается перебор всего набора входных сигналов для преобразователя 5 кода и соответственно его тестирование с помощью блока 4 сравнения. На вторые входы сумматора 8 поступают с. выхода преобразователя 5 кода в контрольном режиме тестовые сигналы, приведенные для четырех разрядов блока 3 памяти в табл.1. В табл.2 приведены состояния блока памяти в моменты прохождения тактов в контрольном режиме. После завершения цикла контроля информация на выходе блока 3 памяти восстанавливается. Поскольку для тестирования блока 3 памяти используются не все кодовые комбинации с выхода счетчика тактовых импульсов 7, то выбор этих комбинаций осуществляет дешифратор 17 импульсов записи, а их синхронизацию с тактовыми импульсами второй элементе И 16, выход которого через элемент И/11/f 18 связан с входом синхронизации блока 3 памяти.

Для сумматора 8, соединенного первым входом с выходом соответствующего разряда блока 3 памяти, вторым входом с выходом преобразователя 5 кода, а выходом - с информационным входом разряда блока 3 памяти обеспечивается выполнение в кон- тольном режиме полного проверяющего теста 00, 01, 10, 11, т.е. самоконтроль всех типов отказов.

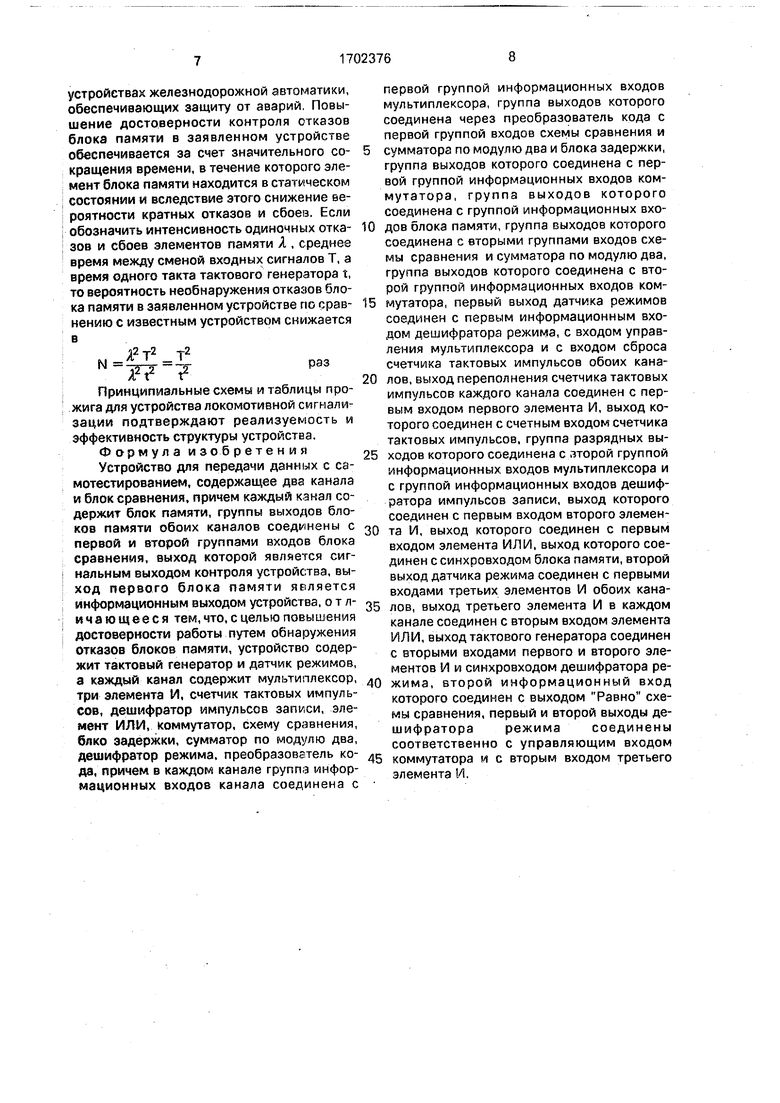

Для более сложной структуры тестовых сигналов, приведенной в табл.3, тестирование предлагаемого устройства по табл.4 обеспечивается более достоверно, чем для известного, взятого в качестве прототипа (см. табл.5), так как контролируется расширенный класс неисправностей логических элементов, а не только константа О и 1, как для известного.

Преобразователь 5 кода формирует рабочие воздействия в рабочем режиме, исход из всех потенциально возможных комбинаций сигналов на его выходах, например:

0000

0001 контр, сигнал

0010контр, сигнал

0011ч Рабочие сигналы 0100 контр, сигнал

0101

1000 контр, сигнал

В контрольном режиме к формируемым сигналам предъявляются требования, как к контрольному тесту согласно табл.1 описа- ния. Контрольные сигналы получаются из общего набора рабочих воздействий путем формирования записи в память только на комбинациях с выхода преобразователя 5, содержащих одну единицу в кодовом набо0 ре. Их совокупность при полном переборе комбинаций, содержащихся в преобразователе кода 5 обеспечивает требуемый набор тестовых сигналов. Таким образом, дешифратор 17 импульсов записи подает сигнал

5 записи в память только на тех кодах из общего числа на выходе преобразователя 5 кода, которые могут быть использованы в качестве контрольных тестов в контрольном режиме (см. временную диаграмму фиг.4).

0Из рассмотрения табл.5 для известной

схемы и табл.4 для предлагаемого устройства это очевидно, так как в предлагаемом устройстве среди промежуточных тестовых состояний блока памяти первой и второй

5 групп разрядов есть инверсные рабочему состоянию. Кроме того, тест тестирования в предлагаемом устройстве короче, чем в известном.

Управление исполнительными устрой0 ствами с периодической сменой рабочего и контрольного режима для систем железнодорожной автоматики осуществляется известным стандартным способом - через исполнительный элемент, имеющий замед5 ленпе на срабатывание и отпускание (электромагнитное реле). В предлагаемом устройстве длительность рабочих сигналов больше длительности контрольных, причем последние выбираются из условия, чтобы

0 сработавшее в рабочем режиме реле не отпало в контрольном режиме и не сработало ложно от контрольного сигнала, если до того в рабочем режиме отсутствовал сигнал включения реле.

5Контроль отказов самого реле не требуется, так как они включаются по специальной технологии с контактами уголь - серебро и якорем отпадающим под действием гравитации.

Структура предлагаемого устройства

0 обеспечивает полноту контроля отказов схемы за счот введения тестовых режимов и применения корректирующего блока 2, дублирующего обрабатывающий блок 1. Достоинством схемы является ее простота и

5 возможность реализации на серийно выпускаемых элементах высокой и средней степени интеграции (533 КП11, 533ИПЗ, 556РТ5, 533ИР16). Такая структура обеспечивает выполнение требования по контролю дефектов в наиболее ответственных

устройствах железнодорожной автоматики, обеспечивающих защиту от аварий. Повышение достоверности контроля отказов блока памяти в заявленном устройстве обеспечивается за счет значительного сокращения времени, в течение которого элемент блока памяти находится в статическом состоянии и вследствие этого снижение вероятности кратных отказов и сбоев. Если обозначить интенсивность одиночных отказов и сбоев элементов памяти А , среднее время между сменой входных сигналов Т, а время одного такта тактового генератора t, то вероятность необнаружения отказов блока памяти в заявленном устройстве по сравнению с известным устройством снижается в

N :

раз

Aztz t2

Принципиальные схемы и таблицы прожига для устройства локомотивной сигнализации подтверждают реализуемость и эффективность структуры устройства. Формула изобретения Устройство для передачи данных с самотестированием, содержащее два канала и блок сравнения, причем каждый какал содержит блок памяти, группы выходов блоков памяти обоих каналов соединены с первой и второй группами входов блока сравнения, выход которой является сигнальным выходом контроля устройства, выход первого блока памяти является информационным выходом устройства, отличающееся тем, что, с целью повышения достоверности работы путем обнаружения отказов блоков памяти, устройство содержит тактовый генератор и датчик режимов, а каждый канал содержит мультиплексор, три элемента И, счетчик тактовых импульсов, дешифратор импульсов записи, элемент ИЛИ, коммутатор, схему сравнения, блко задержки, сумматор по модулю два, дешифратор режима, преобразователь кода, причем в каждом канале группа информационных входов канала соединена с

первой группой информационных входов мультиплексора, группа выходов которого соединена через преобразователь кода с первой группой входов схемы сравнения и

сумматора по модулю два и блока задержки, группа выходов которого соединена с первой группой информационных входов коммутатора, группа выходов которого соединена с группой информационных входов блока памяти, группа выходов которого соединена с вторыми группами входов схемы сравнения и сумматора по модулю два, группа выходов которого соединена с второй группой информационных входов коммутатора, первый выход датчика режимов соединен с первым информационным входом дешифратора режима, с входом управления мультиплексора и с входом сброса счетчика тактовых импульсов обоих каналов, выход переполнения счетчика тактовых импульсов каждого канала соединен с первым входом первого элемента И, выход которого соединен с счетным входом счетчика тактовых импульсов, группа разрядных выходов которого соединена с зторой группой информационных входов мультиплексора и с группой информационных входов дешифратора импульсов записи, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен ссинхровходом блока памяти, второй выход датчика режима соединен с первыми входами третьих элементов И обоих каналов, выход третьего элемента И в каждом канале соединен с вторым входом элемента ИЛИ, выход тактового генератора соединен с вторыми входами первого и второго элементов И и синхровходом дешифратора режима, второй информационный вход которого соединен с выходом Равно схемы сравнения, первый и второй выходы дешифратора режима соединены соответственно с управляющим входом

коммутатора и с вторым входом третьего элемента И.

I

N

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1683015A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

Изобретение относится к импульсной технике, в частности к логическим устройствам, снабженным схемами встроенного контроля, и может применяться в устройствах управления движением поездов. Цель изобретения - повышение достоверности работы путем обнаружения отказов блоков памяти. Устройство содержит блок сравнения, датчик режимов, тактовый генератор, обрабатывающий и корректирующий блоки, каждый из которых содержит мультиплексор, преобразователь кода, схему сравнения, сумматор по модулю два, блок памяти, дешифратор режима, коммутатор, счетчик тактовых сигналов, дешифратор импульсов записи, элемент ИЛИ, три элемента И. 4 ил. КЛ

I

If

II Г

V

.г

Тадмца /

Т0&ицс(3

tpt/г.З

7аЈлща fy

Tad/tuna 5

Рабочий режим

Контрольный режим

счетч. т акт, сигн.7

шишлллллляп.

Выделит, имп. зап.

&ППЛЛЛ

И

лгит

ЛЛЛЛГ

ФигЛ

| Сапожников В.В., Сапожников Вл | |||

| В | |||

| Методы синтеза надежных автоматов Л,; Энергия, 1980 | |||

| Е.Е.Гелбштейн и др | |||

| Использование микропроцессоров с программным управлением для обеспечения безопасности движения поездов | |||

| - Железные дороги мира, М.: 1976 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1991-12-30—Публикация

1988-12-29—Подача