ков II хранения констант, сумматор 12, умножитель 13, блок 17 масштабирования чисел, две группы мультиплексоров 14 и 16, два регистра 8 и 9, введены

1 1

Изобретение относится к вычислительной технике и предназначено для вычисления функций из заданного набора от массивов значений аргументов, представленных в модулярной системе счисления.

Цель изобретения - повышение быстродействия.

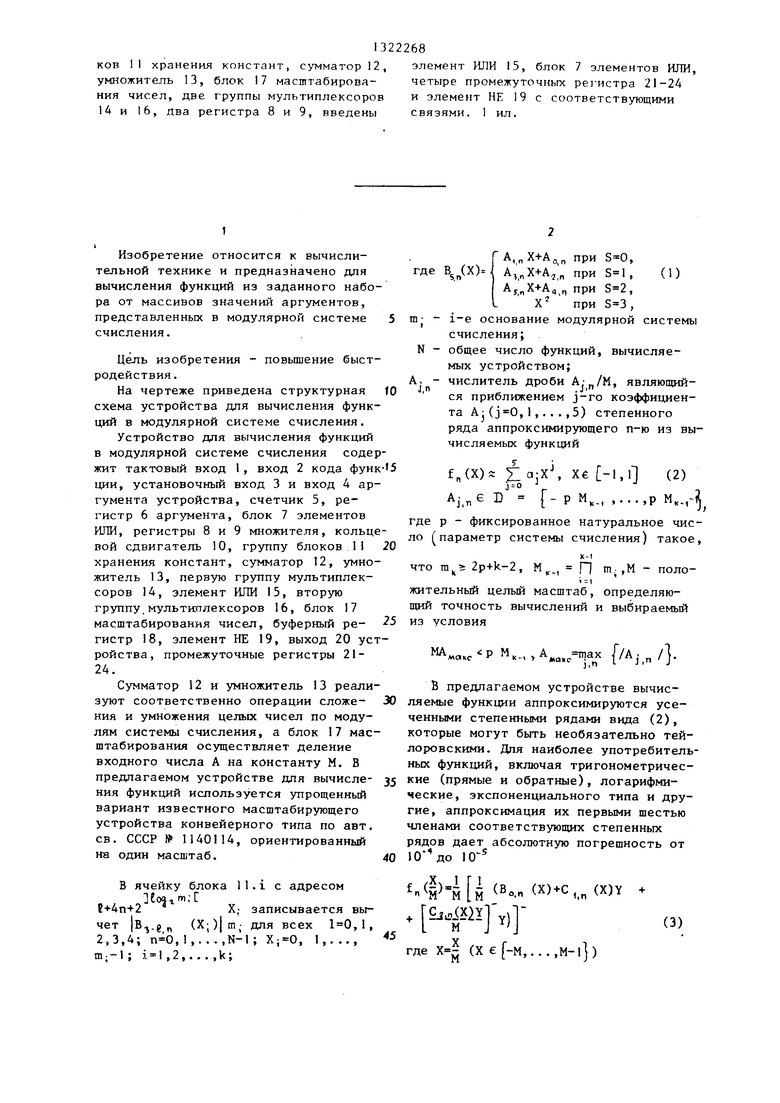

На чертеже приведена структурная схема устройства для вычисления функций в модулярной системе счисления.

Устройство для вычисления функций в модулярной системе счисления содержит тактовый вход 1 , вход 2 кода функ ции, установочный вход 3 и вход 4 аргумента устройства, счетчик 5, регистр 6 аргумента, блок 7 элементов ИЛИ, регистры 8 и 9 множителя, кольцевой сдвигатель 10, группу блоков 11 хранения констант, сумматор 12, умножитель 13, первую группу мультиплексоров 14, элемент ИЛИ 15, вторую группу,мультиплексоров 16, блок 17 масштабирования чисел, буферный ре- гистр 18, элемент НЕ 19, выход 20 устройства, промежуточные регистры 21- 24.

Сумматор 12 и умножитель 13 реализуют соответственно операции сложа- ния и умножения целых чисел по модулям системы счисления, а блок 17 масштабирования осуществляет деление входного числа А на константу М. В предлагаемом устройстве для вычисления функций используется упрощенный вариант известного масштабирующего устройства конвейерного типа по авт. св. СССР № 1140114, ориентированный на один масштаб.

-«-4п-ь2

IB

чет

В ячейку блока 11.i с адресом

.-C

Л;

(Х;)|т,

j-e,n

записывается вы- для всех ,1,

2,3,4; ,,...,N-l; , I,..., ,2,...,k;

элемент ИЛИ 15, блок 7 элементов ИЛИ, четыре промежуточных pei-истра 21-24 и элемент НЕ 19 с соответствующими связями. 1 ил.

где В, (Х),

s.n

А,„Х+А,,„ при , А, при , (1)

А „Х-ьА при , Х при 5-3, ш; - i-e основание модулярной системы

счисления;

N - общее число функций, вычисляемых устройством;

А, - числитель дроби А /М, являющийся приближением j-ro коэффициента А:(,1,...,5) степенного ряда аппроксимирующего п-ю из вычисляемых функций

„(Х)г ajX Хе -1,1 (2)

D f- р М,.,р м,.,

где р - фиксированное натуральное число (параметр системы счисления) такое

К-1

что 2p+k-2, М ., П Ш; ,М - поло 1

жительный целый масштаб, определяющий точность вычислений и выбираемый из условия

WA axc P

к-. А,1Пах

.

В предлагаемом устройстве вычисляемые функции аппроксимируются усеченными степенными рядами вида (2), которые могут быть необязательно тейлоровскими. Для наиболее употребительных функций, включая тригонометрические (прямые и обратные), логарифмические, экспоненциального типа и другие, аппроксимация их первыми шестью членами соответствующих степенных рядов дает абсолютную погрешность от 10 до 10

°. W.C,(X)Y

. С,,ШУ)где Х (X ef-M,...,M-l)

(3)

С ,х)4ЬпШГ с fx)-| - I м I . м

Y 3

|й

.-

Устройство для вычисления функ- ций н модулярной системе счисления работав слодутоп .нм образом.

Для приведения устройства в исходное состояние в кольцевой сдвигатель

10посредством установочного входа 3 устройства записывается двоичный код единицы и после этого начинается цик- лическт процесс формирования требуемой последовательности функциональных значений. В пределах каждого цикла длиной в пять тактов вьтолняется один и тот же набор действий.

На всех тактах сумматор 12 осуществляет сложение по основаниям системы счисления величин, поступающих с вы- хода блока 7 элементов ИЛИ и буферного регистра 18, а умножитель 13 находит модулярный код произведения чисел, поступающих с выходов блока 17 масштабирования и группы мультиплексоров 14. При этом модулярньш код суммы с выхода сумматора 12 подается в первый промежуточньй регистр 21 и iHa второй информационный вход группы (мультиплексоров 16, а модулярный код произведения запоминается в буферном регистре 18.

Полезную работу сумматор 12 выполняет на нулевом, первом и четвертом, а умножитель 13 - на нулевом, втором и четвертом тактах циклов (такты циклов нумеруются, начиная с нуля) На каждом такте работы устройства содержимое счетчика 5, подается на младшие разряды адресного входа блоков

11хранения константы, а на старшие разряды их адресных входов с выхода регистра 6 аргумента подается записанный в нем модулярный код некоторого числа ХбВи из блока ll.i считьшается i-я ид1фра модулярного кода числа В. (X). Модулярный код этого числа с выхода блоков 11 поступает на информационный вход второго , промежуточного регистра 22 и первый информационный вход группы мультиплексоров 16.

На всех тактах управляющие сигналы (J(5 - б . , сформированные в разрядах с нулевого по четвертый кольцевого сдвигателя 10, непосредственно или через логические элементы 15 и 19 подаются на управляющие входы соответ

25

5

Ю 5

20 30 35. 40

4550 ствующих блоков: Gp - пя управляющие входы приема кода счетчика 5, регистра 6 и первый вход элемента ИЛИ 15; G, - на входы разрещенил приема ре- г истров 21 и 23 и выдачи регистрА 24; G. - на селекторный вход группы мультиплексоров 1А; С. - на управляющд1е входы приема кода регистров 8 и 9 и вход элемента НЕ 19; G - на входы разрешения приема регистров 22 и 24 и выдачи регистра 23 и второй вход элемента ИЛИ 15. После этого по сигналу, подаваемому через тактовый вход 1 устройства на счетные входы счетчика 5 и сдвигателя 10, содержимое первого из них увеличивается на единицу, а второго - сдвигается на один разряд в сторону старших разря- дов.

Согласно изложенному выше на начальном (нулевом) такте работы устройства в счетчик 5 посредством входа 2 кода функции устройства записывается двоичный код числа 4п, а в регистр 6 через вход 4 аргумента устройства принимается модулярный код (Х| ,Х,. . . ,Х.) числа X, определяющего требуемое значение Х/М аргумента X функции. На последующих трех тактах (с первого по четвертый) блоки 11 хранения констант формируют соответ- ственно модулярные коды величин Х,

В.Х). Bi,n(X) и В„п(Х) (см. (О) и, так как на селектор ный вход группы мультиплексоров 16 с выхода элемента ИЛИ 15 в первом, втором и третьем тактах поступает нулевой сигнал, то модулярные коды первых трех из указанных величин через первый информационный вход группы мультиплексоров 16 пройдут на ее выход и поступят во входной регистр блока 17 масштабирования.

На четвертом такте 0 1, поэтому модулярный код величины В(Х) с выходов блоков 11 хранения констант поступит в регистр 22, при этом прежнее содержимое регистра 22 пересылается в регистр 24, а содержимое регистра 23 через первый вход элементов ИЛИ 7 подается на второй вход сумматора 12, на первый вход которого подается содержимое буферного регистра 18. Результат суммирования (его значение в данный момент несущественно) с выхода сумматора 12 через второй информационный вход группы мультиплексоров 16 передается в блок 17 масштабирования чисел.

В ходе тактов с пятого по девятьй составляющих второй цикл работы устройства, описанные действия повторя- ются для второго элемента последовательности функциональных значений, подлежащих вычислению. Начиная с восьмого такта, с выхода блока 17 масштабирования чисел начнут поступать про- масштабированные значения входных величин блока в порядке поступления последних на вход. В частности на восьмом такте на выходе блока 17 сформируется модулярный код величины Y (см.(4)), который подается на второй вход умножителя 13 и ввиду и 1 записывается в регистр 8 с одновременной пересылкой прежнего его содержимого в регистр 8.В девятом такте на второй вход умножителя 13 с блока 17 поступает величина C,ri(X (см. (4)) и, так как в данный момент на селекторный вход группы мультиплексоров 14 подается сигнал 1о. 0, то на первый вход умножителя I3 через информационньй вход 1 руппы мультиплексоров 14 поступит содержимое регистра 8.

Умножитель 13 получает модулярный код произведения С, (X)Y, который, запоминается в буферном регистре 18 (на управляющий вход приема кода регистра 18 с выхода элемента НЕ 19 подает- ся сигн.ал ). Одновременно с этим на девятом такте в регистр 22 с выхода блоков I1 хранения констант передается величина вида (1) при S 3, необходимая для вычисления второго функционального значения, а прежнее содержимое регистра 22 пересылается в регистр 24.

В ходе третьего цикла (такты с де сятого по четырнадцатый) наряду с выполнением описанных действий в связи с выполнением третьего функционального значения в десятом такте сумматор 12, складьгаая содержимое регист- ра 1В с выходной величиной блока 7 элементов ИЛИ (на нулевом такте каждого цикла она равна нулю), получает модулярный код числа C(X)Y, который через второй информационный вход группы мультиплексоров 16 передается в блок 17 масштабирования (ввиду(5 0), умножитель 13 находит модулярный код произведения чисел С,,п(Х)

и Y, запоминаемый в ре(см. (4)) гистре 18.

В одиннадцатом такте сигнал О, 1, в результате чего величина Вд(Х) из регистра 24 через второй вход элементов ИЛИ 7 пройдет на выход и поступит на вход сумматора 12, на другой вход которого с выхода буферного регистра 18 подается величина (X)Y, сумматор 12 находит модулярный код числа BU (X)+C,(X)Y, который поступает в регистр 21 с одновременной пересылкой его прежнего содержимого в регистр 23. На тринадцатом такте в регистр 8 с выхода блока I7 передается промасштабированное значение квадрата аргумента второй функции, а код числа Y из регистра 8 пересылается в регистр 9 ().

В ходе четвертого цикла работы устройства (такты с пятнадцатого по девятнадцатый) наряду с действиями, выполняемыми в связи с выполнением второго, третьего и четвертого функциональных значений осуществляется следующее. На семнадцатом такте с выхода блока 17 на вход умножителя 13 поступает модулярньй код величины

Гс,п(Х) Yl МJ

на другой вход умножителя 13 через информационный вход группы мультиплексоров 14 (G) подается содержимое регистра 9, умножитель 13 получает модулярный код произведения

r.C2a(X)Y. М

Y, который запоминается в

буферном регистре 18, где он хранится в течение следующего такта (на во- семнадцат рм такте запись в регистр 18 ввиду«5j 0 запрещена).

На девятнадцатом такте при записи в регистр 22 новой информации содержимое регистра 23 через первый вход элементов ИЛИ 7 подается на вход сумматора 12, а на другой его вход подается содержимое буферного регистра 18. Код, получаемьй сумматором 12 через второй информационный вход группы мультиплексоров 16, передается в блок 17 масштабирования чисел, который по истечении двадцать пятого такта завершит вычисление первого элемента заданной последовательности функциональных значений (см. (3)), при этом модулярный код искомого зна - чения числителя дроби (3) снимается с выхода 22 устройства, модулярный

код ( Функ11ио1 а. значения () снимается с выхидл 22 vcгрой- стна по истечении (15--5)-гст такта.

Ф

е т е и и

рмула изобр

Устройство для вычисления функци

в модулярной системе счисления, содержащее счетчик, колг-цевой сдвига- тель, группу блоков хране шя констант, сумматор, умножитель, блок ма штабирования чисел, две группы мультиплексоров, два регистра множителя регистр аргумента и буферный регист причем тактовый вход устройства соединен со счетным входом счетчика,ра ряды выхода которого соединены с младшими разрядами адресного входа блоков хранения констант группы, выход первого регистра множителя соеднен с информационным входом второго регистра множителя, выход которого соединен с первыми информационными входами мультиплексоров первой группы, выходы которых соединены с входом первого сомножителя умножителя, выход которого соединен с информационным входом буферного регистра, выход которого соединен с входом певого слагаемого сумматора, выходы блоков хранения констант группы соединены с первыми информационными вхдами соответств тощих мультиплексоро второй группы, выход блока масштабирования чисел является выходом устройства , отличающееся тем что, с целью повьццения быстродействи оно содержит элемент ИЛИ, блок элементов ИЛИ, четыре промежуточных регистра и элемент НЕ, причем тактовый вход устройства соединен с входом разрешения сдвига кольцевого сдвига- теля, информационный вход которого соединен с установочным входом устройства, входы кода функции и аргумента которого соединены соответственно с информационными входами счетчика и регистра аргумента, разряды выхода которого соединены соответственно со старшими разрядами адресного входа блоков хранения констант

Составите Редактор .П.Гереши Техред Л.О

Заказ 2865/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д.4/5

Производственно-полиграфическое предприятие, г.Ужгород,ул.Проектная, it

25

5

fO J5 20

222688

I pyriribi, выход сумматора (пединен го вторыми информационными входами мультиплексоров второй группы и с информационным входом первого промежуточ- 5 ного регистра, выходы мультиплексоров второй группы соединены с входом блока масгатабирования чисел, выход которого соединен с входом второго сомножителя умножителя и с информационным входом первого регистра множителя , выход которого соединен с вторыми информаци- оН}1ыми входами мультинлексоров первой группы, выходы блоков хранения констант группы соединены с информационным входом второго промежуточного регистра, выходы первого и второго промежуточных регистров соединены соответственно с информационными входами третьего и четвертого промежуточных регистров, выходы которых соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход которого соединен с входом второго слагаемого сумматора, разряды выхода кольцевого сдвигателя соединены соответственно с первым входом элемента ИЛИ, с входом разрешения приема первого промежуточного регистра, с управляющим входом мультиплексоров первой группы, с входом элемента НЕ и с вторым входом элемента ИЛИ, выход которого соединен с управляющим входом мультиплексоров второй группы, входы разрешения приема регистра аргумента и счетчика соединены с первым входом элемента ИЛИ, второй вход которого соединен с входами разрешения приема второго и четвертого промежуточных регистров и с входом разрешения выдачи третьего промежуточного регистра, вход разрешения приема которого соединен с входом разрешения приема первого промежуточного регистра и с входом разрешения вьщачи четвертого про- 45 межуточного регистра, вход элемента НЕ соединен с входами разрешения приема первого и второго регистров множи-, теля, выход элемента НЕ соединен с входом разрешения приема буферного регистра.

30

35

40

50

Корректор Л. Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для вычисления дискретного преобразования Фурье в модулярной системе счисления | 1988 |

|

SU1633423A1 |

| Устройство для вычисления элементарных функций в модулярной системе счисления | 1985 |

|

SU1291977A1 |

| Устройство для масштабирования чисел | 1989 |

|

SU1667066A1 |

Изобретение отиосится к вычислительной технике и предназначено для вычисления функций из заданного набора от массивов значений аргументов, представленных в модулярной системе счисления. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее счетчик 5, кольцевой сдвигатель 10, группу бло

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1985-08-01—Подача