. . . / . Изобретение относится к области ( v

фазоизмерительной техники и может найти применение для контроля установки фаз на выходах передающих станций, работающих на сложение мощное- S ,тей в эфире.

Известно устройство измерения сдвига фаз, которое может быть использовано при контроле фазирования и позволяющее за один период исследу- 10 емого сигнала измерить сдвиг фазы радиоимпульсного напряжения относительно непрерывного опорного сигнала и содержгодее два формирователя, триггер, генератор опорных импульсов, |5 схему совпадения и цифровой отсчетный блок f 1 .

Недостатком устройства является невозможность измерять сдвиг фазы между двумя радиоимпульсными напря- jO пениями, существующими неодновременно.

Известно устройство контроля фазирования, содержащее -два усилителяограничителя, выходной формирователь,25 элемент совпадения, счетчик фазы, блок индикации и генератор счетных импульсов t2j.

Недостатком устройства является значительное время, затрачиваемое .30

оператором на фазирование отдельных систем.

. Целью настоящего изобретения является повышение быстродей.ствия конт-. роля фазирования системы передающих станций.

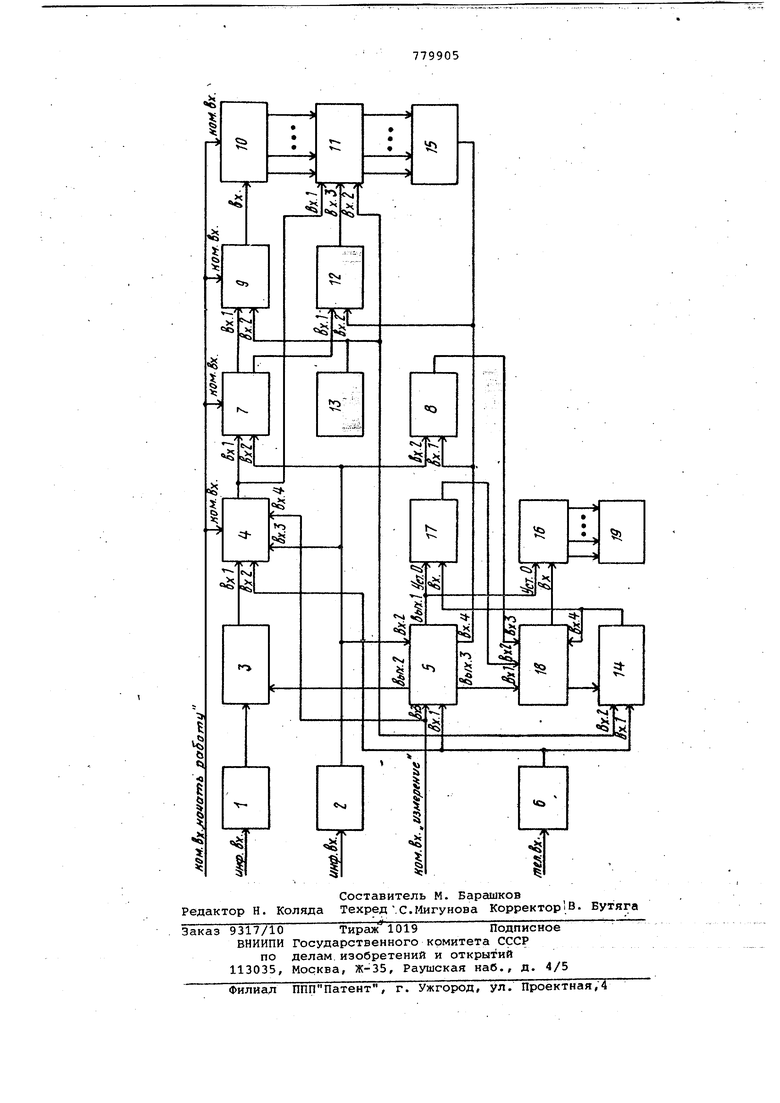

Поставленная цель достигается тем, ЧТО устройство, содержащее первый и второй усилители-ограничители, выход второго из них соединен с ;одним из входом выходного формирователя, первый элемент совпадения, счетчик Фазы, соедийенный со входами блока цифровой индикации и генератор счетных импульсов, снабжено блоком регулируемой задержки,Управляемым инвертором, блоком исключения грубой - оиибки, блоком разрешения измерений, фор мирователем импульсов, делителем,регистром, вычитающим счетчиком, элементом ИЛИ, вторым элементом совпадения, счетчиком временного интервала и блоком введения поправок, прИчем выход первого усилителя-ограничителя соединен с одним из входов управляемого инвертора, второй вход которого соединен с вторьим выходом блока исключения грубой ошибки, а выход - с первым входом блока регулируемой задержки, второй вход кото РОЙ присоединен к первым входам бло ка исключения грубой ошибки и первого элемента совпадения и к выходу блока разрешения измерений, BTopdro усилителя-ограничителя соединен с третьим входом блока регулируемой задержки и со вторыми входами формирователя импульсов и блока искл ючения грубой ошибки, третий вход которого присоединен к четвертому входу блока регулируеомй задержки, выход которого соединен с первыми- входами вычитающего счетчика и формирователя импульсов, первый и второй выходы которого подсоединены соответственно к одним из входов делителя и элемента ИЛИ, выход делителя через регистр соединен с входом числа вычитающего сумматора, второй вход которого соединен с генератором с : етных импульсов и вторыми входами делителя и первого элемента совпадения, третий - с выходом элемента ИЛИ,а выход - через второй элемент совпадения соединен с другими входами элемента ИЛИ и выходного формирователя., а также-С четвертым входом блока исключения грубой ошибки, первый и третий выходы которого соединены соответственно с одними из входов счетчика временного интервала и счетчика фазы и первым входом блока введения поправки, второй, третий и четвертый входы которого соединены соответственно с выходом счетчика временных интервалов, с выходом выходного формирователя, с выходом пер вого элемента совпадения и вторым входом счетчика времени интервалов, один выход его подсоединен к третьему входу первого элемента совпадения а другой - ко второму входу счетчика фазы, входы синхронизации блока регулируемой задержки, формйрбвателя импульсов, делителя и регистра объединены. , На чертеже представлена блок-схема устройства для контроля фазирования системы передающих станций. Устройство контроля фазирования системы передающих станций содержит первый и второй усилители-ограничители 1 и 2, .управляемый инвертор 3, блок с регулируемой задержкой 4,блок исключения грубой ошибки 5, блок раз решения измерений б, формирователь импульсов 7, выходной формирователь 8, делитель 9, регистр 10, вычитающий счетчик 11, элемент ИЛИ 12, гене ратор счетных импульсов 13, первый элемент совпадения.14, второй элемен совпадения 15, фазы 16, счет чик временного интервала 17, блок введения поправки 18 и блок цифровой индикации 19. . Работа устройства происходит следующим образом. На вход первого усилителя-рг1раничителя 1 постоянно подается сигнал, который с некоторыми задержками повторяется на выходах передающих станций контролируемой системы. Последовательность импульсов с выхода усилителя-ограничителя 1 проходит без изменения через управляемый инвертор 3 на первый вход блока регулируемой задерхски 4, а с выхода усилителя-ограничителя 2 поступает на пятый вход блока 4. ;- Для запоминания фазы опорной ПС достаточно определить и затем перио;дически воспроизводить временной интервал t мехсду положительными фронтами импульсов последовательностей. Для уменьшения влияния помех интервал необходимо определять как среднюю величину за некоторое число периодов исследуемого сигнала. В случае малого сдвига между импульсами возможно, что из-за влияния помех интервал f определится как средняя величина между величинами, часть из которых близка к б, а другая часть к периоду исследуемых синалов. Следовательно, определяемая величина будет иметь некоторое случайное значение , Необходимо определить и исключить случаи, приводящие к указанному результату. После получения команды Начать работу регистр 10, делитель 9 и формирователь импульсов 7 устанавливаются в исходное состояние, а в блоке 4 вырабатывается последовательность импульсов, положительные фронты которых задержаны. В соответствии с телеграфным сигналом на входе блока разрешения измерения бив зависимости от условий связи, БРИ б выдает на второй вход БРЗ 4 сигнал, разрешающий производить измерения. Этот сигнал выдается в течение в эемёни, когда на информационные входы устройства поступают сигналы одной и той же радиотелеграф-г ной посылки и уровень их достигает необходимого значения. В течение времени воздействия на второй вход блока 4 сигнала, разрешающего измерение, последовательность импульсов поступает на первый вход формирователя импульсов 7. На выходе формирователя 7 вырабатывается п импульсов. В течение длительности этих импульсов, подаваемых на первый вход делителя 9 с коэффициентом деления п , на второй вход регистра 10 разрешается прохождение счетных импульсов, поступающих от генератора счетных импульсов 13 на второй вход делителя .9. Частота следования счетных импульсов много больше частоты исследуемых сигналов. Таким образом, в регистре 10 записывается число,, соответствующее средней задержке положительных фронтов импульсов. До момента окончания п-го импульса на одном выходе формирователя 7, сигнал с другого его выхода, поступая через элемент ИЛИ 12 . :На третий вход вычитающего счетчика 11, разрешает параллельную перепись содержания регистра 10 в счетчик 11. Начиная с момента окончания п-го пульса сигнал, поступающий на вход усилителя-ограничителя 2 от опорной передающей станции, не нужен.

После поступления положительного фронта импульса из последовательности , используемой для запоминания фазьа, на первый вход вычитающего счетчика 11 и в результате поступления счетных импульсов на второй его вход происходит вычитание из числа, запи санного в счетчик 11. В момент установки всех разрядов счетчика 11 в нулевое состояние, на выходе второго элемента совпадения 15 вырабатывается импульс, который воздействует через элемент ИЛИ 12 на третий вход счетчика 11, вызывая перепись содержания регистра 10 в счетчик 11.В дальнейшем описанный процесс периодически повторяется.

Далее вместо сигнала с выхода опорной станции на вход ограничителя 2 подается сигнал с выхода станции, расфазирование которой относительно опорной требуется измерить. Если фаза сигнала близка к фазе опорной, то в результате воздействия помех, временной интервал, соответствующий измеряемому расфазированию, может соответствовать либо величине близкой к О, либо к периоду исследуемого сигнала. Средняя величина этого временного интервала за некоторое число периодов исследуемого сигнала может быть случайной величиной, что объясняет возможность появленияг рубой ошибки при измерении.Необходимо исключить такие случаи.После получения команды измерение и сигнала разрешения .измерения с выхода блока 6, :блок 4 уменьшает заде1ржку положительного фронта одного импульса из последовательности,используемой для запом нания фазы опорной ПС. В результате этого один из импульсов с выхода второго элемента совпадения 15 придет на четвертый вход блока 5 с onepexteнием на некоторую величину. Если в течение времени, превышающего вдвое :время с момента прихода этого импульса, на второй вход блока 5 придет положительный фронт, то это оз-i начает возможность появления грубой ошибки при измерении. Для исключения возможности такой ошибки на первый вход блока введения поправки 18 с третьего выхода блока 5 выдается соответствующий сигнал, а на вход управления инвертора 3 до конца измерения подается постоянный сигнал, приводящий к инвертированию последовательности импульсов, проходящих на первый вход блока 4. В результате

такого инвертирования, изменение положения во времени импульсов на выходе второго элемента совпс1дения 15 соответствует 180 фазовому сдвигу сигнала опорной станции. После окончания процесса определения возможности грубой ошибки, сигнал с первого выхода блока 5 разрешает запись счетных импульсов, которые поступают на вторые входы счетчика временных интервалов 17 и счетчик фазн 16 в теoчение времени выдачи сигнала разрешения на первый вход первого элемента совпадения 14. Счетные импульсы на второй вход счетчика 17 поступают непосредственно с выхода второго элемента 14, а на второй вход счетчика

5 16 поступают через блок 18, но только в течение длительности импульсов, поступающих с выхода формирователя 8 на третий вход блока 18..Начало импульсов ни выходе формирователя 8

0 соответствует началу импульсов на .его первом входе, а конец - соответствует положительному фронту на втором его входе.

В момент заполнения счетчика 17

5 на второй вход блока 18 поступает сигнал, по которому импульсы на второй вход счетчика 16 начинают проходить непрерывно, но с частотой в два раза меньше, чем йа второй вход счет0чика 17. За время повторного заполнения счетчика 17 емкостью 3,6-10 (где К - целое положительное число) на счетчик 16 пройдет дополнительно 1,8-10 импульсов, причем в случае

5 заполнения счетчика 16 емкостью 3, разряды его устанавливаются в исходное (нулевое)состояние и запись импульсов продолжается. Сигнал, поступающий на второй вход блока 18

0 в момент повторного заполнения счетчика 17, приводит к выдаче на третий вход первого эз1еме 1:а 14 сигнала, запрещающего прохождение счетных импульсов на его выход. Число, записанное в трех старших десятичных разря5дах счетчика 16,отображается с помощью блока цифровой индикации 19 и соответствует в градусах расфазированию измеряемой станции относительно опорной. Измерение расфазирования

0 данной станции заканчивается, прекращается подача сигнала с ее выхода на вход ограничителя 2, одновременно прекращается подача команды измерение , в результате чего блок 5 уста5навливается в исходное состояние, а сигнал с первого его выхода устанав ливает счетчики 16 и 17 в исходные (нулевые) Состояния. После подачи на вход ограничителя 2 сигнала с выхода

0 станции, расфазироваиие которой требуется измерить, вьщача сигнала измерение возобновляется и процесс измерения повторяется.

Применение изобретения позволит обеспечить автоматический контроль

5 фазирования системы передающих станций , работаютих в телеграфных режимах при наличии значительных шумовых помех в каналах передачи сигнала с выходов Передающих станций на вход коктролируйадей аппаратуры. Автоматизация процесса контроля уменьшает загрузку оператора, исключает возможность возникновения субъективных ошибок , позволяет уменьши время контроля системы ПС-ПС, что имеет большое значение в случае конТ роля системы перед сеансом связи. Формула изобретения Устройство контроля фазирования системы переданлпих станций, содержащее первый и второй усилители-ограни чители, вахОд второго из них Соединен с одним из входов выходного фор мирователя, первый элемент совпадения, счетчик фазы, соединенный сО входами блока цифровой индикации и .генератор счётных импульсов, о т л и ч а ю щ е е с я тем, что, с Целью повышения быстродействия, оно снабжено блоком регулируемой задержки, Управляемым инвертором, блоком исклю чения грубой ошибки, блоком разрешения измерений, формирователем импуль сов, делителем, регистром, вычитающим счетчиком, элементом ИЛИ,вторым элементом совпадения, счетчиком временного интервала и блоком введения поправок, причем выход первого усилителя-ограничителя соединен с одним из входов управляемого инвертора, второй вход которого соединен с втоРЬ1М выходом блок-а исключения грубой ошибки, а выход - с первым вводом блока регулируемой задержки, второй вход которой присоединен к первым входам блока исключения грубой ошибк Тйг первого элемента совпадения и к вы ходу блока разрешения измерений,выХОД второго усилителя-ограничителя соединен с третьим входом блока регулируемой задержки и со вторыми входами формирователя импульсов и блока исключения грубой ошибки, третий вход которого Присоединен к четвертому входу блока регулируемой задержки, выход которого соединен с первыми входам вычитающего счетчика и формирователя импульсов, первый и вто. рой выходы которого присоединены dooTветственно к одним из входов делителя и элемента ИЛИ, выход делителя через регистр соединен с входом числа вычитающего сзчетчика, второй вход которого соединен с генератором счетныз импульсов и вторыми входами делителя и первого элемента совпадения, третий - с выходом элемента ИЛИ, а выход - через второй элемент совпадения соёдйн ён с другими входами элемента ИЛИ и выходного формирователя, а также с четвертым входом блока исключения грубой ошибки, первый и третий выходы которого соединены соответственно с одними из входов счетчика Временного интервала, .и счетчика фазы и первш входом блока введения поправки, второй, третий и четвертый взгоды которого соединены соответственно с,выходом счетчика временных интервалов, с выходом выходного формйрОвателя, с выходом первого элемента совпадения и вторым входом, счетчика временных интервалов, один выход его подсоединен к третьему вхрду первого элемента совпадения, а другой ко второму входу счётчика фазы,входы синхронизации блока регулируемой задержки, формирователя импульсов, дедителя и регистра объединены. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 359619, Кл. G 01 R 25/04, 1972. 2. Вопросы радиоэлектроники,серия ТРС 1976, № 5, с, 177.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазирования шкалы времени электронных часов | 1982 |

|

SU1084720A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство фазирования по циклам | 1988 |

|

SU1601773A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Протонный магнитометр | 1980 |

|

SU938227A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство дискретного фазирования | 1980 |

|

SU1016847A1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1985 |

|

SU1840278A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

Авторы

Даты

1980-11-15—Публикация

1978-09-05—Подача