а

CD

ел

Од

Изобретение относится к электросвязи и может быть использовано в мнороканальных синхронно-адресных системах связи с временным разделе- нием каналов, в которых обмен иафор- наплей между несколькими приемо- переданшщми станциями осуществляется на одной частоте в неперекрывающихся интервалах времени.

Целью изобретения является повышение устойчивости синхронизации.

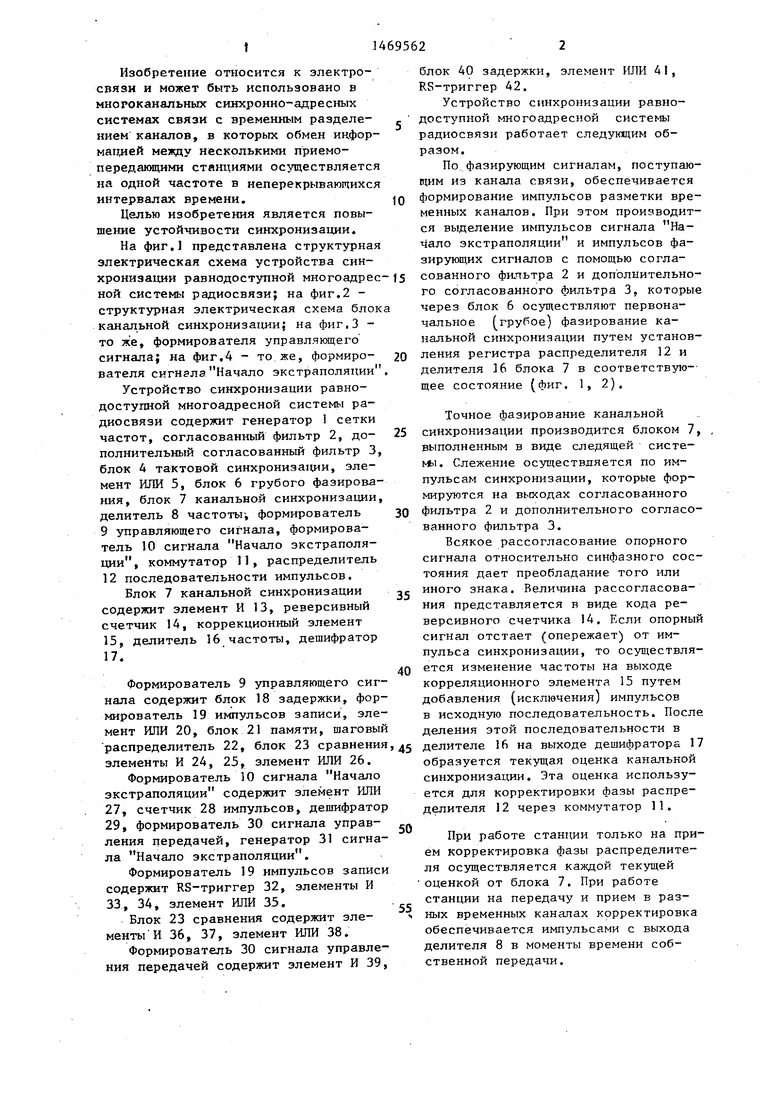

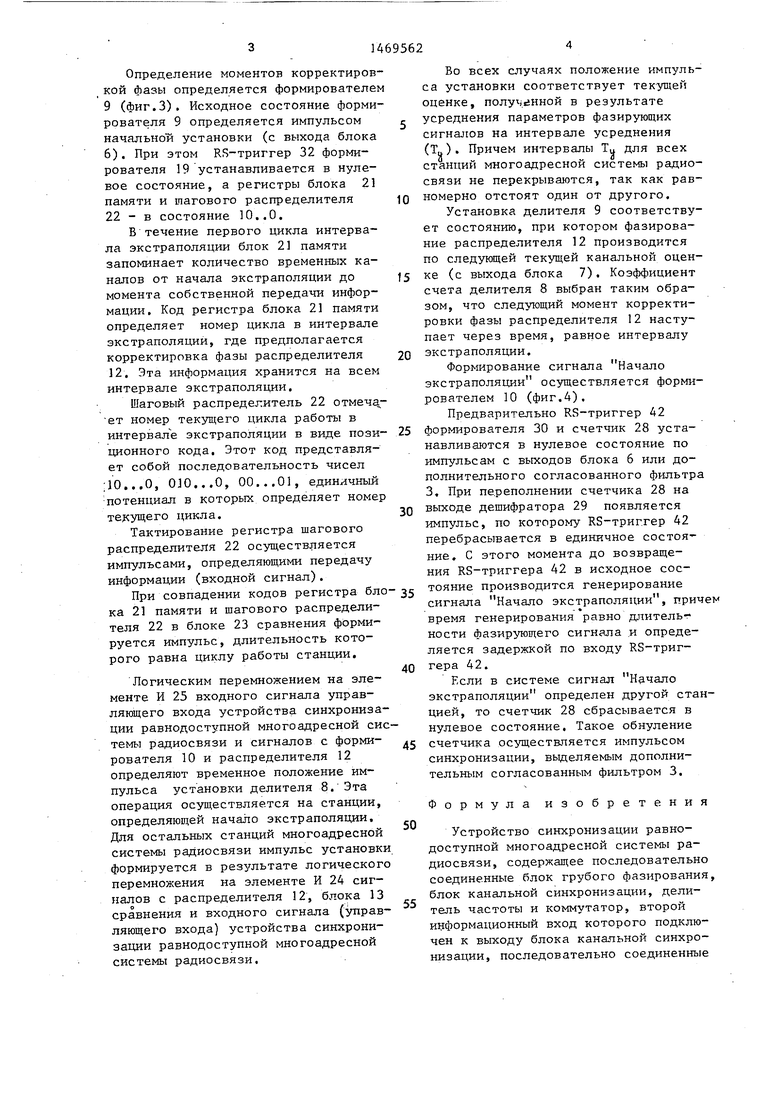

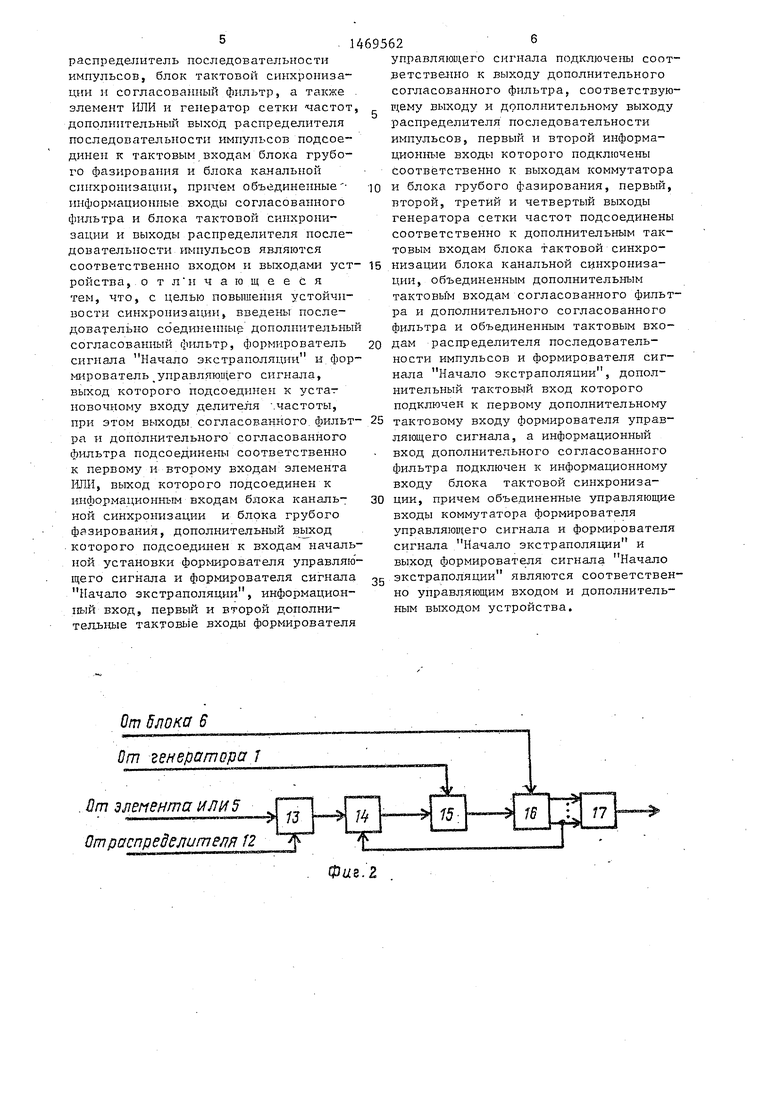

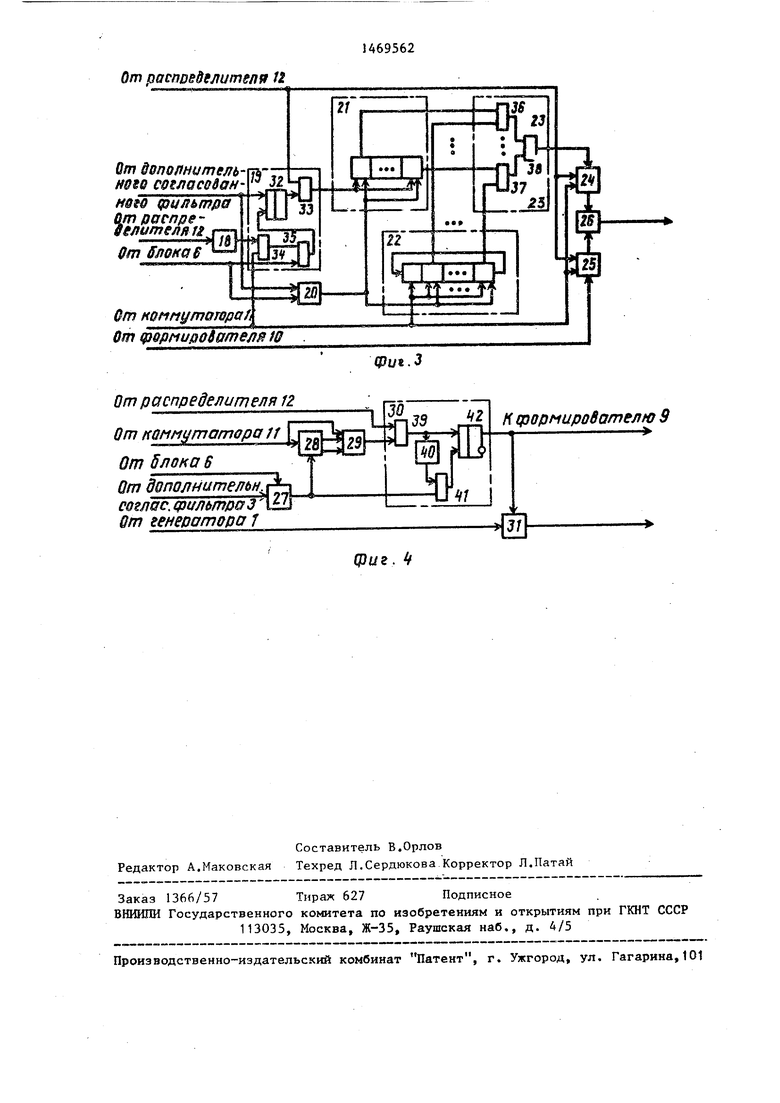

На фиг.1 представлена структурная электрическая схема устройства синхронизации равнодоступной многоадресной системы радиосвязи; на фиг.2 - структурная электрическая схема блок канальной синхрониза1 1ии; на фиг.З - то же, формирователя управляющего сигнала; на фиг,4 - то же, формиро- вателя сигнала Начало экстраполяции

Устройство синхронизации равнодоступной многоадресной систе радиосвязи содержит генератор 1 сетки частот, согласованный фильтр 2, до- полнительный согласованный фильтр 3, блок 4 тактовой синхрониза1ши, элемент ИЛИ 5, блок 6 грубого фазирования, блок 7 канальной синхронизации, делитель 8 частоты; формирователь 9 управляющего сигнала, формирователь 10 сигнала Начало экстраполяции, коммутатор 11, распределитель 12 последовательности импульсов.

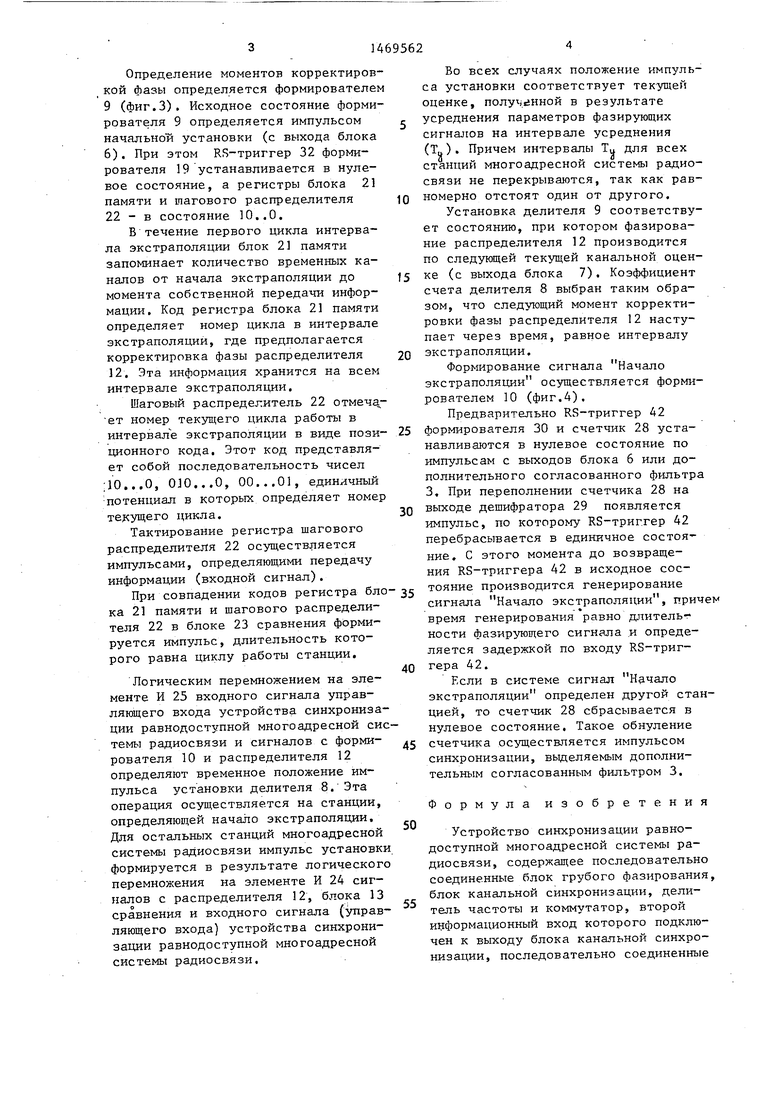

Блок 7 канальной синхронизации содержит элемент И 13, реверсивный счетчик 14, коррекционный элемент 15, делитель 16 частоты, дешифратор 17.

Формирователь 9 управляющего сигнала содержит блок 18 задержки, формирователь 19 импульсов записи, элемент ИЛИ 20, блок 21 памяти, шаговый распределитель 22, блок 23 сравнения элементы И 24, 25, элемент ИЛИ 26.

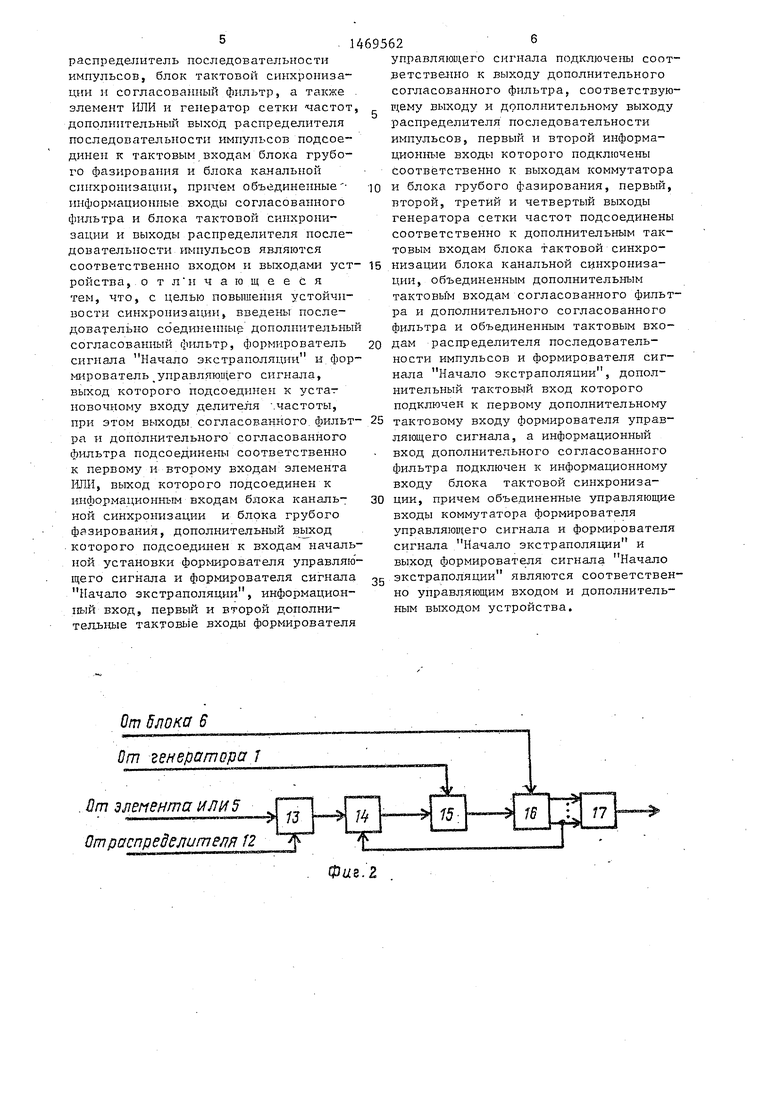

Формирователь 10 сигнала Начало экстраполяции содержит элемент ИЛИ 27, счетчик 28 импульсов, дешифратор 29, формирователь 30 сигнала управ- ления передачей, генератор 31 сигнала Начало экстраполяции.

Формирователь 19 импульсов записи содержит RS-триггер 32, элементы И 33, 34, элемент ИЛИ 35.

Блок 23 сравнения содержит эле- менты И 36, 37, элемент ИЛИ 38.

Формирователь 30 сигнала управления передачей содержит элемент И 39

блок 40 задержки, элемент ИЛИ 41, RS-триггер 42.

Устройство синхронизации равнодоступной многоадресной системы радиосвязи работает следующим образом.

По, фазирующим сигналам, поступающим из канала связи, обеспечивается формирование импульсов разметки временных каналов. При этом производится выделение импульсов сигнала Начало экстраполяции и импульсов фазирующих сигналов с помощью согласованного фильтра 2 и дополнительного согласованного фильтра 3. которые через блок 6 осуществляют первоначальное (грубое) фазирование канальной синхронизации путем установления регистра распределителя 12 и делителя 16 блока 7 в соответствую-- щее состояние (фиг, 1, 2),

Точное фазирование канальной синхронизации производится блоком 7, выполненным в виде следящей систе- . Слежение осуществляется по импульсам синхронизации, которые формируются на выходах согласованного фильтра 2 и дополнительного согласованного фильтра 3.

Всякое рассогласование опорного сигнала относительно синфазного состояния дает преобладание того или иного знака. Величина рассогласования представляется в виде кода реверсивного счетчика 14. Если опорный сигнал отстает (опережает) от импульса синхронизации, то осуществляется изменение частоты на выходе корреляционного элемента 15 путем добавления (исключения) импульсов в исходную последовательность. После деления этой последовательности в делителе 16 на выходе дешифратора 17 образуется текущая оценка канальной синхронизации. Эта оценка используется для корректировки фазы распределителя 12 через коммутатор П.

При работе станции только на прием корректировка фазы распределителя осуществляется каждой текущей оцеикой от блока 7. При работе станции на передачу и прием в разных временных каналах корректировка обеспечивается импульсами с выхода делителя 8 в моменты времени собственной передачи.

Определение моментов корректировкой фазы определяется формирователем 9 (фиг.З). Исходное состояние формирователя 9 определяется импульсом начальной установки (с выхода блока 6). При этом RS-триггер 32 формирователя 19 устанавливается в нулевое состояние, а регистры блока 21 памяти и шагового распределителя 22 - в состояние 10..0.

В течение первого цикла интервала экстраполяции блок 21 памяти запоминает количество временных каналов от начала экстраполяции до момента собственной передачи информации. Код регистра блока 21 памяти определяет номер цикла в интервале экстраполяции, где предполагается корректировка фазы распределителя 12. Эта информация хранится на всем интервале экстраполяции.

Шаговый распределитель 22 отмечд.- ет номер текущего цикла работы в интервал экстраполяции в виде позиционного кода. Этот код представляет собой последовательность чисел 10...О, OJO...O, 00...01, единичный потенциал в которых определяет номер текущего цикла.

Тактирование регистра шагового распределителя 22 осуществляется импульсами, определяющими передачу информации (входной сигнал).

При совпадении кодов регистра блока 21 памяти и шагового распределителя 22 в блоке 23 сравнения формируется импульс, длительность которого равна циклу работы станции.

Логическим перемножением на элементе И 25 входного сигнала управляющего входа устройства синхронизации равнодоступной многоадресной ситемы радиосвязи и сигналов с формирователя 10 и распределителя 12 определяют временное положение импульса установки делителя 8. Эта операция осуществляется на станции, определяющей начало экстраполяции. Для остальных станций многоадресной системы радиосвязи импульс установк формируется в результате логическог перемножения на элементе И 24 сигналов с распределителя 12, блока 13 сравнения и входного сигнала (управляющего входа) устройства синхронизации равнодоступной многоадресной системы радиосвязи.

Во всех случаях положение импульса установки соответствует текущей оценке, полупленной в результате усреднения параметров фазирующих сигналов на интервале усреднения (Тц). Причем интервалы Т для всех станций многоадресной системы радиосвязи не перекрываются, так как рав- Q номерно отстоят один от другого.

Установка делителя 9 соответствует состоянию, при котором фазирование распределителя 12 производится по следующей текзтцей канальной оцен- 5 ке (с выхода блока 7). Коэффициент счета делителя 8 выбран таким образом, что следующий момент корректировки фазы распределителя 12 наступает через время, равное интервалу 0 экстраполяции.

Формирование сигнала Начало экстраполяции осуществляется формирователем 10 (фиг.4).

Предварительно RS-триггер 42 5 формирователя 30 и счетчик 28 устанавливаются в нулевое состояние по импульсам с выходов блока 6 или дополнительного согласованного фильтра 3, При переполнении счетчика 28 на 3Q выходе дешифратора 29 появляется импульс, по которому RS-триггер 42 перебрасывается в единичное состояние, С этого момента до возвращения RS-триггера 42 в исходное сос- ,5- тояние производится генерирование

сигнала Начало экстраполяции, причем время генерирования равно длительт- ности фазирующего сигнала и определяется задержкой по входу RS-триг- 40 гера 42.

Если в системе сигнал Начало экстраполяции определен другой станцией, то счетчик 28 сбрасывается в нулевое состояние. Такое обнуление 45 счетчика осуществляется импульсом синхронизации, вьщеляемым дополнительным согласованным фильтром 3.

Формула изобретения

Устройство синхронизации равнодоступной многоадресной системы радиосвязи, содержащее последовательно соединенные блок грубого фазирования, блок канальной синхронизации, делитель частоты и коммутатор, второй информационный вход которого подключен к выходу блока канальной синхронизации, последовательно соединенные

импульсов, блок тактовой синхронизации и согласованный фнльтр, а также . элемент ГШИ и генератор сетки частот, дополнительный выход распределителя последовательности импульсов подсоединен к тактовым входам блока грубого фазирования и блока канальной синхро1П-1заиин, причем объединенные - информационные входы согласованного фнлътра и блока тактовой синхрони нации и выходы раснределителя носле- довательности импульсов являются соответственно входом и выходами устройства,, о тл и чающееся тем, что, с целью повышения устойчивости синхронизации, введены последовательно соединенные дополнительный согласованный фильтр, формирователь сигнала Начало экстраполяции и.формирователь управляющего сигнала, выход которого подсоединен к установочному входу делителя .частоты.

ветстве1п-ю к выходу дополнительного согласованного фильтра, соответствующему выходу и донолнительному выходу распределителя последовательности импульсов, первый и второй информационные входы которого подключены соответственно к выходам коммутатора

0 и блока грубого фазирования, первый, второй, третий и четвертый выходы генератора сетки частот подсоединены соответственно к дополнительным тактовым входам блока тактовой синхро5 низании блока канальной синхронизации, объединенным дополнительным тактовым входам согласованного фильтра и дополнительного согласованного фильтра и объединенным тактовым вхо0 дам раснределителя последовательности импульсов и формирователя сигнала Начало экстраполяции, дополнительный тактовый вход которого подключен к первому дополнительному

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации многоканальной системы радиосвязи | 1990 |

|

SU1739502A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1976 |

|

SU650245A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU758550A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1977 |

|

SU681566A2 |

| УСТРОЙСТВО ЦИКЛОВОЙ и КАНАЛЬНОЙ СИНХР011ИЗАЦИИ | 1970 |

|

SU259136A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU745012A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение устойчивости синхронизации. Устр-во содержит г-р 1 сетки частот, согласованные фильтры 2 и 3, блок тактовой синхронизации 4, эл-т ИЛИ 5, блок грубого фазирования 6, блок канальной синхронизации (БКС) 7, делитель 8 частоты, формирователь (Ф) 9 -7 управляющего сигнала, Ф 10 сигнала Начало экстраполяции, коммутатор 11 и распределитель 12 последовательности импульсов. Точное фазирование канальной синхронизации производится с помощью БКС 7, выполненного в виде следяЕ ей системы. Слежение производится по импульсам синхронизации, формируемым фильтрами 2 и 3. Образуемая текущая оценка канальной синхронизации используется для корректировки-фазы распределителя 12 через коммутатор 11. При работе станции только на прием корректировка фазы осуществляется каждой текуп1ей оценкой от БКС 7, При работе станции на передачу и прием в разных временных каналах корректировка обеспечивается импульсами с делителя 8 в моменты времени собственной передачи. Цель достигается введением фильтра 3 и Ф 9 и 10. Даны ил. выполнения БКС 7 и Ф 9 и 10. 4 ил. € (Л

при этом выходы, согласованного, фильт- 25 тактовому входу формирователя управра и дополнительного согласованного фильтра подсоединены соответственно к первому и второму входам элемента ГОБ, выход которого подсоединен к информационным входам блока канальной синхронизации и блока грубого фазирования, дополнительный выход которого подсоединен к входам начальной установки формирователя улравляю - щего сигнала и формирователя сигнала Начало экстраполяции, информационный вход, первый и второй дополни- телыдае TaKTOBbie входы формирователя

ляющего сигнала, а информационный вход дополнительного согласованного фильтра подключен к информационному входу блока тактовой синхронизации, причем объединенные управляющие входы коммутатора формирователя управляющего сигнала и формирователя сигнала Начало экстраполяции и выход формирователя сигнала Начало

экстраполяции являются соответственно управляющим входом и дополнительным выходом устройства.

От распокделителя J2

Вт бвпопнитель- Н09В согласованnew фипьтрв

Ст/готя/ efflumsnKilrri

Я /д

От SflOKQS

От Konnymowpa/t От ipoftfiujso OfneflK W

От распределителя 12 От KQMMumamopan

От 5л ока 6

От дололнителбн соглас, срильт оЗ От генератора 1

К срормцроваптелю 9

фуг. Ч

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-03-30—Публикация

1987-03-31—Подача