Изобретение относится к области аналоговой вычислительной техники, автоматике, телемеханике, радиоэлектронике и предназначено для в.ычисления частного от деления двух знакопеременных напряжений в 4-х квадрантах. Известное делительное устройство I выполняет операцию деления методом неявных функций с использованием операционного усилителя с аналоговым умножителем в обратной связи.. Недостатком такого устройства является невозможность выполнения операции деления в 4-х квадрантах. Наиболее близким техническим решением к предложенному является делительное устройство 21, содержащее блок умножения, первый вход которого является входом делителя устройства, компаратор, один вход которого подключен к входу делител устройства,а другой - к шине нулев потенциала, первый и второй ключи, операционный усилитель, выход кото рого подключен к второму входу блока умножения и является выходом устройства, инвертирующий вход опе рационного, усилителя через первый масштабный резистор подключен к шине нулевого потенциала и через последовательно соединенные первый ключ и второй масштабный резистор к входу делимого устройства. Недостатком этого устройства является необходимость использования в качестве умножителя только такого блока, в котором выходное напряжение имеет постоянный знак. В противном случае обратная связь разрывается и устройство перестает функционировать , В частности, в делительном устройстве 2 в .качестве умножителя используется умножитель на квадранторах, выходное напряжение которого имеет постоянный знак. Данное огра 1Ичение приводит к тому, что в схему умножителя дополнительно вводится устройство вычисления модуля, что усложняет схему всего делительного устройства. Кроме того, применение умножителя на квадранторах вносит большую погрешность при небольших напряжениях на входе делителя и уменьшает устойчивость всего делительного устройства, а также приводит к усложнению схемы, связанному с необходимостью применения устройства вычисления модуля на входе умножителя.

Целью-изобретения является повышение точности делительного устройства,

Поставленная цель достигается тем, что в известное делительное устройство введены инвертор и два ключа, причем выход компаратора подключен к входу инвертора и к управляницим входам второго и- четвертого ключей, выход инвертора подключе k управляющим входам первого и третьего ключей, информационные входы третьего и четвертого ключей объединены и через третий масштабный рези тор подключены к выходу блока умножения , информационный вход второго ключа подключен к информационному входу первого клича, выхода: второго и третьего ключей объединены и подключены к неинвертирую1Цвл}у входу опрационного усилителя и через четвертый масштабный резистор к шине нулевого потенциала, выход четвертого ключа подклйрчен к инвертирующему входу операционного усилителя.

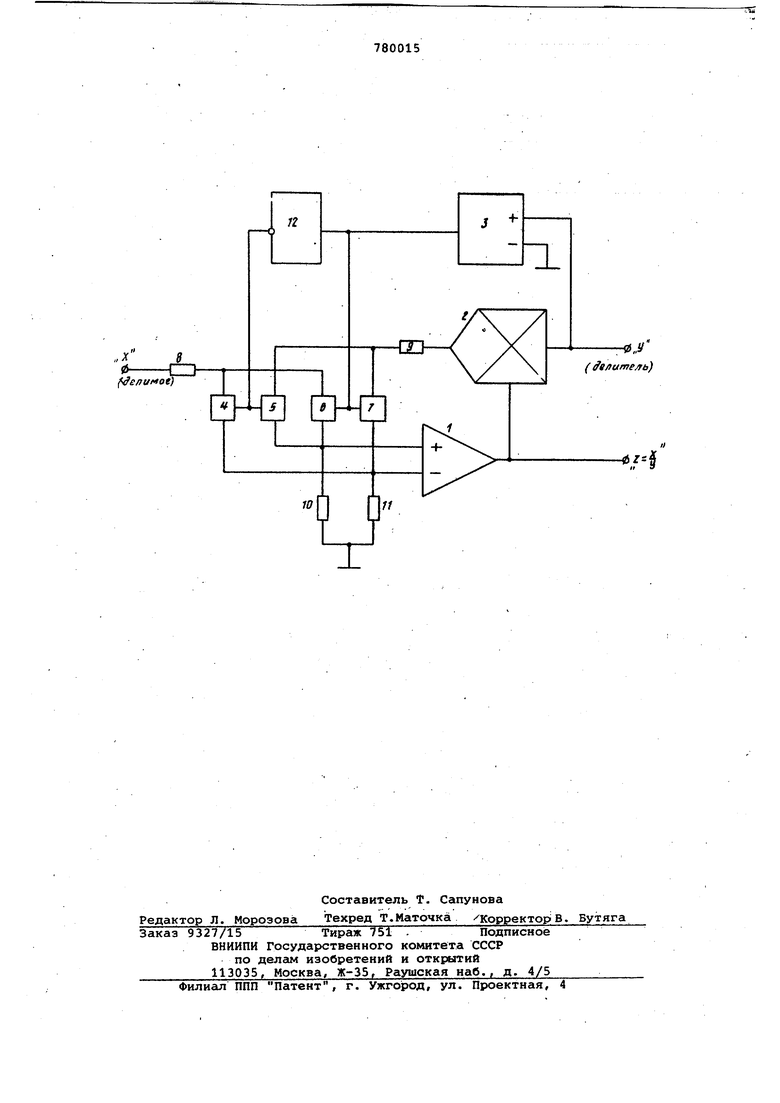

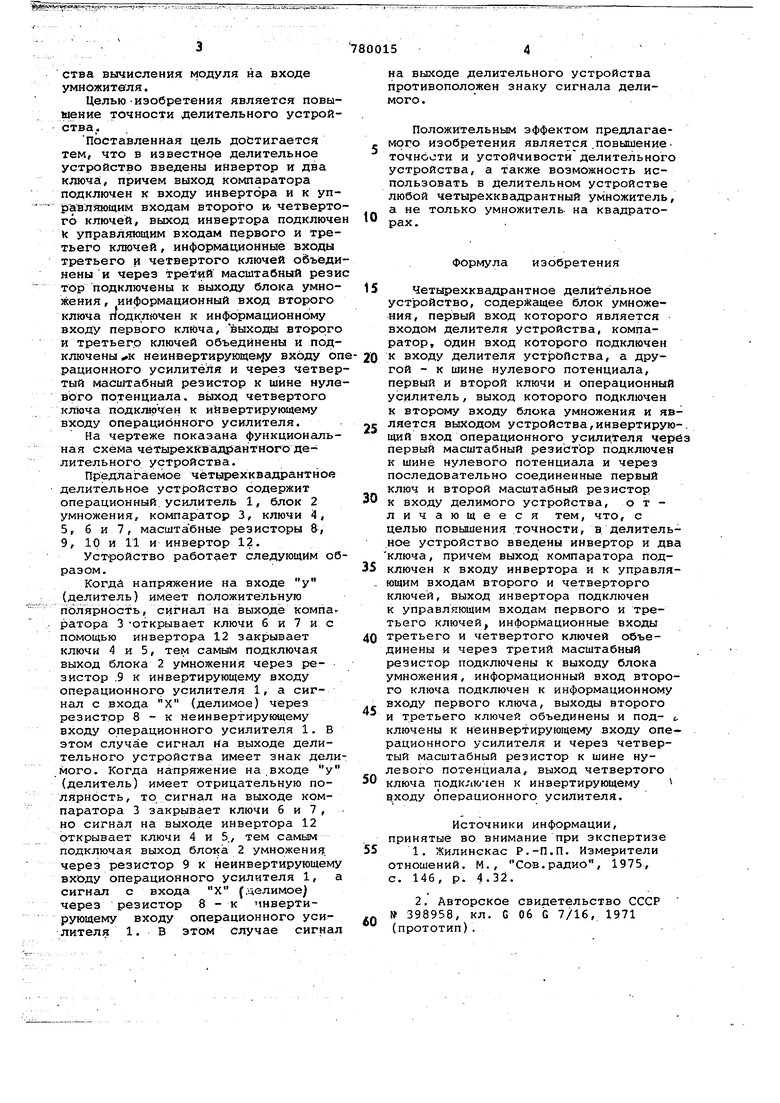

На чертеже показана функциональная схема чётырех {вадрантного делительного устройства.

Предлагаемое чётырехквадрантное делительное устройство содержит операционный усилитель 1, блок 2 умножения, компаратор 3, ключи 4, 5, 6 и 7, масштабные резисторы 8, 9, 10 и 11 и инвертор 12.

Устройство работает следующим образом.

Когда напряжение на входе у (делитель) имеет Положительную полярность, сигнал на выходе компаратора 3 -открывает ключи б и 7 и с помощью инвертора 12 закрывает ключи 4 и 5, тем самым подключая выход блока 2 умножения через резистор .9 к инвертирующему входу операционного усилителя 1, а сигнал с входа X (делимое) через резистор 8 - к неинвертирующему входу операционного усилителя 1. В этом случае сигнал на выходе делительного устройства имеет знак делимого. Когда напряжение на .входе у (делитель) имеет отрицательную полярность, то сигнал на выходе компаратора 3 закрывает ключи б и 7, но сигнал на выходе инвертора 12 открывает ключи 4 и 5., тем самым подключая выход блока 2 умножения, через резистор 9 к неинвертирующему входу операционного усилителя 1, а сигнал с входа X (делимое) через резистор 8 - к мнвертирующему входу операционного усилителя 1. В этом случае сигнал

на выходе делительного устройства противоположен знаку сигнала делимого.

Положительным эффектом предлагаемого изобретения является .повышениеточности и устойчивости делительного устройства, а также возможность использовать в делительном устройстве любой четырехквадрантный умножитель, а не только умножитель на квадраторах.

Формула изобретения

Чётырехквадрантное делительное устройство, содержащее блок умножения, первый вход которого является входом делителя устройства, компаратор, один вход которого подключен

к входу делителя устройства, а другой - к шине нулевого потенциала, первый и второй ключи и операционный усилитель, выход которого подключен к второму входу блока умножения и является выходом устройства,инвертирую-, щий вход операционного усилителя через первый масштабный резиСтЬр подключен к шине нулевого потенциала и через последовательно соединенные первый ключ и второй масштабный резистор

к входу делимого устройства, отличающееся тем, что, с целью повьнаения точности, в. делитель,ное устройство введены инвертор и два ключа, причем выход компаратора подключен к входу инвертора и к управляющим входам второго и четверторго ключей, выход инвертора подключен к управляющим входам первого и третьего ключей, информационные входы

третьего и четвертого ключей объединены и через третий масштабный резистор подключены к выходу блока умножения, информационный вход второго ключа подключен к информационному входу первого ключа, выходы второго и третьего ключей объединены и под- (, ключены к неинвертиру ощему входу операционного усилителя и через четвертый масштабный резистор к шине нулевого потенциала, выход четвертого

ключа подключен к инвертирующему цходу операционного усилителя.

Источники информации, принятые во внимание при экспертизе 1. Жилинскас Р.-П.П. Измерители отношений. М., Сов.радио, 1975, с. 146, р. 4.32.

2, Авторское свидетельство СССР 398958, кл. G Об G 7/16, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехквадрантное делительное устройство | 1984 |

|

SU1198543A2 |

| Делительное устройство | 1982 |

|

SU1070569A1 |

| Аналоговое делительное устройство | 1983 |

|

SU1153331A1 |

| Аналого-цифровое делительное устройство | 1979 |

|

SU886017A1 |

| Множительно-делительное устройство | 1986 |

|

SU1405077A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Устройство для деления аналоговых сигналов | 1990 |

|

SU1795479A1 |

| Устройство для вычисления алгебраических выражений | 1979 |

|

SU864298A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

Т

ьч

И

Ю

(г у

Авторы

Даты

1980-11-15—Публикация

1978-12-25—Подача