Цель изобретения - сокращение избыточности информации..

Поставленная цель достигается тем, что в 5стройство, содержащее коммутатор, выход которого подключен к входу аналогоцифрового преобрагователя, лервый выход которого соединен с первым входом буферного регистра, второй выход - с первым входом первого блока сравнения, выход которого .связан с цервым входом блока синхронизации, первый выход блока синхронизации- соединен с вторым входом буферного регистра, второй выход - с управляющим входом коммутатора, вторым входом первого блока сравнения и первым входом блока буферной памяти, третий выход аналого-цифрового преобразователя соединен с вторым входом блока буферной памяти, введены сумматор, второй блок сравнения и ,блок постоянной памяти, выход которого соединен с первым входом сумматора. Третий выход аналого-цифрового преобразователя соединен € вторым входом сумматора, выход которого связан с третьим входом первого блока сравнения, второй выход блока синхронизации - с третьим входом сумматора и первым входом второго блока сравнения, первый выход которого соединен с четвертым входом сумматора, второй выход - с вторым входом блока синхронизации. Выход буферного регистра подключен к второму входу, а третий выход аналого-цифрового преобразователя - к третьему входу второго блока сравнения.

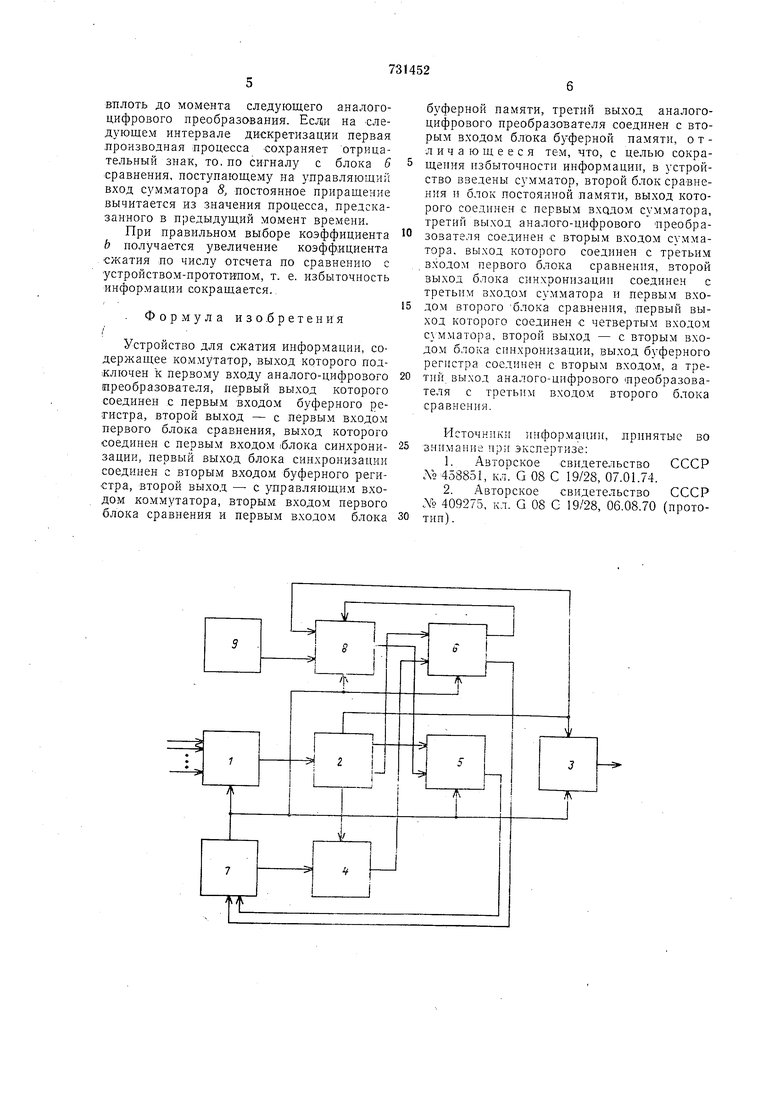

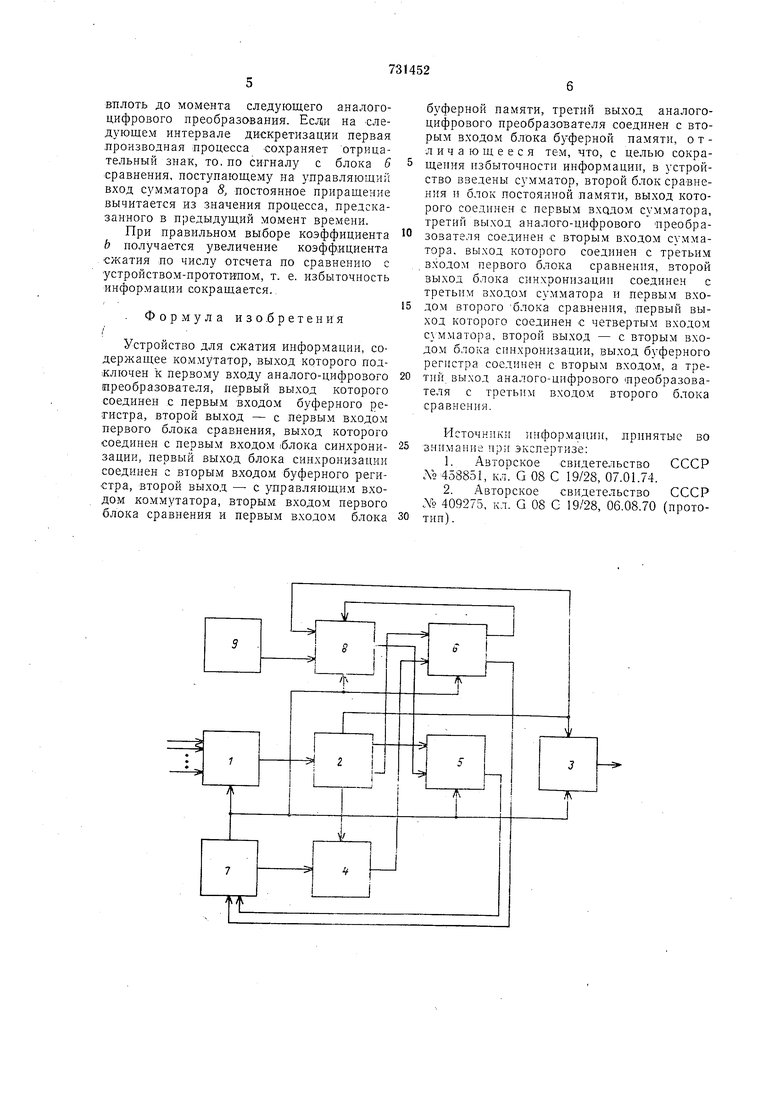

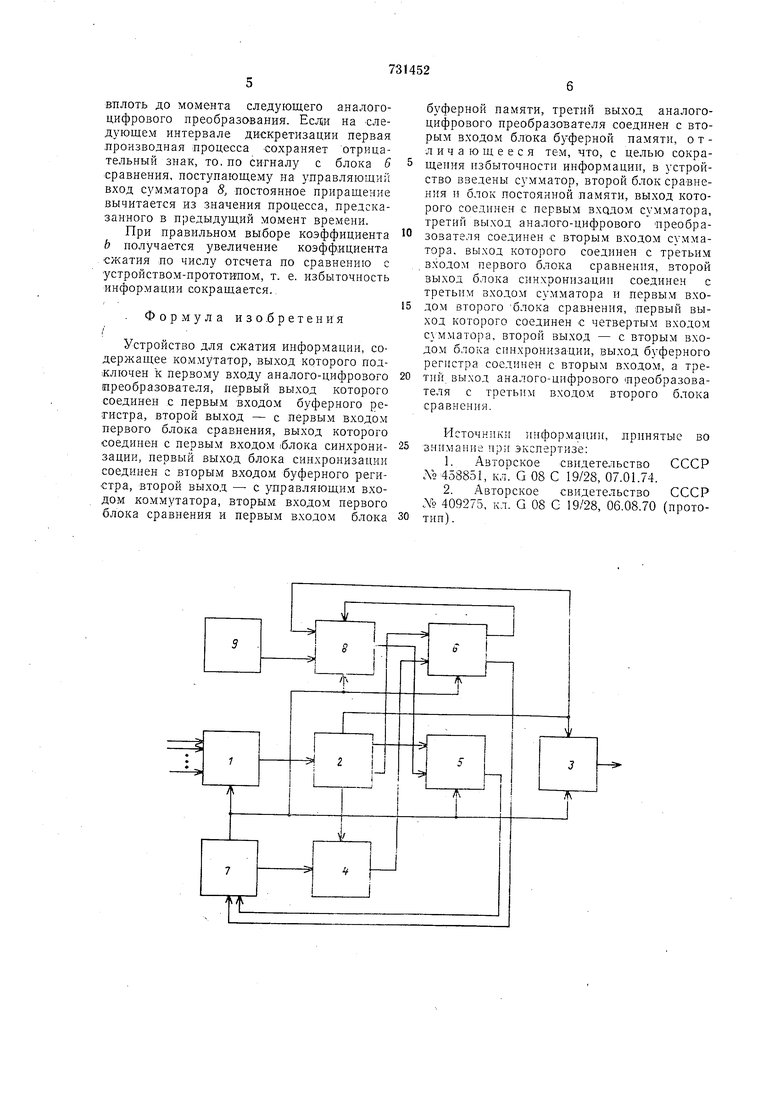

На чертеже представлена блок-схема устройства.

Она содержит коммутатор /, аналогоцифровой преобразователь 2, блок 3 буферной памяти, буферный регистр 4, блоки сравнения: первый 5 и второй 6, блок 7 синхронизации, сумматор 8, блок 9 постоянной памяти.

Устройство работает следующим образом.

. В блок 9 постоянной памяти до начала о:бработки сообщения заносят значение постоянного приращения

б Ibi .Д/,

где |6| - коэффициент, .численно равный среднему значению модуля первой производной обрабатываемого процесса; At - интервал дискретизащии обра/батыбаемаго процесса.

Коэффициент b определяется исходя из априорных сведений об исследуемом процессе. По сигналу из блока 7 синхронизации обрабатываемый сигнал через коммутатор / постулает «а вход аналого-цифрового преобразователя 2, где преобразуется в цифровую форму. Полученный код поступает на входы блока 3 буферной памяти буферного регистра 4, блока 5 сравнения сумматора 8 и блока (5 сравнения. На другой вход блока 6 сравнения из запоминающего блока поступает значение процесса, соответствующее предыдущему моменту времени. По сигналу из блока 7 синхронизации, сравнивая поступивщие на его входы значения inponecca, блок 6 сравнения определяет знак первой производной на данном интервале дискретизации.

После определения знака первой производной по сигналу из блока 7 синхронизации код с аналого-цифрового преобразователя 2 переписывается в буферный регистр 4. Знак первой производной поступает на управляющий вход сумматора 8. Предположим, что на предыдущем интервале дискретизации первая производная, обрабатываемого процесса была положительной. Тогда, если первая производная ароцесса на данном . интервале дискретизации имеет положительный знак, то по сигналу из блока 7 синхронизации содержимое блока 9 постоянной памяти прибавляется к значению процесса, предсказанному в предыдущий момент времени и хранящемуся в сумматоре 8. Таким образом, в сумматоре 8 образуется предсказанное значение процесса, соответствующее настоящему моменту времени.

Это предсказанное значение поступает на вход блока 5 сравнения и по сигналу с блока 7 синхронизации сравнивается с истинным значением процесса .в настоящий момент времени. Когда эти значения равны или отличаются на величину, меньшую дЬпустимой абсолютной потрещности, то на выходе блока 5 сравнения вырабатывается сигнал «О и он через блок оинхронизацин не разрещает блоку 3 буферной памяти принимать данное значение процесса. Есля же сравниваемые значения отличаются на величину, больщую допустимой абсолютной погрещности, то на выходе блока 5 сравнения вырабатывается сигнал «1, который через блок 7 синхронизации разрещает блоку 3 буферной памяти запомнить значение процесса в данный момент времени. По этому же сигналу рассматриваемое значение процесса с выхода аналого-цифрового преобразователя 2 переписывается в сумматор 8 и дальнейщее предсказапие значений процесса будет происходить относительно этого значения.

Если же первая производная процесса на данном интервале дискретизации имеет отрицательный знак, то блок 6 сравнения вырабатывает сигнал об изменении знака первой производной. Этот сигнал через блок 7 синхронизации разрещает блоку 3 буферной памяти запомнить рассматриваемое значение процесса. По этому же сигналу данное значение процесса переписывается ИЗ аналого-цифров&го преобразователя 2 в сумматор 8. После этого блок 7 синхронизации не выдает разрешающих сигналов на выполнение последующих операций

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия информации | 1978 |

|

SU780019A1 |

| Устройство для сжатия информации | 1979 |

|

SU830484A1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Устройство для сокращения избыточности информации | 1981 |

|

SU1005148A1 |

| Нерекурсивный цифровой фильтр | 1984 |

|

SU1223346A1 |

| Функциональный преобразователь | 1978 |

|

SU805337A1 |

| Многоканальная система для анализаэКСТРЕМуМОВ | 1977 |

|

SU842826A1 |

| Устройство для кодирования аналоговых сигналов | 1985 |

|

SU1316091A1 |

| Устройство для разделения направлений передачи и приема | 1989 |

|

SU1734220A1 |

| СПОСОБ ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099721C1 |

Авторы

Даты

1980-04-30—Публикация

1978-04-10—Подача