единен с выходом элемеита 2И-п ИЛИ, при этом первый вход первого блока сравнения соединен с первыми входами п-1 блока сравнения, а вторые входы п блоков сравнения соединены СП шинами входных сигналов,при этом выходы п блоков сравнення соединены соответственно со входами регистра, выходы которого соединены соответственно с первыми входами элемента ИЛИ, вторые входы которого соединены соответственно с выходами блока иэбирания, второй вход которого соединен с шиной адресаканала.

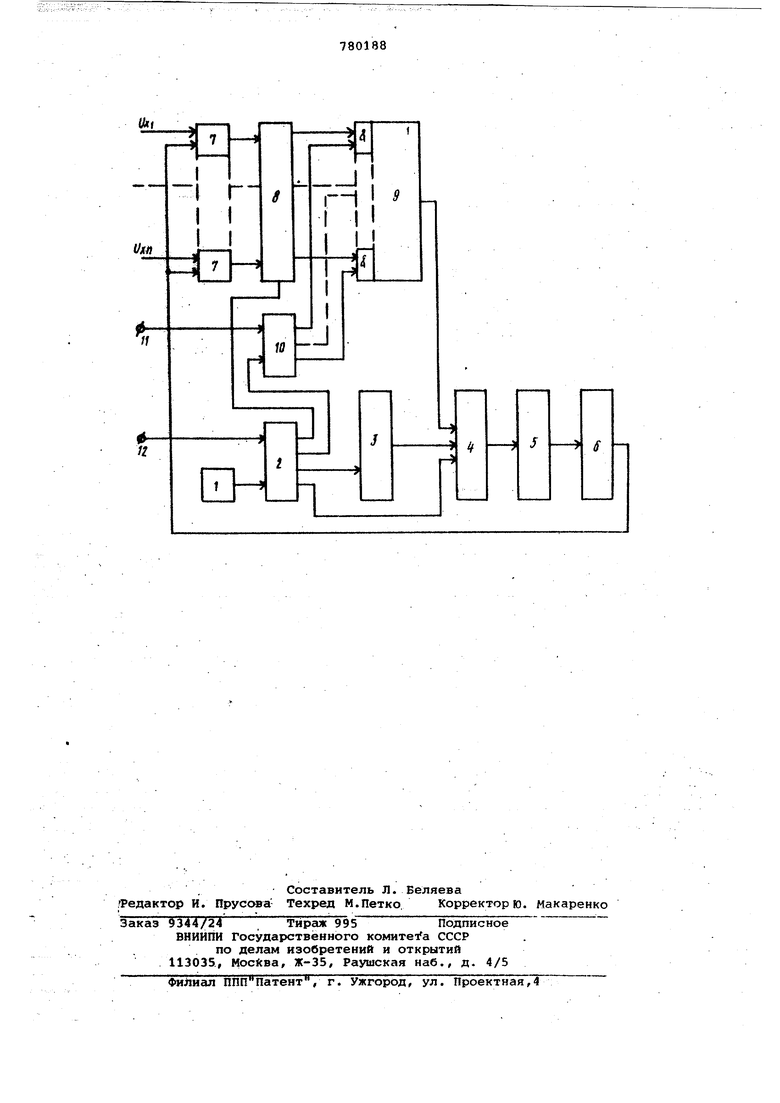

На чертеже представлена структурная схема многоканального аналогоцифрового преобразователя.

Преобразователь содержит тактовый генератор 1 импульсов, блок 2 режимов, распределитель 3, блок 4 управления, регистр 5 преобразования, циф1РОаналоговый преобразователь 6, блоки 7 сравнения, регистр 8/элемент 2И-П ИЛИ 9, блок 10 избирания, шину 11 адреса канала, ыину 12 управляющего входа блока режимов.

Работа многоканального аналогоцифрового преобразователя осуществляется после предварительного занесения в блдк режимов кода команды, которая может соответствовать одному йэ следующих основных режимов работк преобразователя;

а)преобразование по заданному адресу;

б)определение максимума;

в)определение минимума-,г)определение потенциалов заданного диапазона.

В режиме п С5еобразования по заданному адресу на входной регистр блока избира1йия заносится код адреса изби e sftiKAfiSina, по которому отпира %тся элемент совпадения 2И - п ИЛИ, соответствующий этому каналу.

В каждом такте по сигналам с блока режимов производится предварительная установка в б регистра 8. в результате сравнения аналоговых сигналом 0 с компёнсируияц М напряжением 0 сигналами с блокоа сравнения переключ-аются в 1 триггеры регистра 8 тех каналов , для которых вЫпол-; няётся условие U(j.- Элемент 2И-п I ИЛИ пропускает на вход бло.ка 4 управления сигналы с выхода триггера регистра 9 избранного канала. По этим сигналам осу11ествляется поразрядное уравновешивание измеряемого сигнала компенйИругацим напряжением, в результате чего в регистре 5 преобразователя образуется код напряжения, избранного по заданному адресу . канала.

В режиме определения максимума по сигналу с блока реу симов блок избираНия отпирает все п элементы 2И - п ИЛИ. По сигналам с блока режимов в ксОкдом такте перед, сравнением п зоиз-г

водится предварительная установка в О регистра 8. При соотношении K. результате сравнения,вс триггеры регистра 8 остаются в нулевом состоянии, на выходе элемента 2И-П ИЛИ остается сигнал О и блок управления осуществляет уменьшение напряжения U«. При соотношении и, ,.триггеры регистра 8 каналов , для KOTOftax выполняется это неравенство, переключаются в 1, на выходе элемента 2И-п ИЛИ, появляется сигнал 1 и блок управления по сигнё лу осуществляет увеличение нап{эяжёния .

Таким образом, в процессе преобразования осуществляется уравновешивание компенсирующим напряжением максимального напряжения, но поскольку веса разрядов уменьшаются по двоичному закону, то компенсирующее напряжение будет приближаться к максимальному значению и в регистре преобразователя образуется код максимального напряжения.

В режиме определения минимума по сигналам с блока 2 рехшмов в блоке 4 управления используются инверсные значения сигналов с выхода элемента 2И-П ИЛИ 9, блок избирания отпирает все элементы 2И-п ИЛИ, при этом все триггеры регистра 8 устанавливаются в 1 в каждом такте перед сравнением.

ЕСЛИ в текущем такте поразрядного уравновешивания имеет место неравенство UXAAMH и, то все триггеры регистра 8 сигналами 1 с блоков сравнения, поступающими на их счетные входы, переключаются в О. На выходе элемента 2И-п ИЛИ появляется О и блок управления по инверсным значениям этого сигнала производит потактНое увеличение компенсирующег напряжения UK ДО тех пор, пока оно не превысит значения U,/v,,f .

При U|. , хотя бы в одном канале, на выходе соответствующего блока сравнения появится сигнал О в результате чего на соответствующих триггерах регистра останется 1 и,следовательно,на выходе 2И-п ИЛИ будет тоже сигнал 1, по которому блок управления будет осуществлять в данном режиме потактное уменьшение компенсирующего напряжения Un до тех пор, пока оно не станет меньше напряжения Uj;,,,, но поскольку веса разрядов уменьшаются п двоичному закону, то компенсирующее напряжение будет приближаться к минимальному значению.

Таким образом, в процессе преобразования осуществляется уравновешивание минимального напряжения, а в регистре 5 преобразователя образуется код.минимального напряжения.

В режиме определения потенциалов в заданном диапазоне 14-U блокиру ётся работа блока управления, блок избирания отпирает все элементы 2И-П ИЛИ, и все триггеры регистра 8 устанавливаются в О. В регистр преобразования заносит ся код напряжения U, аналоговьй эквивсшент этого кода сравнивается бло ками сравнения с сигналами каналов. В результате сравнения в 1 устанавливаются те триггеры регистра 8, для каналов которых выполняется условие DX и. Затем в регистр преобразования заносится код напряжения U и напряжение, соответствуючдее этому коду, сравнивается блоками сравнения с сиг налами каналов. В результате сравнения на входы регистра 8 поступают с блоков сравнения сигналы 1 тех ка налов ,для которых выполняется условие 1/ и. Этими сигналами,поступающими на счетные входы триггеров, переключаются в 1 триггеры регистра 8, находившиеся в О, и переключаются в О триггеры регистра 8, ранее установленные в 1. Таким образом, в 1 остаются триггеры тех каналов, напряжение которых ограничено уровнями и и Uj. Затем устройство переключается в режим съема информации и поочередным считывание.м с триггеров регистра 8 производится съем полученной информации, при котором с регистра 8 блокируется работа блока управления и отпираются элементы.2И-П ИЛИ того канала, адрес которого занесен на входной регистр блока избирания. Таким образом, при поочередном опросе каналов на выходе элемента 2И-П ИЛИ появляются выходные сигналы триггеров регистра 8 тех каналов,откуда производится их считывание. Таким образом, использование предлагаемого многоканального аналого-цифрового преобразователя в аналого-цифровых вычислительных комплексах позволит в процессе прнэ.образования информации осуществлять первичную обработку этой информации,В результате этого существенно упрощаются и ускоряются операции определения экстремальных значений Функции, нахождения адресов, экстремальных значений функции и построения эквипотенциальных линии, что ведет к увеличению производительности указанных комплексов. Формула изобретения Многоканальный аналого-цифровой преобразователь, содержащий тактовый генератор импульсов, блок избирания, распределитель, выход которого соединен с первым входом блока управления, выход которого через регистр преобразования соединен со входом цифроаналогового преобразователя, выход которого соединен с первым входом первого блока сравнения,о т л и ч а ю щ и и.с я тем, что, с целью расширения функциональных возможностей преобразователя, введены блок режимов, элемент 2И-п ИЛИ,регистр, п-1 блоков сравнения, причем выход тактового генератора соединен с первым входом блока режимов,второй вход которого соединен с тиной управляющего входа блока режимоп,порвый выход соединен с управлякяцим входом регистра,второй выход - с первым входом блока избирания, третий выход - со входом распределителя, а четвертый выход - со вторым входом блока управления, третий вход которого соединен с выходом элемента 2И-п ИЛИ, при этом первый вход первого блока сравнения соединен с первыми входами п-1 блока сравнения, а вторые входы п блоков сравнения соединены с п тинами входных сигналов, при этом пыходы п блоков сравнения соединены соответственно со входами регистра, выходы которого соединены соответственно с первыми входами элемента 2И-П ИЛИ, вторые входы которого соединены соответственно с выходами блока избирания, второй вход которого соединен с шиной адреса канала. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 330539, кл. И 03 К 13/17, 21.07.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля систем преобразователей информации | 1980 |

|

SU978152A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1113816A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Преобразователь напряжение-код сКОНТРОлЕМ | 1979 |

|

SU822342A1 |

| Устройство для сопряжения интерфейса ввода-вывода с регистратором | 1982 |

|

SU1070539A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

Авторы

Даты

1980-11-15—Публикация

1978-06-27—Подача