1

Изобретение относится к вычислительной технике и предназначено для сопряжения ЦВМ.

Известно устройство сопряжения, содержащее буферное ЗУ, регистра, грутпты вентилей ввода информации, распределители ввода информации, регистр меток, сумматор, схемы сравнения, регистры констант и схему управления 1 .

Недостатком этого устройства является сложность.

Наиболее близким техническим решением к предлагаемому является устройство сопряжения, содержащее блок управления вводом, соединенный со входами первого и второго регистров, первую щину, соединенную с выходами двух формирователей импульсов, дешифратором адреса, первым и вторым блоками приемников и блоком управления прерыванием, выход первого регистра соединен со входом первого формирователя импульсов, выход первого блока приемников соединен со входом второго регистра, первый выход второго регистра соединен со входом первого формирователя импульсов и первым входом блока управления прерыванием, второй выход - со входом первого формирователя импульсов и первым входом первого элемента ИЛИ, третий выход со входом первого формирователя импульсов и вторым входом первого элемента ИЛИ, блок управления выводом, соединенный с третьим и четвертым регистрами, первый вход третьего регистра соединен с выходом второго блока приемников и входом четвертого регистра, первый выход которого соединен со входом блока уттравления прерыванием и первым

to входом второго формирователя импульсов, второй выход - со вторым входом второго формирователя импульсов и первым входом второго элемента ИЛИ, третий выход - с третьим входом второго формирователя импуль15сов и вторым входом второго элемента ИЛИ, соответствующие выходы дешифратора соединены со входами первого блока приемников, первого и второго регистров, первого и второ;о формирователей импульсов 2.

20

Недостатком этого устройства является сложность.

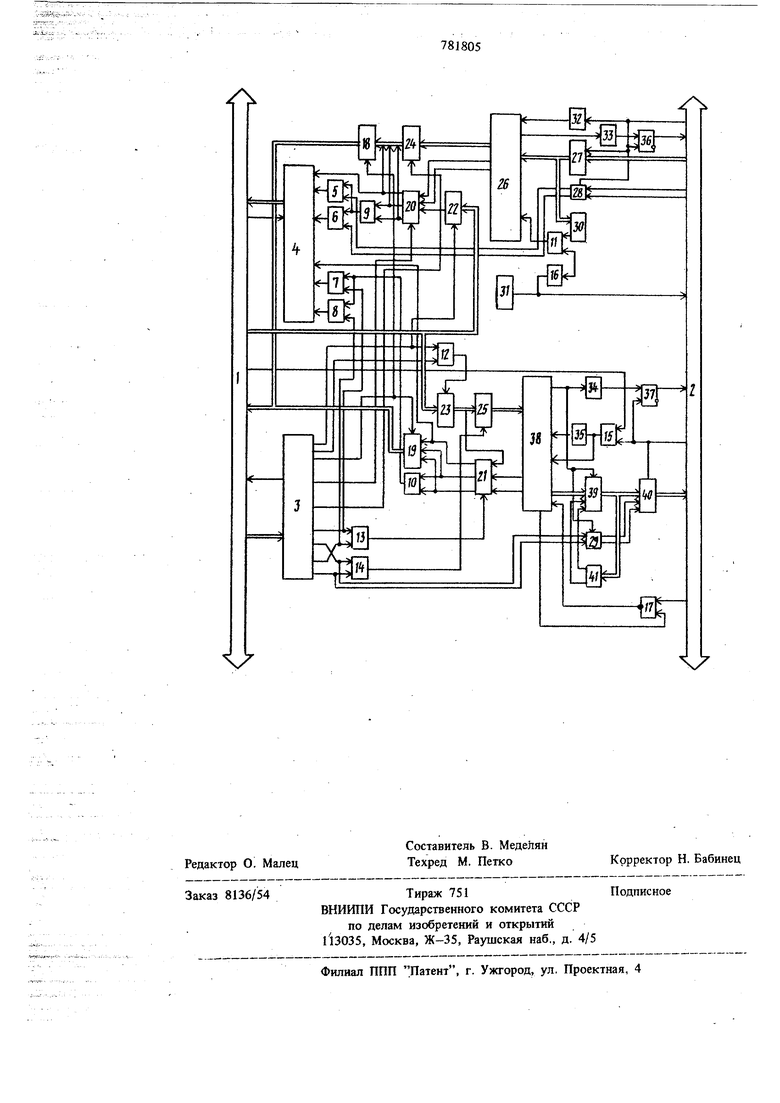

Цель изобретения - упрощение устройства. 37 Поставленная цель достигается тем, что устройство содержит четыре элемента И, два триггера, три элемента задержки, два блока сравнения, элемент И-НЕ, блок усилителей, пять элементов ИЛИ, одновибратор, инвертор, блок формирования сигнала готовности, вторую шину, пятый, шестой, седьмой и восьмой регистры, входы первого и второго элементов И соединены с выходами первого элемента ИЛИ и пятого регистра, выходы - с блоком управления прерыванием, соед1шенного с выходами третьего и четвертого элементов И,, первые вхо ды которых соединены с выходом второго эле мента ИЛИ, вторые входы - с соответствующи ми выходами дешифратора адреса и входами третьего элемента ИЛИ, выход которого соединен со входом четвертого регистра, выход блока формирования сигнала готовности соединен со второй шиной и входом инвертора, выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом первого блока сравнения, выход - с блоком управления вводом, соединенным с выходом шестого регистра, входом первого блока сравнения, выходом одновибратора и входом первого элемента задержки, вы ход которого соедршен с первым входом первого триггера, второй вход которого соединен со второй шиной и входом одновибратора, выход - со второй шиной, соединенной со входа ми пятого и шестого регистров, выходом второго триггера, входом и выходами блока усилителей, первым входом пятого элемента ИЛИ первым входом второго триггера и первым входом элемента И-НЕ, второй вход которого соединен с блоком управления выводом, выход - со входом блока управления выводом, выходы дешифратора соединены со входами шестого элемента ИЛИ,-выход которого соединен со входом второго блока приемников, вход третьего регистра соединен с выходом седьмого элемента ИЛИ, входы которого соеди нены с соответствзтошими выходами дешифратора адреса и входами седьмого регистра, другой вход которого соединен с блоком управления выводом, входами второго элемента задержки и восьмого регистра, выход которого соединен с одними входами блока усилителей и входом второго блока сравнения, выход которого соединен со входом восьмого, регистра, выход седьмого регистра соединен с другими входами блока усилителей, выход второго элемента задержки соединен со вторым входом второго триггера, второй вход пятого элемента ИЛИ соединен с первой шиной, выход - с блоком управления выводом и вхо, дом третьего элемента задержки, выход которого соединен с блоком управления выводом. На чертеже представлена блок-схема устройства. Устройство содержит первую шину 1 (обшая шина), вторую шину 2 (разделенная шина), дешифратор 3 адреса, блок 4 управления прерыванием, первый элемент И 5, второй элемент И 6, третий элемент И 7, четвертый элемент И 8, первый элемент ИЛИ 9, второй элемент ИЛИ 10, четвертый элемент ИЛИ 11, шестой элемент ИЛИ 12, третий элемент ИЛИ 13, седьмой элемент ИЛИ 14, пятый элемент ИЛИ 15, инвертор 16, элемент И-НЕ 17, первый формирователь 18 импульсов, второй формирователь 19 импульсов, второй регистр 20, четвертый регистр 21, первый блок 22 приемников, второй блок 23 приемников, первый регистр 24, третий регистр 25, блок 26 управления вводом, шестой регистр 27, пятый регистр 28, седьмой регистр 29, первый блок 30 сравнения, блок 31 формирования сигнала готовности, одновибратор 32, первый элемент 33 задержки, второй элемент 34 задержки, 1 третий элемент 35 задержки, первый триггер 36, второй триггер 37, блок 38 управления выходом, восьмой регистр 39, блок 40 усилителей, второй блок 41 сравнения. Устройство работает следующим образом. Информация, выдаваемая ЭВМ, присоединенной ко второй шине 2, сопровождается сигналами идентификации. Предусмотрело два таких сигнала. При приеме этой информации ЭВМ, присоединенная к первой шине 1 в зависимости от принятого сигнала идентификации, воспринимает данные как поступившие от одного из двух внешних устройств ввода. Информация, выдаваемая ЭВМ, присоединенной к первой шине 1, также в зависимости от ее характера посылается к абонентам, имеющим разные адреса. В зависимости от номера абонента устройство сопряжения вырабатывает сигналы идентификации, сопровождающие информацию, следующую от первой шины I к ЭВМ, соединенной со второй шиной 2. В устройстве предусмотрено выработка двух таких сигналов идентификации и поэтому имеется два номера внешних устройств вывода. Передача информации от второй шины 2 через устройство связи к первой шине 1 начинается только в том случае, когда на выходе блока 31 формирования сигнала готовности имеется сигнал готовности, возникающий при включешш устройства связи и аппаратуры, подключенной к первой шине 1, после выработки сигнала Подготовка. При наличии сигнала на выходе блока 31 формирования сигнала готовности ЭВМ, подключенная ко второй шине 2 посылает слово передаваемой информации на вход шестого регистра 27 в сопровождении сигнала второй выборки и одного из сигналов идентификации. Сигнал выборки разрешает запом1шание слова информации в шестом регистре 27 и сигнала идентификации в пятом регистре 28. Кроме того, он устанавливает первый триггер 36 в нулевое состояние снимая сигнал второго требования, поступающи на вход второй шины, и запускает одновибратор 32, который выдает импульс, поступающий на вход блока 26 управления вводом. Одновременно в первом блоке 30 сравнения происходит проверка поступившего слова информации на нечетность. При обнаружении ошибки первый блок 30 сравнения выдает через четвертый элемент ИЛИ 11 сигнал на вход блока 26 управления вводом и в 15 разряд второго регистра 20 заносится единица, означающая наличие ошибки в поступившем слове информации. В этом случае ЭВМ, соединенная с первой шиной 1, во время опроса второго регистра 20, получает состояние Ошибка. То же самое происходит в случае, если равен нулю сигнал на выходе блока 31 формирования сигнала готовности. Сигнал с выхода последнего поступает через инвертор 16 и четвертый элемент ИЛИ 11 на вход блока 26 управления вводом. Если ошибка не обнаруже на, то блок 26 управления вводом выдает сиг нал на соответствующий выход. Во время действия этого сигнала слово информации переписывается на шестого регистра 27 в первый регистр 24, а сигнал соответствующего выхода, пройдя через первый элемент, 33 задержки вводит первый триггер 36 в единичное состояние. При этом на входе второй шины 2 выдается сигнал второго требования. Получив этот сигнал, ЭВМ второй шины 2 выдает следу ющее слово информации на шестой регистр 27. Одновременно в 7-й разряд второго регистра 20 заносится единица, что означает состояние Выполнено. В это время ЭВМ, присоедршенная к первой шине 1, отрабатывает программу, обеспечивающую прием информаци от ЭВМ, соединенной со второй шиной 1. Для разрешения запроса прерывания эта ЭВМ посылает через первую шину и через первый блок 22 приемников единицу в шестой разряд второго регистра 20. Для этого первая шина 1 выдает в дешифратор 3 адреса код адреса второго регистра 20 в сопровождении . сочетания сигналов управления, означающего Запись младшего байта. Разрешающие сигналы соответствующих выходов дешифратора 3 осуществляют запись пришедшей с первой шины 1 единицы через первый бдок приемников 22 во второй регистр 20. Далее ЭВМ первой шины 1 считывает содержание вышеука занного регистра. Для этого по первой шине 1 в дешифратор адреса 3 выдается сочетание сигналов управления, означающее Чтение, и КОД адреса второго регистра 20. На соответствующих выходах дешифратора адреса 3 появляются разрешающие сигналы. Через первый формирователь 18 импульсов на первую шину 1 в ее ЭВМ поступает содержание второго регистра 20. Блок управления прерыванием 4 выставляется запрос прерывания и получает разрешение на прерывание в соответствии с принятым порядком работы первой шины 1. Однако вьщача адресов векторов прерывания из блока 4 управления прерыванием на первую шину 1 зависит от того, какой идентификатор хранится в пятом регистре 28. В одном случае возникает сигнал на выходе первого элемента И 5, и блок 4 злтравления прерыванием вьщает один код адреса вектора на первую шину 1. В другом - возникает сигнал на выходе второго элемента И 6, и первая шина 1 получает другой код адреса вектора прерьтания. Управление вьщачей осушествляет второй регистр 20 через первый элемент ИЛИ 9. Для считывания поступивших данных ЭВМ посылает по первой шине 1 на вход дешифратора адреса 3 сочетание сигналов управления, обозначаюшее Чтение и адрес первого регистра 24. При этом на соответствующих выходах дешифратора 3 адреса возникают разрешающие сигналы и из первого регистра 24 через первый формирователь 18 импульсов поступают на первую шину 1 и далее в ЭВМ. При поступлении следующего слова информации в шестой регистр 27 процесс повторяется. При передаче информации от ЭВМ, соединенной с первой шиной 1, к ЭВМ, соединенной со второй щиной 2, необходимо ее снабжать соответствующим признаком идентификации и при прерывании выбрать в ЭВМ, соединенной с первой шиной 1, одну из двух подпрограмм. Для занесения шестого разряда, разрешающего прерывание, в четвертый регистр 21, ЭВМ, соединенная с первой шиной 1, посылает на вход дешифратора 3 адреса сочетание сигналов управления, обозначающее Запись млаДшего байта, и один из адресов четвертого регистра 21. Этот регистр имеет два адреса. Один из них соответствует одному из двух возможных ввдов информации (данные и команды), а другой - второму виду. В за- висимости от поступившего адреса дешифратор 3 адреса выдает соответствующий разрешающий сигнал, который через третий элемент ИЛИ 13 поступает на управляющий вход четвертого регистра 21. Сигнал Чтение младшего байта проходит через шестой элемент ИЛИ 12 на управляющий вход второго блока 23 приемников. С первой шины 1 через второй блок 23 приемНИКОВ происходит занесение единицы в шестой разряд четвертого регистра 21. Пятнадцатый разряд этого регистра обозначает ошибку. Этот разряд равен единице, если блок 38 управления выводом выдает сигнал, разрешающий выдачу данных, а от второй шины 2 через элемент 17 не йоступает сигнал Готовность ЭВМ. Седьмой разряд этого регистра означает Готовность. Единица в этот разряд заносится при передаче первого слова информа ции сигналом Подготовка, передаваемым через пятый элемент ИЛИ 15, гретий элемент 35 задержки и через блок 38 управления выводом на вход четвертого регистра 21, а при передаче всех последующих слов информации сигналом первой выборки, который поступает от ЭВМ, второй шины 2 на вход пятого элемен та ИЛИ 15 и далее по вышеописанным связям в четвертый регистр 21. При наличии ед1шиц в шестом разряде и в седьмом или в пятнадштом разрядах четвертого регистра 21, блоки отравления прерыванием выставляет на первую шину сигнал запроса прерывания. После поступления разрешения прерывания последний выдает код адреса вектора прерыватш на первую шину 1. При этом з зависимости от вира намеченной к передаче информации, посгупающей с четвертого регистра через второй элемент ИЛИ 10 и через второй формирователь 19 импульсов, в соответствии с сигналом с выхода дешифратора 3 адреса третий элемент И 7 или четвертый элемент И 8 выдает сигнал, определяюпдай один из двух выдаваемых адресов вектора прерывания. Слово информации поступает по первой шине 1. При этом на вход дешифратора 3 адреса поступает сочетание сигналов управления Запись слова и адрес третьего регистра 25, Этот регистр имеет два адреса, соответствующих двум возможным видам передаваемой информации. При одном адресе дешифратор 3 адреса выдает сигнал на вход седьмого элемента ИЛИ 1 и седьмой регистр 29 заносится один идентификатор. При другом адресе дешифратор 3 адреса вьщает соответств5аощий сигнал ив седьмой регистр 29 заносится другой идентификатор. В обоих случаях через седьмой элемент ИЛИ 14 на управляющий вход третьего регистра 25 поступает разрешающий сигнал и происходит запись слова информации в этот регистр. По соответствующему сигналу с этого регистра начинается работа блока управления 38 выводом, второй триггер 37 устанавпивается в единичное положение и на вторую итину 2 выдается сигнал первого требования. ЭВМ второй шины 2 выдает сигнал первой вы борки, который, поступая на нулевой вход второго триггера 37 сбрасывает сигнал первс го требования, trocTjiraer на управляющий вход блока 40 усш итйлей, благодаря чему слово информация поступает в ЭВМ второй шины 2 и через пятый элемент ИЛИ 15 поступает в блок 38 управлен{1я выходом, вызывая установку седьмого разряда в четвертом регистре 21, сигнализирующего о готовности к передаче следующего слова информации от первой шины 1 ко второй шине 2. Предложенное уст1:)ойство упрощается за счет искл очения избыточных сложных узлов: регистров команд н состояний, регистров данных, блоков приемников, формирований и схем управления внешними устройствами. Формула изобретения Устройство сопряжения, содержащее блок управления вводом, соединенный со входами первого и второго регистров, первую шину, соединенную с выходами двух формирователей импульсов, дешифратором адреса, первым и вторым блоками приемников и блоком управления прерыванием, выход первого регистра соединен со входом первого формирователя импульсов, выход первого блока приемников соединен со входом второго регистра, первый выход второго регистра соединен со входом первого формирователя импульсов и первым входом блока управления прерыванием, второй выход - со входом первого формирователя импульсов и первым входом первого элемента ИЛИ, третий выход - со входом первого формирователя импульсов и вторым входом первого элемента ИЛИ, блок управления выводом, соед}шенныи с третьим и четвертым рег страми, первый вход третьего регистра соединен с выходом второго блока приемников и- входом четвертого регистра, первый выход которого соединен со входом блока управдения прерыванием и первым входом второго формирователя импульсов, второй выход - со вторым входом второго формирователя импульсов и первым входом второго элемента ИЛИ, третий выход - с третьим входом второго формирователя импульсов и вторым входом второго элемента ИЛИ, соответсгаующие выходы дешифратора соединены со входами первого блока приемников, первого н второго регистров, первого и второго формирователей импульсов, отличающееся тем, что, с целью упрощения устройства, оно содержит четыре элемента И, два триггера, три элемента задержки, два блока сравнения, элемент И-НЕ, блок усилителей, пять элементов ИЛИ, одновибратор, инвертор, блок формирования сигнала готовности, вторут щину, пятый, шестой, седьмой и восьмой регистры, входы первого и второго элементов И соединены с выходами первого элемента ИЛИ и пятого регистра, выходы - с блоком управ ления прерыванием, соединенного с выходами третьего и четвертого элементов И, первые входы которых соединены с выходом второго элемента ИЛИ, вторые входы - с соответству ющими выходами дешифратора адреса и входами третьего элемента ИЛИ, выход которого соединен со входом четвертого регистра, выход блока формирования сигнала готовности соединен со второй шиной и входом инвертора, выход которого соединен с первым вхо дом четвертого элемента ИЛИ, второй вход которого соединен с выходом пердого блока сравнения, выход - с блоком управления вводом, соединенным с выходом шестого регистра, входом первого блока сравнения, выходом одновибратора и входом первого элемента задержки, выход которого соединен с первым входом первого триггера, второй вход которого соединен со второй шиной и входом одновибратора, выход - со второй ишной, соединенной со входами пятого и шестого регистров, выходом второго триггера входом и выходами блока усилителей, первым входом пятого элемента ИЛИ, первым входом второго триггера и первым входом элемента И-НЕ, второй вход которого соединен с блоком управления выводом, выход - со входом блока управления выводом, выходы дешифратора соединены со входами шестогб элемента ИЛИ, выход коюрого соединен со входом второго блока приемников, вход третьего регистра соединен с выходом седьмого элемента ИЛИ, входы которого соединены с соответствующими выходами дешифратора адреса и входами седьмого регистра, другой вход которого соединен с блоком управления выводом, бходами второго элемента задержки и восьмого регистра, выход которого соединен с одними входами блока усилителей и входом второго блока сравнения, выход которого соединен со входом восьмого регистра, выход седьмого регистра соединен с другими входами блока усилителей, выход второго элемента задержки соединен с вторым входом второго триггера, второй вход пятогр элемента ИЛИ соединен с первой шиной, выход - с блоком управления выводом и входом третьего элемента задержки, выход которого соед1шен с блоком управления выводом. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 602937, кл. G 06 F 3/04, 1978. 2.Блок интерфейсный типовой БИТ. Техническое описание 26.700.004.ТО, 1973 (прототип).

7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1987 |

|

SU1411764A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Устройство для сопряжения двух электронно-вычислительных машин с внешними абонентами | 1985 |

|

SU1264192A1 |

| Станция локальной вычислительной сети | 1990 |

|

SU1805474A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для подключения источников информации к общей магистрали | 1989 |

|

SU1679498A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

Авторы

Даты

1980-11-23—Публикация

1978-12-20—Подача