(54) ЦИФРОВОЙ ВЫЧИСЩТЕЛЬ ФУНКЦИЙ СИНУСА И КОСИНУСА

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой вычислитель синуса и косинуса | 1977 |

|

SU682905A1 |

| Цифровой генератор гармонических сигналов | 2015 |

|

RU2616877C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬ ФУНКЦИЙ СИНУСА И КОСИИУСА | 1971 |

|

SU419896A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1339555A1 |

| Цифровой преобразователь координат | 1980 |

|

SU942004A1 |

| Вычислитель функций синуса и косинуса | 1976 |

|

SU628491A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1312737A1 |

| Цифровой вычислитель функций синуса и косинуса | 1977 |

|

SU690490A1 |

| Устройство для вычисления тригонометрических функций | 2016 |

|

RU2614931C1 |

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

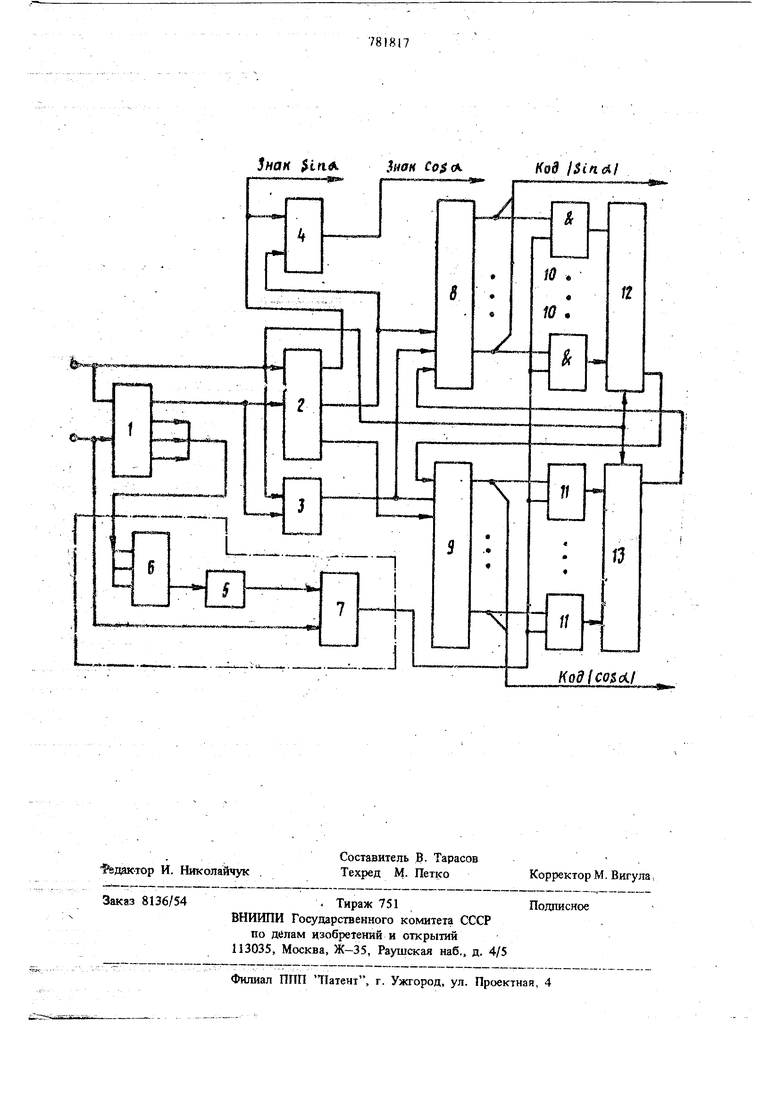

Изобретение относится к автоматике к вычислительной технике и может быть использова но в устройствах цифровых радиально-круговых разверток, в устройствах цифрового автоматического управлеиия и в устройствах отображения графической информации. Известно устройство для вычисления функци синуса и косинуса, в котором эти зависимости получают из параллельного кода аргумента при помощи генератора гармонических колебаний с ударным возбуждением и с использованием цифроаналоговой техники. Точность выработки этих зависимостей связана с точностью аналоговых узлов, используемых в устройстве 1 . Наиболее близким по технической сущности к предлагаемому является цифровой вычислитель функций синуса и косинуса, содержащий два счетчика, три сумматора-, элемент ИЛИ, два регистра и две группы элементов И, причем первый вход первого счетчзоса соед1шен с первым входом второго счетчика, первыми входами первого и второго сумматоров и первым входом элемента ИЛИ, второй вход которого подключен к первому выходу первого счетчика И второму входу второго счетчика, выход элемента ИЛИ соеданен с первыми входами пер,вого и второго регистров, первый выход второго счетчика подключен к первому входу первого сумматора, второй выход второго счетчика соединен со вторым входом первого суммятора и вторым входом первого регистра, третий выход второго счетчика подключен ко второму входу второго регистра, выходы первого регистра соединены с первьпии входами элементов И первой группы, а выходы вторсмго регистра подключены к первым входам элементов И второй группы, выходы элементов И первой группы через второй сумматор соединены с третьим входом второго регистра, а выходы элементов И второй группы через третий сумматор подключены к третьему входу первого регис:фа 2J. Известное устройство имеет низкое быстродействие. Цель изобретения - повыщение быстродействия. Поставленная цега достигается тем, что в устройство введены два дополнительных зйемента ИЛИ и элемент задержки, причем трутт выходов первого счетчика соединена с соответствующими входами первого дополнительного элемента ИЛИ, выход которого через элемент задержки подключен к первому входу второго дополнительного элемента ИЛИ, второй вход которого соединен со вторым входом первого счетчика, а выход - со вторыми вЬсодами элементов И первой и второй групп. На чертеже схематически изображен цифровой вычислитель. Вычислитель содержит два счетчика 1 и 2, элемент ИЛИ 3, первый, сумматор 4, элемент 5 задержки, два дополнительных элемента ИЛИ 6 и 7, два регистра 8 и 9, первую группу элементов И 10, вторую rpjmny элементов И Пи второй и третий сумматоры 12 и 13. Вычислитель функции синуса и косинуса работает слёцующкм образом. . На устройство поступают импульсы прираще йий аргумента oL и контрольный импульс арг мента oCfj. По этим сигналам вычислитель вырабатывает 12-ти разрядный код сС и 11-ти разрядные коды dihct и ,У которых 11-е разряды - знаковые. Импульсы приращений аргумента подсчитываются счетчиками 1 и 2, в которых вырабатыва ется код. Разряды счетчика 2 имеют веса 2 и ЗГ и содержат информацию о знаках и . Поэтому прямой выход старшего разряда счетчика 2 является выходом с вычислителя знакового разряда кода ащ d. а прямые выходы обоих разрядов счетчика 2 подаются на входы сумматора 4, который вырабатывает знаковый разряд кода COS d- и выдает его на выход вычислителя. Определение кодов чисел/SmdL/ и/cosol/ в вычислителе основано на извеспсых теоретических полоЧ(ениях .osxdx,cosx -JsmxdLx Это вычисление в устройстве производится на двух цифровых интеграторах с параллельны переносом числа из регистра подынтегральной функ1ши. Первый из интеграторов образован регистром 8, первой группой элементов И 10 и сумматором 12, а второй - регистром 9, второй группой элементов И И и сумматором 13.; Вычисление кодов d / и /fcOSd / ведет ся последовательно по квадрантам, вначале каждого из котьрых производится установка начальных условий в регистр 8 и регистр 9.. Коррекция работты вычислителя и установка начальных условий в первом квадранте осущес вляется по контрольному импульсу угла dLg который устанавливает счетчики 1 и 2 в нулевое состояние, а сумматор 13 - в единичное и через элемент ИЛИ 3 переводит регистры 8

781817 И 9 В нулевое состояние. Гак как сигналы на управляющих входах регистров 8 и 9 onpefделяются соответственно прямым и инверсным значениями первого разряда счетчика 2, то с выходов регистра 8 снимаются нули, а регистра 9 - единицы. ,. Это соответствует начальным условиям в первом квадранте угла ,SmAo 0 COS d-Q 1 Установка начальных условий во втором, третьем и четвертом квадрантах угла осуществляется по импульсу переполнения счетчика I, который через элемент ИЛИ 3 устанавливает регистры 8 и 9 в нулевое состояние. Начальные условия во втором, третьем и четвертом квадрантах угла соответствуют условиям. „ , я; . квадрант второй: oL- ,coscLOi третий:оС - ПГ, S-in dl O,/coso(J--(, четвертый: di 5-ir,/eiiic cf--1,cosd О. Интегрирование ведется по аргументу представлением d. на входе цифровых интеграторов (вторых входах всех схем И) последовательностью импульсов с весом каждого импульса 2 рад. Число импульсов в этой последовательности, приходящихся на один квадрант угла, равно .(l°-t)c-i607. Это число импульсов N вырабатывается элементами 5,6 и 7 путем суммировАпия входных импульсов аргумента , приходящих со входа вычислителя на второй вход элемента ИЛИ 7, с приходящей на ее первый вход с элемента 5 задержки корректирующей последовательности импульсов. Корректирующая последовательность импульсов вырабатывается элементом ИЛИ 6, который суммирует три не совпадающие друг с другом последовательности импульсов, вырабатываемых счетчиком 1. Последовательности импульсов, которые вырабатывает счетчик 1 по импульсам аргумента, приходящим на вход счетчика с входа вычислителя, представляют собой счетные импульсы установки в единицы триггеров первого, четвертого и седьмого разрядов. Следовательно, после каждого обнуления счетчика 1 и поступлении на вход вычислителя 1023 импульсов аргумента на выходе элемента 7 вырабатывается последовательность импульсов, число импульсов в которой равно УУ- 1023 + 512 +64 + 8 к 1607 Погрещность такого представления утла .at последовательностью импульсов на выходе элемента 7 не превьщ1ает ±2 рад. Импульсы с выхода элемента 7 поступают на управление сложением. По каждому иэ этих импульсов

производится опрос элементов И первой и второй групп 10 и 11, при котором производится передача содержимого регистра 8 в сумматор

12и содержимого регистра 9 в сумматор 13 косинуса. При этом сумматор 12 и сумматор

13запоминают остатки суммирования и вырабатывают соответственно приращение косинуса и приращение синуса. Приращение синуса с выхода сумматора 13 поступает на суммирующий вход регистра 8, а прира цение косинуса с выхода сумматора 12 - на суммирующий вход регистра 9. Приращение функций на суммирующие входы регистров 8 и 9 поступают в виде наличия или отсутствия импульса.

с весом 2 а содержимое этих регистров меняется только после момента окончания импульсов на их суммирующих входах. На выходах регистра 8 вырабатывается 10-ти разрядный код I Siv сИ , а на выходах регистра 9 10-ти разрядный код ICcSSii.

Из описания работы вычислителя следует, что при поступлении на его вход импульса аргумента каждый цикл интегрирования содержит один или два равноценных такта суммирования

Следовательно цикл интегрирования длится или () ,

Ы

НЬ - длительность входного импульса аргдеoLI

ГУ мента;

t. - длительность задержки элемента 5

задержки.

Технико-экономическая эффективность предлагаемого изобретения заключается в том, что вычислитель функций синуса и косинуса имеет простую структуру, не содержит тактирующих узлов или блоков управления и может вычислять функт и синуса и косинуса аргумента, изменяющегося с высокой скоростью.

Формула изобретения Цифровой вычислитель функций синуса и косинуса, содержащий два счетчика, три сумматора, элемент ИЛИ, два регистра и две группы элементов И, причем первый вход перв(зго счетчика соединен с первым входом второго счетчика, первыми входами первого и второго сумматоров и первым входом элемента ИЛИ, второй вход которого подключен к первому выходу первдао счетчика и второму входу второго счетчика, выход элемента ИЛИ соединен с первыми входами первого и второго регистро первый выход второго счетчика подключен к первому входу первого сумматора, второй выход второго счетчика соединен со вторым входом первого сумматора и вторым входом первого регистра, третий выход второго счетчика подключен ко второму входу второго регистра, выходы первого регистра соединены с первыми входами элементов И первой группы, а выходы второго регистра подключены к первым входам элементов И второй группы, выхо)ы элементов И .первой группы через второй сумматор соединены с третьим входом второго регистра, а выходы элементов И второй группы через третий сумматор подключены к третьему входу первого регистра, отличающийся тем, что, с целью повышения быстродействия, в него введены два дополнительных элемента ИЛИ и элемент задержки, причем группа выходов первого счетчика соединена с соответствующими входами первого дополнительного элемента ИЛИ, выход которого через элемент задержки подключен к первому входу второго дополнительного элемента ИЛИ, второй вход которого соединен со вторым входом первого счетчика, а выход - со вторыми входами элементов И первой и второй групп.

Источники информации, принятые во внимание при экспертизе

5нок 1«.лЗяан Со$л.

. .....и.. .ЗМ

«

П

Кой

0

Kodlco oil

Авторы

Даты

1980-11-23—Публикация

1976-08-13—Подача