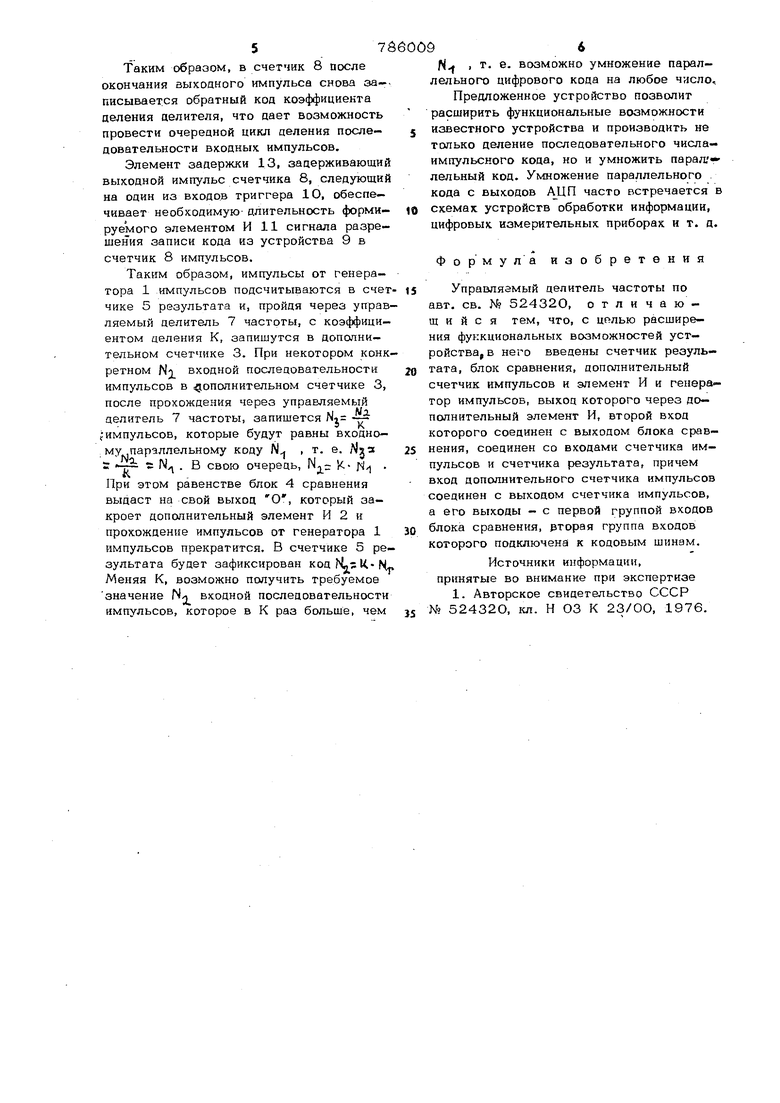

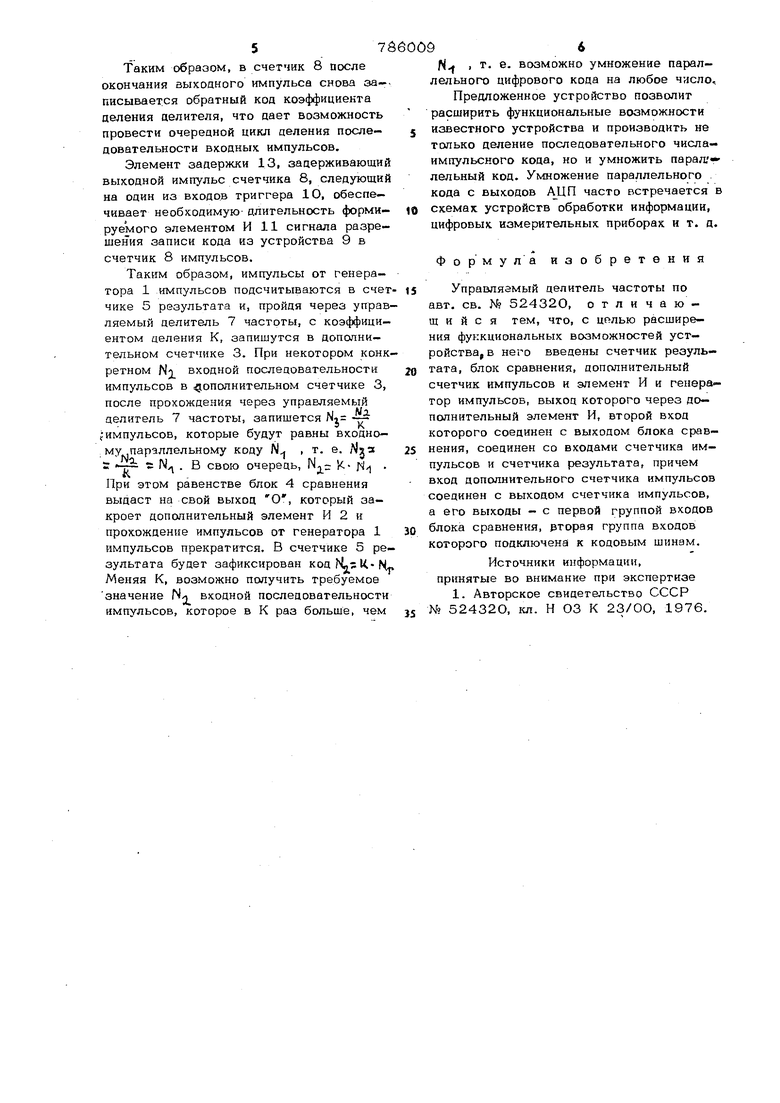

Изобретение относится к импульсной и вычислительной техлике. оно может быть использовано в различных масшта- .бирующих преобразованиях измерительной информации и является дополнительным к основному изобретению по авт. св № 524320. Предлагаемый целитель частоты по основному авторскому свилегельству содержит счетчик импульсов, устройство записи обратного кода, элементы И и НЕ элемент задержки, вход которого соединен со входом элемента НЕ и выходом счетчика импульсов, и триггер, первый ВХ.ОП которого соединен с выходом элемента задержки, а второй - с выходом элемента НЕ и одним из входов элемента И, второй вход которого соединен с выходом триггера У-1Недостатком описанного делителя час тоты является ограниченность его функциональных возможностей, возникающая из-ва невозможности осуществлять умно жение параллельного цифрового кода. Цель изобретения - расширение функ -циональных возможностей. С этой целью в управляемый целитель частоты, содер жащнй счетчик импульсов, установочный вход которого соединен с выходом уст- ройства записи обратного кода, триггер, выход которюго подключен к одному из входов элемента И, элемент задержки н элемент НЕ, входы которых подключе« ны к выходу счетчика импульсов, выход элемента задержки подключен к первому входу триггера, а выход элемента НЕ - ко второму входу триггера н ко втор(Ж-1у входу элемента И, выход которого соединен с .управляющим входом устройства записи обратного кода, введены счетчик результата, блок сравнения, дополнительные счетчик импульсов и элемент И и генератор импульсов, выход которого через дополнительный элемент И, второй вход которого соединен с выходом блока сравнения, соединен со входами счетчи- каимпульсов исчетчика результата,причем вход дополнительного счетчика импульсов 7 соединен с выходом счетчика импульсов а его выходы - с первой группой входов блока сравнения, вторая группа входов которого подключена к кодовым шинам устройства. На фиг. 1 изображена структурная электрическая схема устройства. В основу работы устройства положен принцип взаимообратимости и симметричности от носительно биссектрисы первого и треть го координатных углов, линейных функций деления и умножения. На фиг. 2 приведен график работы делителя частоты, у которого из Ng,, входны( импульсов на выход проходит /Vn, ..- s . , где коэффициент К-любое целое число; и график работы умножителя на KNj, К- . Из этих графиков видно, что для того чтобы получить функцию умножения аргумента ON (входной параллельный код) на К, т. е. отрезок , на вход управляемогоделителя частоты (с коэффициентом деления К) . необходимо подать такое число импульсов N- (отрезок ON,,), функция деления которого (отрезок ,) ) была бы равна первоначальному аргументу ON , , т. е. 2 2ic:N.,npH этом равенстве JSIis-siON, . О/1,и является функs:ON , О/1и цией умножения аргумента О N(входной параллельный код) на К, так как О NI ., вм, т. е. ON,.ON . Управляемый делитель частоты, изображенный на фиг, 1, содержит генератор 1 импульсов, дополнительный элемент И 2, дополнительный счетчик 3 импульсов, блок 4 сравнения, счетчик 5 результата. Кроме того, делитель содержит кодовые шины 6, управляемый делитель частоты 7 по основному изобретению, включающий счетчик 8 импульсов, устройство 9 записи обратного кода триггер 10, элемент И 11, элемент НЕ 12 и элемент задержки 13. Шины 6 соединены с первыми входами блока 4 сравнения, выход которого соединен со вторым входом дополнительного элемента И 2, первый вход которого соединен с генератором 1 импульсов а выход - со входами счетчика 5 резуль тата и управляемого делителя 7 частоты выход которого соединен с дополнительным счетчиком 3 импульсов, выходы двоичных разрядов которого соединены с первыми входами блока 4 сравнения. В исходном положении догюлнительны счетчик 3 в состоянии О, на шины 6 также подан нулевой параллельный код. Блок 4 сравнения фиксирует равенство 4 равниваемых кодов и выдает при этом а свой выход О, который закрывает ополнительный элемент И 2 по второму ходу. В некоторый момент времени на шины поступает параллельный цифровой код Н , который необходимо умножить на К коэффициент К .заранее устанавливается управляемом делителе 7 частоты). шок 4 сравнения фиксирует неравенство одов в дополнительном счетчике 3 ( в нем по прежнему нулевой код) и входного параллельного цифрового кода N , и выдает на свой выход 1. Это приводит к открытию дополнительного элемента И 2, через который начинают проходить импульсы от генератора 1 импульсов. Эти импульсы шасчитываются счетчи ком 5 результата и попадают на вход управляемого делителя 7 частоты. Управляемый делитель 7 частоты (согласно описанию изобретения по авт. св. № 524320) работает следующим образом. По шине 14 в устройство 9 записи обратного кода в определенный момент времени поступает обратный код коэффициента деления делителя. Этот код хранится в устройстве 9 до тех пор, пока по шине. 14 не прступит новый код. По сигналу, сформированному элементом И 11, устройство 9 записывает хранящийся в нем код в счетчик импульсов. Счетчик 8 импульсов формирует и выдает на выход устройства импульс переполнения, когда в него поступает количество импульсов, равное коэффициенту деления, записанному в нем в обратном ; коде. Сначала триггер 10 находится в состоянии О, при этом на первом входе атемента И 11 удерживается запрещающий потенциал. При появлении импульса на выходе счетчика 8 элемент НЕ 12 формирует запрещающий сигнал на второй вход элемента И 11, длительность кото-, рого равна длительности импульса. Этим же сигналом триггер 10 устанавливается в 1, формируя сигнал разрешения на первый вход элемента И 11. По окончаннии импульса на выходе счетчика 8 на второй вход элемента И 11 поступает разрешающий потенциал, в результате чего на его выходе появляется сигнал разрешения записи из устройства 9 в счетчик 8 импульсов. Таким образом, в счетчик 8 псх;ле окончания выходного импульса снова записывается обратный код коэффициента деления целигеля, что дает возможность провести очередной цикл деления последовательности входных импульсов. Элемент задержки 13, задерживающий выходной импульс счетчика 8, следующий на один из входов триггера 1О, обеспечивает необходимую- длительность формируемого элементом И 11 сигнала разрешения записи кода из устройства 9 в счетчик 8 импульсов. Таким образом, импульсы от генератора 1 импульсов подсчитываются в счет чике 5 результата и, пройдя через управ ляемый делитель 7 частоты, с коэффициентом целения К, запишутся в дополнительном счетчике 3. При некотором конк ретном f входной последовательности импульсов в .дополнительном счетчике 3, после прохождения через управляемый делитель 7 частоты, запишется Ni -5-S ;импульсов, которые будут равны входному параллельному коду N , т. е. Nja Т - N . В свою очередь, К- j . При этом равенстве блок 4 сравнения выдаст на свой выход О, который закроет дополнительный элемент И 2 и прохождение импульсов от генератора 1 импульсов прекратится. В счетчике 5 результата будет зафиксирован код l,;:,-fi( Меняя К, возможно получить требуемое значение N входной последовательности импульсов, которое в К раз больше, чем fi , т. а. возможно умножение параллельного цифрового кода на любое число. Предложенное устройство позволит расширить функциональные возможности известного устройства и производить не только деление последовательного числа- импульсного кода, но и умножить парал. лельный код. Умножение параллельного . кода с выходов часто встречается в схемах устройств обработки информации, цифровых измерительных приборах и т. д. Формула изобретения Управляемый делитель частоты по авт. св. № 524320, отличающийся тем, что, с целью расширения функциональных возможностей устройства, в него введены счетчик резуль- тата, блок сравнения, дополнительный счетчик импульсов и элемент И и генератор импульсов, выход которого через дополнительный элемент И, второй вход которого соединен с выходом блока сравнения, соединен со входами счетчика импульсов и счетчика результата, причем вход дополнительного счетчика импульсов соединен с выходом счетчика импульсов, а его выходы - с первой группой входов блока сравнения, рторая группа входов которого подключена к кодовым шинам. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 52432О, кл. Н ОЗ К 23/ОО, 1976.

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1988 |

|

SU1626315A1 |

| Цифровой измеритель отношения временных интервалов | 1984 |

|

SU1188696A1 |

| Масштабно-временной преобразователь | 1982 |

|

SU1045218A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2042261C1 |

| Цифровой умножитель частоты | 1982 |

|

SU1088107A1 |

| Устройство для синхронизации многоканального воспроизведения с носителя магнитной записи | 1984 |

|

SU1150660A1 |

| Делитель частоты с дробным коэффициентом деления | 1986 |

|

SU1347184A1 |

| Управляемый делитель частоты следования импульсов | 1978 |

|

SU750742A1 |

| Вычислительное устройство | 1983 |

|

SU1120324A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ М-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2112313C1 |

Авторы

Даты

1980-12-07—Публикация

1978-10-23—Подача