(54) СИСТЕМА МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1974 |

|

SU526902A1 |

| Микропрограммный процессор с самоконтролем | 1980 |

|

SU1007109A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Процессор микро-ЭВМ | 1979 |

|

SU1042026A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Арифметическое устройство с микропрограммным управлением | 1989 |

|

SU1725216A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

Изобретение относится к вычисли1тельной технике, в частности к устройствам микропрограммного управления, и может быть использовано при построении цифровых вычислительных машин и контроллеров с микропрограм мным управлением. Известно микропрограммное устройство управления l,содержащее блок памяти, регистры, схемы приема информации, генератор импульсов, сч чик тактов, элементы И, НЕ, дешифра торы, формирователь адресов микропрограммных слов. Сложность такого устройства обус ловлена большим количеством разноти ного о борудов а н ия. Наиболее близким к изобретению по технической сущности и достигае мому результату является система микропрограммного управления 2, содержащая адресную и управляющую памяти микрокоманд, память команд, арифметико-логическое устройство, интерфейс ввода-вывода, генератор пульсов, регистр адреса памяти мик команд, .регистр условий, узел вьще ления логических условий. Однако такое устройство требует большого количества оборудования и значительного увеличения объема адресной памяти микрокоманд в случае увеличениячисла ветвлений микропрограмм. Цель изобретения - сокращение оборудования. Эта цель достигается тем, что система микропрограммного управления, содержащая генератор импульсов, первый выход которого соединен с управляющими входами памяти команд, адресной и управляющей памятями микрокоманд, первый выход адресной памяти микрокоманд связан с адресным входом регистра адреса памяти микрокоманд, выход памяти команд соединен с информационным входом регистра адреса памяти микрокоманд, разрядный выход которого подключен к адресному входу управляющей памяти микрокоманд, выход которой соединен с входом памяти команд и входом арифметикологического блока, а вход генератора импульсов является входом устройства, содержит комбинационный сумматор и констант переходов. При этом выход логических условий арифметико-логического блока соединен с входом логических условий памяти констант переходов, управляющий вход которой соединен с вторым выходом генератора импульсов, а выхо памяти констант переходов - с входом констант перехода комбинационного сумматора, адресный вход которого связан с разрядным выходом регистра адреса памяти микрокоманд. Выход комбинационного сумматора подключен к входу адресной памяти микрокоманд второй выход которой связан с адресным входом памяти констант переходов,

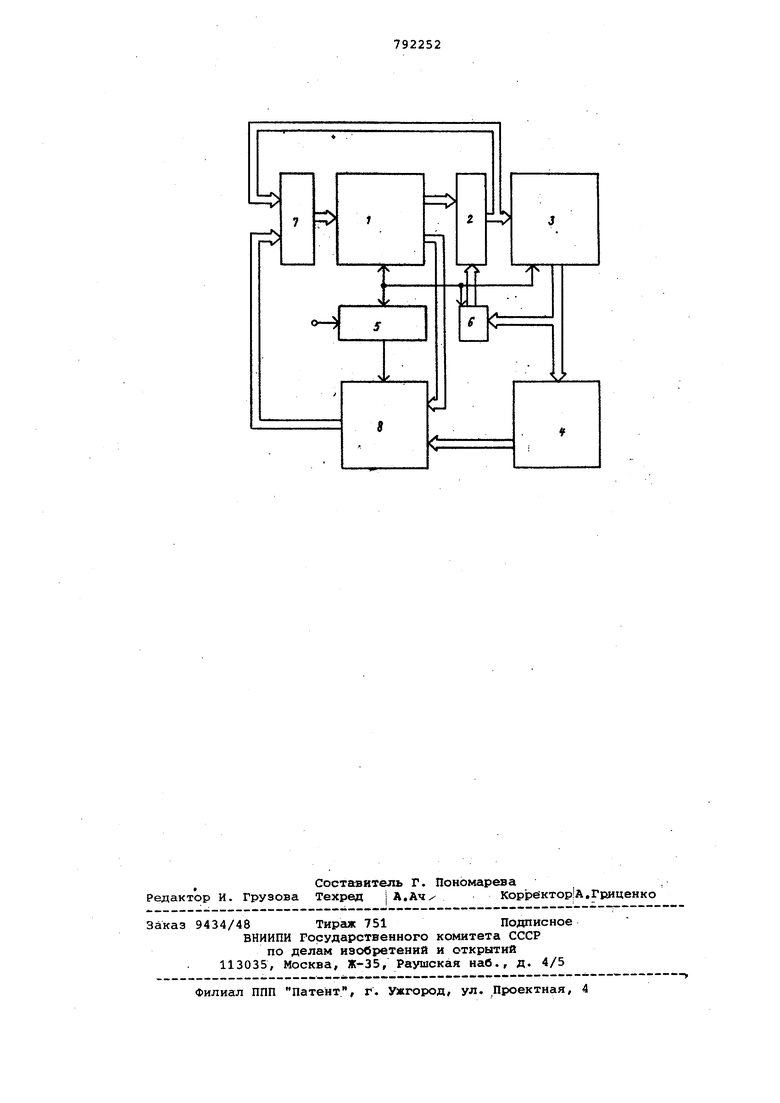

Блок схема микропрограммного устройства управления приведена на чертеже ,

Система микропрограммного управлейия содержит адресную память 1 микрокоманд, регистр 2 адреса памяти микрокоманд, управляющую память 3 микрокоманд, арифметико-л.огическое устройство 4, генератор 5 импульсов, память 6 команд, койбинационный сумматор 7, память 8 констант переходов

Адресная память 1 микрокоманд содержит адресные микрокоманды, формат которых включает гщрес микрокоманды управляющей памяти 3 микрокоманд и вторую группу адресов памяти 8 констант переходов. Регистр 2 адреса памяти микрокоманд выдает адрес микрокоманды управляющей памяти 3 микрокоманд, который используется также в комбинационном сумматоре 7 для выработки следующего адреса адресной памяти 1 микрокоманд. Управляющая память 3 микрокоманд содержит набор различных управля ощих микрокоманд для задания режимов работы памяти 6 команд и арифметико-логического устройства 4.

Логические условия, вырабать1ваемые арифметико-логическим устройством, используются в качестве первой группы адресов памяти 8 констант переходов.

Устройство работает следующим образом.

В каждом цикле, задаваемом генератором 5 импульсов, из адресной памяти 1 микрокоманд считывается текущая адресная микрокоманда. Част адресной микрокоманды используется для адресации памяти 8 констант переходов. Другая часть заносится в регистр 2 адреса памяти микрокоманд, который определяет адрес управляющей памяти 3 микрокоманд. Этот же адрес подается на пёрвьой вход комбинационного сумматора 7 для определения следующего адреса .адресной памяти 1 микрокоманд. Микркоманда, считанная из управляквдей памяти 3 микрокоманд, подаётся на . вход арифметико-логического устройсва 4, которое по выполнениюопераций формирует логические условий, явл5пощиеся первой группой адресов памяти 8 констант переходов. При отсутствии ветвления в микропрограмме

адрес следую1пей микрокоманды адресной памяти микрокоманд определяется содержимым регистра адреса памяти микрокоманд, поскольку константа перехода в этом случае равна 0. Определение адреса следующей микрокоманды в случае ветвления микропрограммы осуществляется путем суммирования содержимого регистра адреса памяти . микрокоманд и константы перехода,. считанной из памяти констант переходов .

Наличие в составе данного устройства, комбинационного сумматора и памяти констант переходов позволяет исключить дополнительные схемы управления адресной памяти микрокоманд, что обеспечивает сокраидение количества оборудования, а исключение повторяющихся микрокоманд веде.т к уменьшению объема памяти микрокоманд.

Формула изобретения

Система микропрограммного управления, содержащая генератор импульсов, первый выход которого соединен с управляющими входами памяти команд, адресной и управляквдей памятями микрокоманд, первый выход гщресной памяти микрокоманд соединен с адресным входом регистра адреса памяти микрокоманд, выход памяти команд соединен с информационным входом регистра адреса памяти микрокоманд, разрядный выход которого подключен к адресному входу управляющей памяти микрокоманд выход которой соединен с входом памяти команд и входом арифметико-логического блока, а вход генератора импульсов является входом устройства отличающаяся тем, что, с целью сокращения оборудввания, оно содержит комбинационный сумматор и память констант переходов,причем выход логических условий арифметикологического блока соединен с логическим входом условий памяти констан перекодов, управляющий вход которой соединен с вторым выходом генератора импульсов, а выход памяти констант соединен с входом констант перехода комбинационного сумматора, адресный вход которого соединен с разрядным выходом регистра гщреса памяти микрокоманд, а выход комбинационного сумматора подключен к входу адресной памяти микрокоманд, второй выход которой связан с адресным входом памяти констант переходов.

Источники информации, Q .принятые во внимание при экспертизе

45 кл. G 06 F 9/16, 1977 (прототип).

Авторы

Даты

1980-12-30—Публикация

1979-01-04—Подача