Изобретение относится к вычислительной технике и может быть использовано при построении процессоров, выполняющих операции двоичной и десятичной арифметики.

Известны арифметические устройства с микропрограммным управлением, построенные на основе четырехразрядных двоичных арифметико-логических блоков (микропроцессорных секции-МПС), например процессор ЭВМ СМ-1420. В него входят арифметико-логический модуль, содержащий 4 МПС типа К1804ВС2 и микропрограммное устройство управления (МП У).

Недостатком устройств является низкое быстродействие при выполнении операций над десятичными числами из-за отсутствия микроопераций десятичной коррекции. Выполнение в таких устройст - вах десятичных операций чисто микропрограммным путем с потетрадной обработкой ведет к значительному увеличению затрат времени.

Известны также устройства на базе четырехразрядных блоков, имеющих десятичные операции, таких как микросхемы К1800ВС1.

Использование данных устройств не всегда возможно или желательно, так как блоки без десятичных операций могут иметь лучшие характеристики - наличие внутренней памяти, надежность, температурный диапазон и т.п.

Наиболее близким к предлагаемому является устройство, состоящее из блока обработки данных (БОД), включающего в себя 4 двоичных 4-разрядных МПС, соединенных по цепям сдвига и переноса, схему ускоренного переноса, регистры входных и выходных данных и блок микропрограммного управления, содержащий схему управления последовательностью микрокоманд (УПМ), микропрограммную память, регистр микрокоманд (РМК), мультиплексор кода условия (МКУ). Выходы РМК подключены к управляющим входам БОД, УПМ и МКУ, адресному входу УПМ и одному из информационных входов БОД.

Недостатком устройства является низкое быстродействие при выполнении десятичных операций, так как отсутствие цепей десятичной коррекции пиводит к необходимости большого числа микрокоманд (МК) для их выполнения.

Цель изобретения - повышение быстродействия при выполнении десятичных операций путем внесения в устройство дополнительных связей, облегчающих микропрограммирование этих операций.

Арифметическое устройство с микропрограммным управлением содержит п/4

двоичных арифметико-логических блоков (п - разрядность информации), блок памяти М К, регистр МК, блок формирования адресов МК и первый мультиплексор. Выход блока формирования адресов соеди0 нен с адресным входом блока памяти МК, выход которого соединен с входом регистра МК. Выходы разрядов поля задания режима адресации регистра МК соединены с входами разрядов задания режима блока

5 формирования адресов МК. Вход условия переходов этого блока соединен с выходом первого мультиплексора, управляющий вход которого соединен с выходами разрядов поля задания вида переходов ре0 гистра МК.

Выходы разрядов поля задания константы регистра МК соединены соответственно с разрядами информационного входа устройства. Выходы разрядов уст5 ройства соединены соответственно с выходами разрядов результата с первого по n/4-й двоичных арифметико-логических

блоков. Выход переноса k-ro (k 1п/4-1)

соединен с входом переноса (k+1)-ro двоич0 ного арифметико-логического блока, выходы переноса знака, признака нуля и признака переполнения п/4-го блока-соответственно с информационными входами первого мультиплексора.

5 Выходы задания вида операции регистра МК соединены с входами задания вида операции арифметико-логических блоков с первого по n/4-й. Вход задания вида операции устройства соединен с установочным

0 входом блока формирования адресов МК. Выходы старших разрядов поля задания адреса регистра МК соединены с входами старших разрядов адреса блока формирования адресов МК.

5 С целью повышения быстродействия в устройство включен второй мультиплексор, причем выходы переносов двоичных арифметико-логических блоков с первого по п/4- й соединены соответственно с разрядами

0 первого информационного входа второго мультиплексора. Разряды его второго информационного входа соединены соответственное выходами младших разрядов поля задания адреса регистра МК. Выходы разря5 дов второго мультиплексора соединены соответственно с входами младших разрядов адреса блока формирования адресов МК. Управляющий вход второго мультиплексора соединен с выходом признака десятичной операции регистра МК.

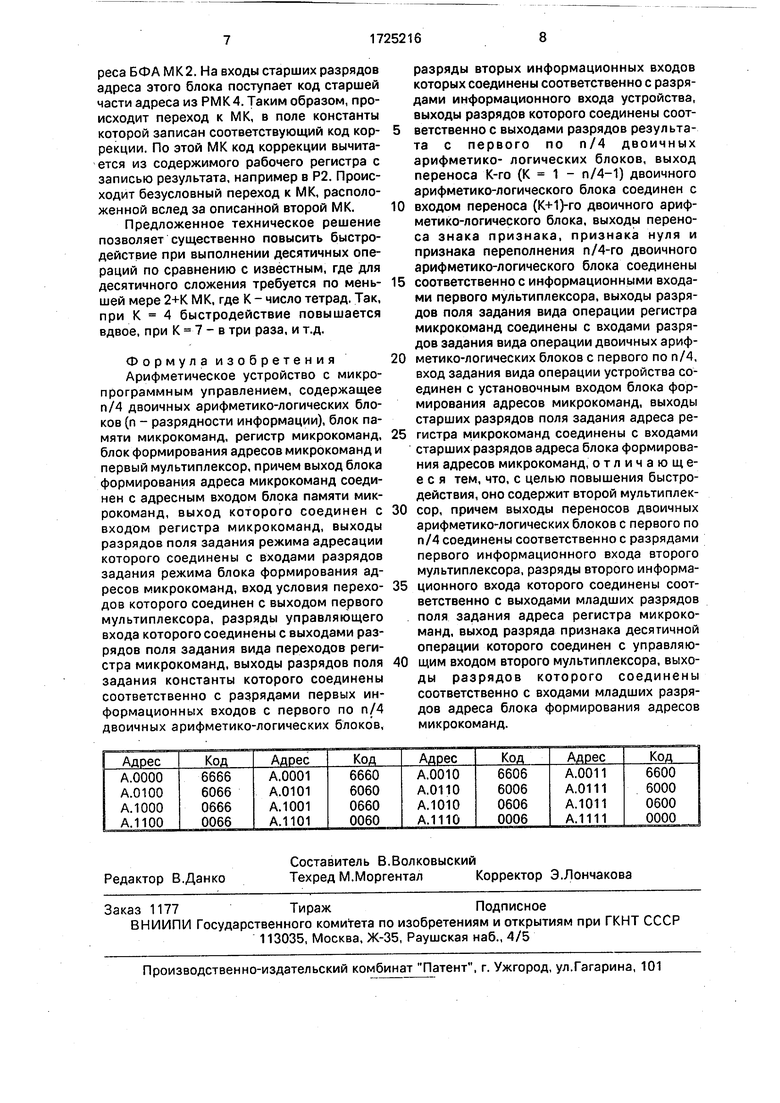

Изобретение иллюстрируется на примере устройства для обработки 16-разрядных двоичных или 4-разрядных десятичных чисел. Суть изобретения состоит в использовании выходов межтетрадных переносов в качестве составной части адреса следующей МК, Адресуемые МК прибавляют или вычитают записанный в поле константы код коррекции к предварительному результату сложения десятичных чисел. Так, при обработке 4-разрядных десятичных чисел возможны 16 различных значений кода коррекции, записанных в МК с адресами

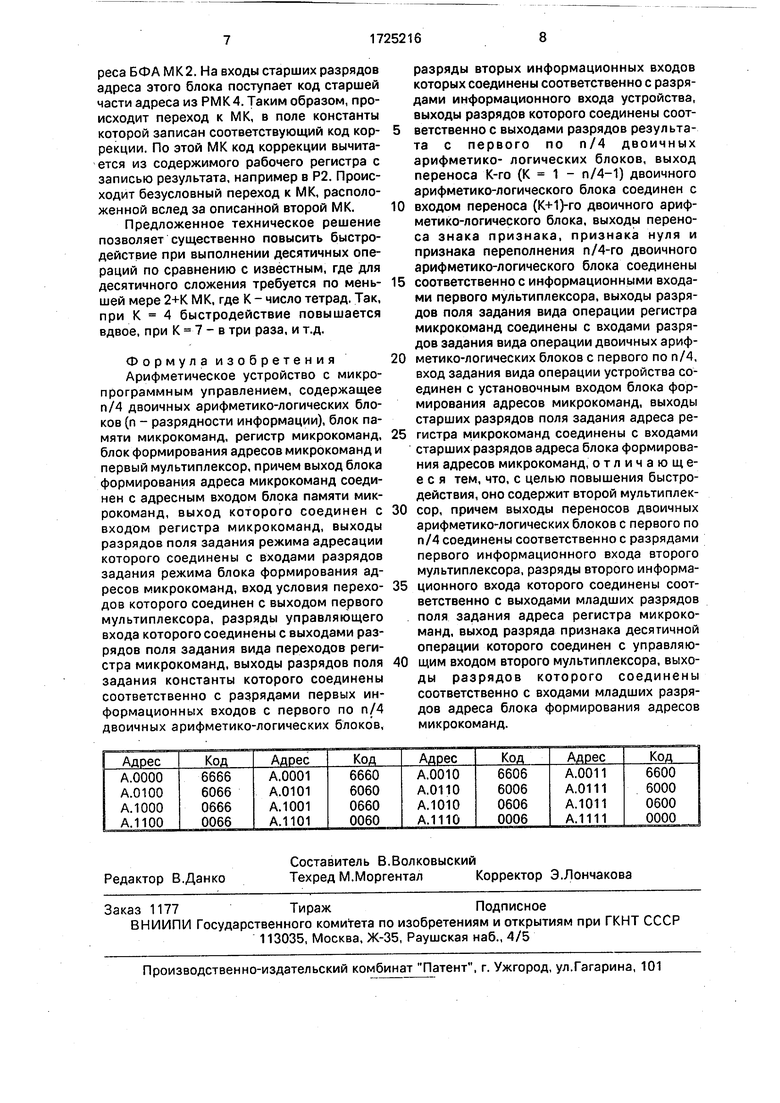

А.ОООО, А.0001 А.1110, А.1111, где А старшая часть адреса, младшие биты которого задаются значениями переносов. Значения кодов коррекции для кода 8421 приведены в таблице.

Рассмотрим пример сложения чисел 3458 и 4089, выполняемого в три микрокоманды:1. Прибавление кода 6666 к первому слагаемому

0100 0110

0101 0110

1000 0110

2. Прибавление второго слагаемого(код переноса 0011)

1010 0000

1011 1000

1110 1001

3. Вычитание кода коррекции,

содержащегосяв МК с адресомА.0011

1101 1011 0100 0111 -0110 0110 0000 0000 0111 0101 0100 0111 7547.

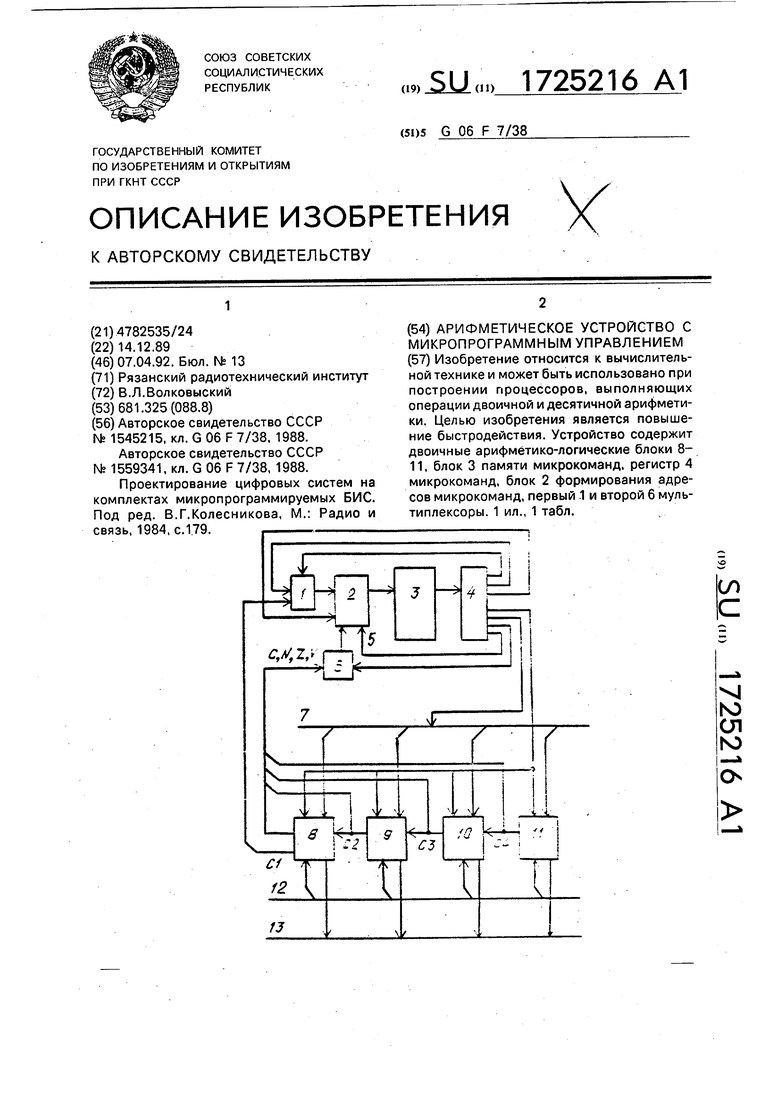

На чертеже приведена схема арифметического устройства с микропрограммным управлением.

Устройство включает в себя мультиплексор (М2) 1 адреса ветвления, блок 2 формирования адреса МК (БФА МК) с установочным входом 5, память 3 микрокоманд (ПМК), регистр 4 микрокоманд (РМК), мультиплексор (М1) 6 кода условия, четыре (в общем случае п/4) 4-разрядных двоичных арифметико-логических блока 8-11, соединенных по цепям двоичного переноса. БФА

МК и двоичные блоки могут быть реализованы, например, на микросхемах 1804ВУ4 и 1804ВС2 соответственно. Информационные выходы арифметических блоков соединены с 16-разрядным информационным

0 выходом 13 устройства. Информационные входы этих блоков соединены соответственно с выходами поля константы РМК (первый информационный вход 7) и внешним входом (второй информационный вход 12).

5 Адресный вход ПМК 3 соединен с выходом БФА МК2, выход ПМКЗ-с входом РМК 4. Выход РМК, задающий режим адресации, соединен с управляющим входом блока 2. Выход, задающий условие перехода, соеди0 нен с управляющим входом мультиплексора 6, выход поля константы РМК - с первым информационным входом 7, выход, задающий вид операции - с управляющими входами блоков 8-11. Выход, задающий старшую

5 часть адреса, подключен к входу старших разрядов адреса блока 2, выход, задающий младшую часть адреса, соединен с первым информационным входом мультиплексора 1, с управляющим входом которого соеди0 нен выход РМК, содержащий признак десятичной операции. Разряды второго информационного входа мультиплексора 1 соединены соответственно с выходами С1, С2, СЗ, С4 переносов блоков 8-11. Выход

5 мультиплексора 1 соединен с входом младших разрядов адреса БФА М К 3. К информа- ционному входу мультиплексора 6 подключены выходы С, N, Z, V со старшего блока, соответствующие признакам перено0 са, знака, нуля и переполнения. Выход мультиплексора 6 соединен с входом условия перехода БФА МК 2.

Работу устройства рассмотрим на примере сложения чисел в коде 8421, записан5 ных во внутренних регистрах Р1 и Р2 арифметико-логических блоков. По первой МК содержимое Р1 складывается с кодом 6666, записанным в поле константы МК и поступающим на первый информационный

0 вход 7 арифметико-логических блоков. Результат записывается в рабочие регистры блоков. Вторая МК, следующая в естественном порядке, задает прибавление к рабочему регистру второго слагаемого из Р2. Поле

5 режима адресации задает переход по адресу ветвления. На управляющий вход мультиплексора 1 поступает из РМК признак десятичной операции, по которому биты переноса С1, С2, СЗ, С4 через мультиплексор поступают на входы младших разрядов адреса БФА МК2. На входы старших разрядов адреса этого блока поступает код старшей части адреса из РМК4. Таким образом, происходит переход к МК, в поле константы которой записан соответствующий код коррекции. По этой МК код коррекции вычитается из содержимого рабочего регистра с записью результата, например в Р2. Происходит безусловный переход к МК, расположенной вслед за описанной второй МК.

Предложенное техническое решение позволяет существенно повысить быстродействие при выполнении десятичных операций по сравнению с известным, где для десятичного сложения требуется по меньшей мере 2+К МК, где К - число тетрад. Так, при К 4 быстродействие повышается вдвое, при К 7 - в три раза, и т.д.

Ф о р м у л а и з о б р ете н и я Арифметическое устройство с микропрограммным управлением, содержащее п/4 двоичных арифметико-логических блоков (п - разрядности информации), блок памяти микрокоманд, регистр микрокоманд, блок формирования адресов микрокоманд и первый мультиплексор, причем выход блока формирования адреса микрокоманд соединен с адресным входом блока памяти микрокоманд, выход которого соединен с входом регистра микрокоманд, выходы разрядов поля задания режима адресации которого соединены с входами разрядов задания режима блока формирования адресов микрокоманд, вход условия переходов которого соединен с выходом первого мультиплексора, разряды управляющего входа которого соединены с выходами разрядов поля задания вида переходов регистра микрокоманд, выходы разрядов поля задания константы которого соединены соответственно с разрядами первых информационных входов с первого по п/4 двоичных арифметико-логических блоков,

разряды вторых информационных входов которых соединены соответственно с разрядами информационного входа устройства, выходы разрядов которого соединены соответственно с выходами разрядов результата с первого по п/4 двоичных арифметике- логических блоков, выход переноса К-го (К 1 - п/4-1) двоичного арифметико-логического блока соединен с

входом переноса (К+1)-го двоичного арифметико-логического блока, выходы переноса знака признака, признака нуля и признака переполнения n/4-ro двоичного арифметико-логического блока соединены

соответственно с информационными входами первого мультиплексора, выходы разрядов поля задания вида операции регистра микрокоманд соединены с входами разрядов задания вида операции двоичных арифметико-логических блоков с первого по п/4, вход задания вида операции устройства соединен с установочным входом блока формирования адресов микрокоманд, выходы старших разрядов поля задания адреса регистра микрокоманд соединены с входами старших разрядов адреса блока формирования адресов микрокоманд, отличающееся тем, что, с целью повышения быстродействия, оно содержит второй мультиплексор, причем выходы переносов двоичных арифметико-логических блоков с первого по п/4 соединены соответственно с разрядами первого информационного входа второго мультиплексора, разряды второго информационного входа которого соединены соответственно с выходами младших разрядов поля задания адреса регистра микрокоманд, выход разряда признака десятичной операции которого соединен с управляющим входом второго мультиплексора, выходы разрядов которого соединены соответственно с входами младших разрядов адреса блока формирования адресов микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство с микропрограммным управлением | 1990 |

|

SU1797108A1 |

| Система для выполнения команд десятичной арифметики табличным способом | 1981 |

|

SU1027731A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство для обработки данных переменной длины | 1986 |

|

SU1675897A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении процессоров, выполняющих операции двоичной и десятичной арифметики. Целью изобретения является повышение быстродействия. Устройство содержит двоичные арифметико-логические блоки 8- 11, блок 3 памяти микрокоманд, регистр 4 микрокоманд, блок 2 формирования адресов микрокоманд, первый 1 и второй 6 мультиплексоры. 1 ил., 1 табл.

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Проектирование цифровых систем на комплектах микропрограммируемых БИС | |||

| Под ред | |||

| В.Г.Колесникова, М.: Радио и связь, 1984, с.179. | |||

Авторы

Даты

1992-04-07—Публикация

1989-12-14—Подача