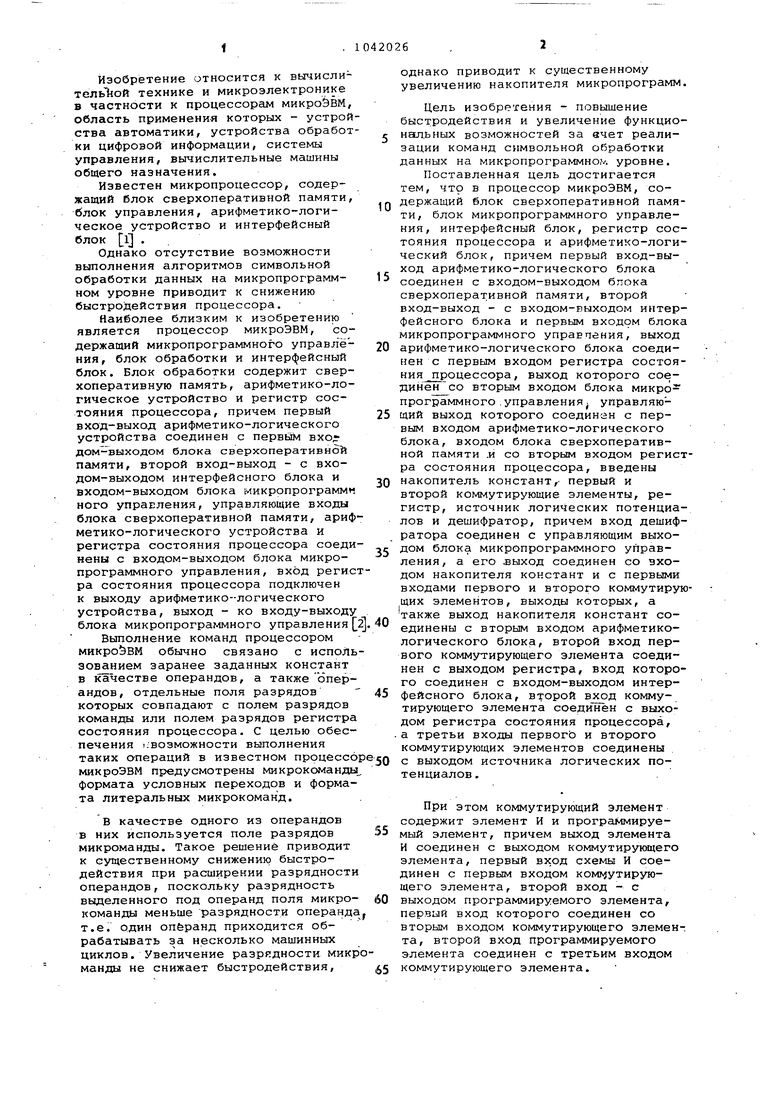

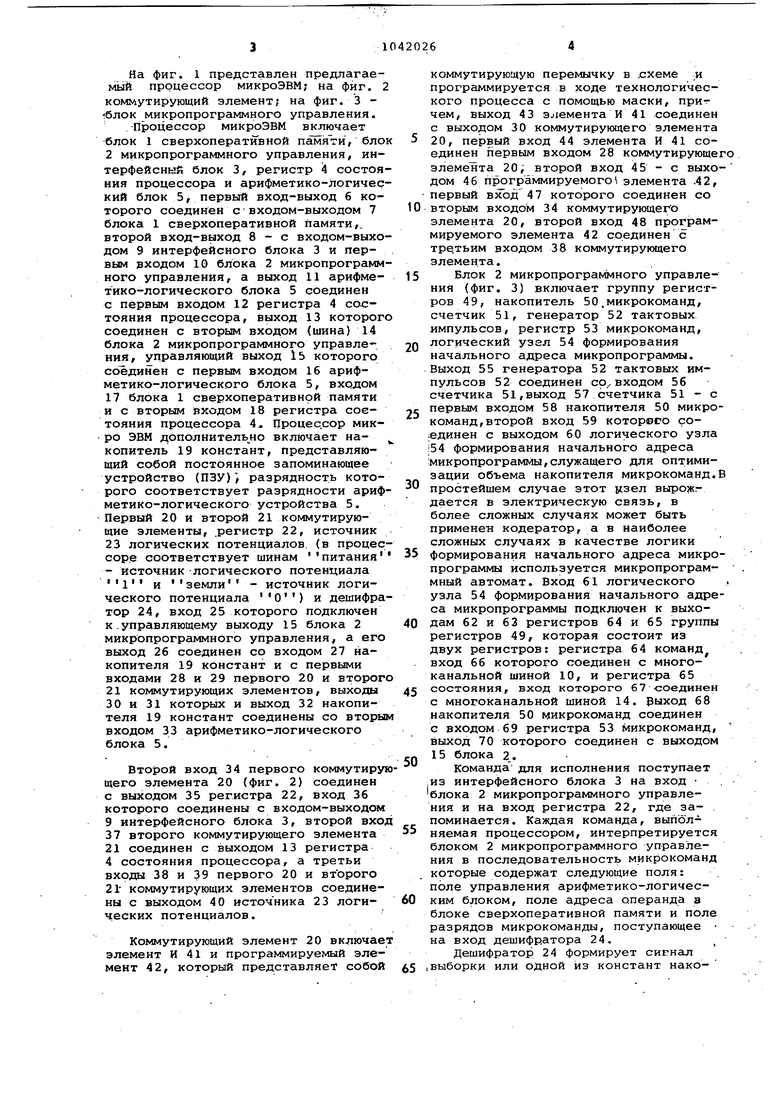

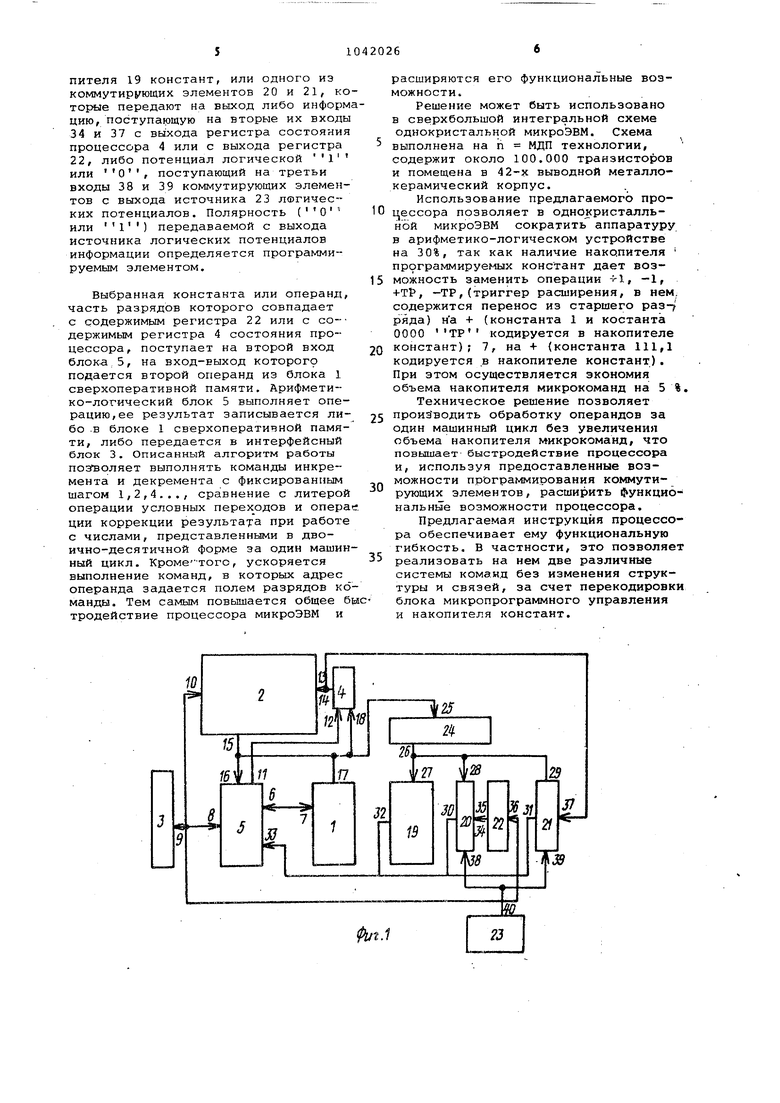

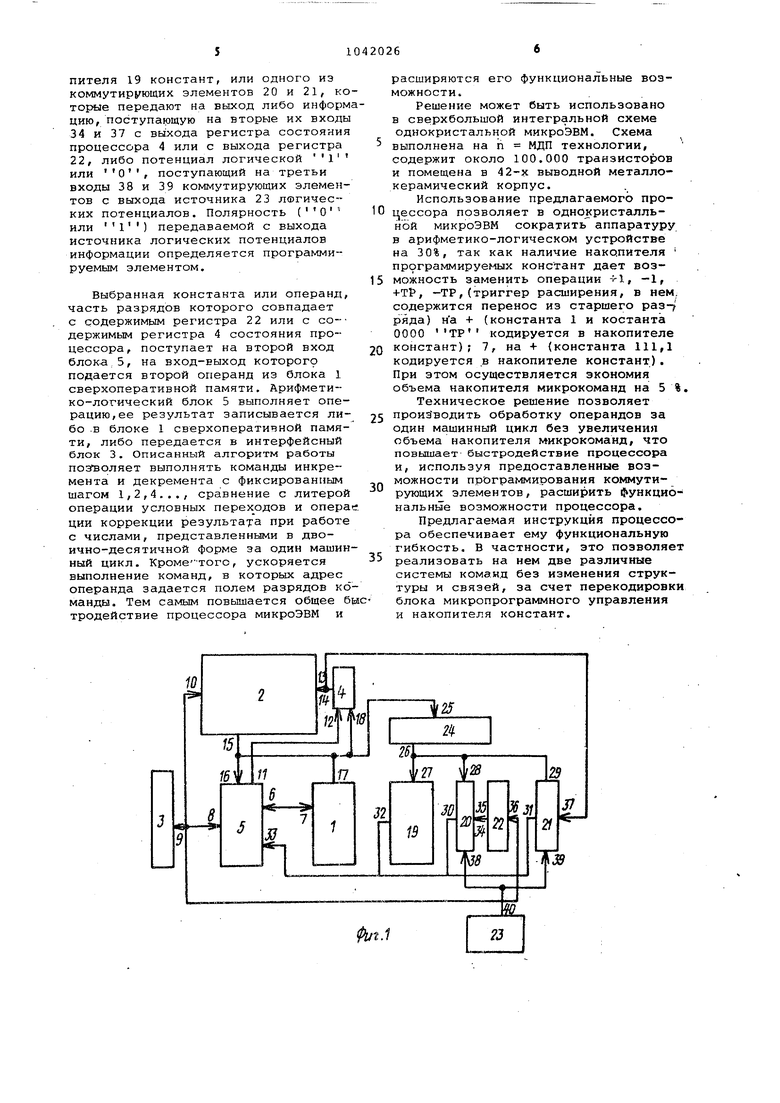

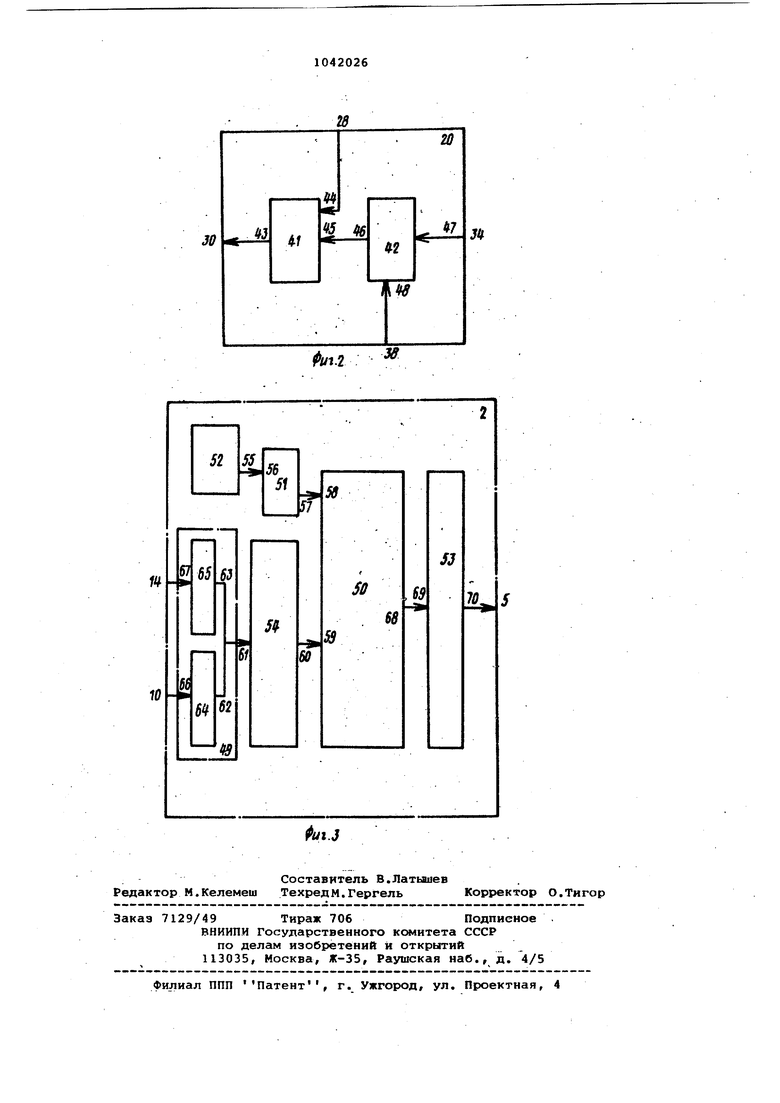

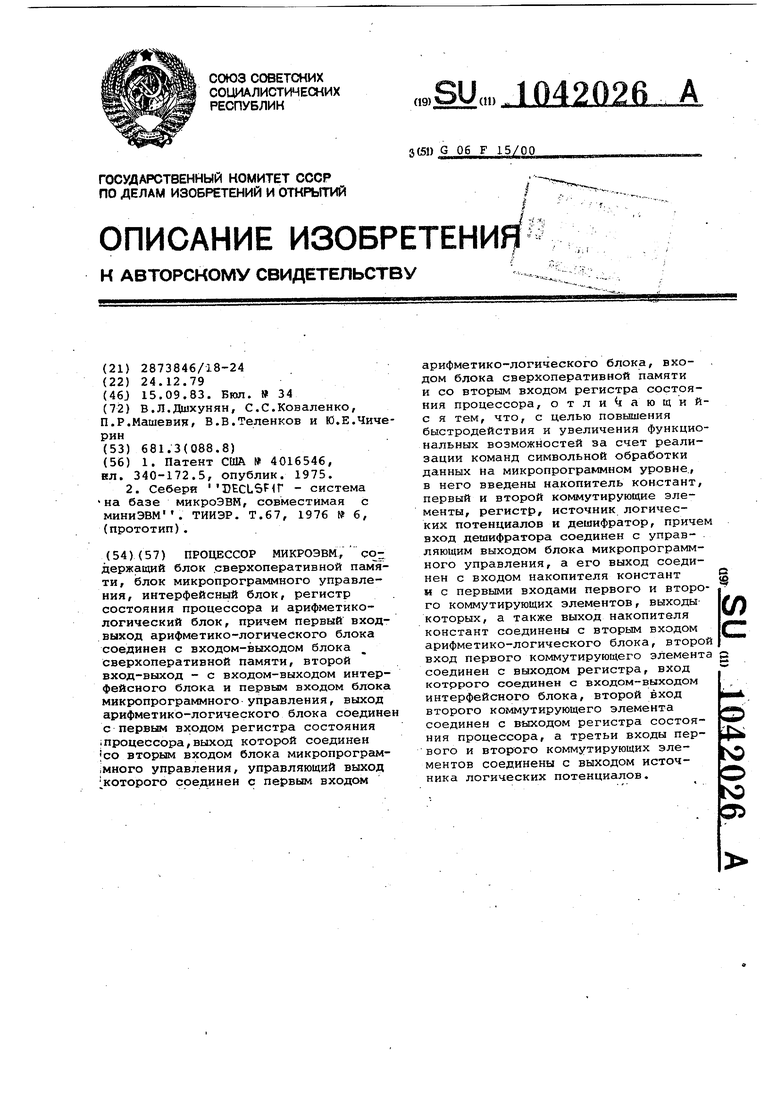

Изобретение относится к вычислиTcnbkoft технике и микроэлектронике в частности к процессорам микро&ВМ, область применения которых - устрой ства автоматики, устройства обработ ки цифровой информации, системы управления, вычислительные машины общего назначения. Известен микропроцессор, содержащий блок сверхоперативной памяти, блок управления, арифметико-логическое устройство и интерфейсный блок l . Однако отсутствие возможности выполнения алгоритмов символьной обработки данных на микропрограммном уровне приводит к снижению быстродействия процессора. Наиболее близким к изобретению является процессор микроэвм, содержащий микропрограммного управлёния, блок обработки и интерс ейсный блок. Блок обработки содержит сверхоперативную память, арифметико-логическое устройство и регистр состояния процессора, причем первый вход-выход арифметико-логического устройства соединен с первым входом-выходом блока сверхоперативно памяти, второй вход-выход - с входом-выходом интерфейсного блока и входом-выходом блока микропрограмма ного управления, управляющие входы блока сверхоперативной памяти, ариф метико-логического устройства и регистра состояния процессора соеди нены с входом-выходом блока микропрограммного управления, вход регис ра состояния процессора подключен к выходу арифметико-логического устройства, выход - ко входу-выходу блока микропрограммного управления Выполнение команд процессором микроэвм обычно связано с испол зованием заранее заданных констант в качестве операндов, а также операндов, отдельные поля разрядов которых совпадают с полем разрядов команды или полем разрядов регистра состояния процессора. С целью обеспечения возможности выполнения таких операций в известном процессб микроэвм предусмотрены микрокоманды формата условных переходов и формата литеральных микрокоманд. В качестве одного из операндов в них используется поле разрядов микроманды. Такое решение приводит к существенному снижению быстродействия при расширении разрядност операндов, поскольку разрядность выделенного под операнд поля микро команды меньше разрядности операнд т.е. один операнд приходится обрабатывать за несколько машинных циклов. Увеличение разрядности мик манды не снижает быстродействия, однако приводит к существенному увеличению накопителя микропрограмм. Цель изобретения - повышение быстродействия и увеличение функционашьных возможностей за ачет реализации команд символьной обработки данных на микpoпpoгpaммнo.. уровне. Поставленная цель достигается тем, что в процессор микроэвм, содержащий блок сверхоперативной памяти, блок микропрограммного управления, интерфейсный блок, регистр состояния процессора и арифметико-логический блок, причем первый вход-выход арифметико-логического блока соединен с входом-выходом бпока сверхоперативной памяти, второй вход-выход - с входом-выходом интерфейсного блока и первым входом блока микропрограммного управ пения, выход арифметико-логического блока соединен с первым входом регистра состояния процессора, выход которого соедине н со вторым входом блока микропрограммного .управления управляющий выход которого соединен с первым входом арифметико-логического блока, входом блока сверхоперативной памяти .и со вторым входом регистра состояния процессора, введены накопитель констант,- первый и второй коммутирующие элементы, регистр, источник логических потенциалов и дешифратор, причем вход дешифратора соединен с управляющим выходом блока микропрограммного управления, а его выход соединен со входом накопителя констант и с первыми входами первого и второго коммутирующих элементов, выходы которых, а также выход накопителя констант соединены с вторым входом арифметикологического блока, второй вход первого коммутирующего элемента соединен с выходом регистра, вход которого соединен с входом-выходом интерфейсного блока, второй вход коммутирующего элемента соедиТГен с выходом регистра состояния процессора, а третьи входы первого и второго коммутирующих элементов соединены с выходом источника логических потенциалов . При этом коммутирующий элемент содержит элемент И и програ Ф4ируемый элемент, причем выход элемента И соединен с выходом коммутирующего элемента, первый В5год схемы И соединен с первым входом ком утирующего элемента, второй вход - с выходом программируемого элемента, первый вход которого соединен со вторым входом коммутирующего элеменг та, второй вход программируемого элемента соединен с третьим входом коммутирующего элемента. На фиг. 1 представлен предлагае мый процессор микроэвм; на фиг. коммутирующий элемент; на фиг. 3 1блок микропрограммного управления. . -nipoueccop микроэвм включает блок 1 сверхоперативной , бло 2 микропрограммного управления, ин терфейсный блок 3, регистр 4 состоя ния процессора и арифметико-логичес кий блок 5, первый вход-выход 6 которого соединен с входом-выходом 7 блока 1 сверхоперативной памяти,, второй вход-выход 8 - с входом-выхо дом 9 интерфейсного блока 3 и первым рходом 10 блока 2 микропрограмм ного управления, а выход 11 арифметико-логического блока 5 соединен с первым входом 12 регистра 4 состояния процессора, выход 13 которог соединен с вторым входом (шина) 14 блока 2 микропрограммного управления, управляющий выход 15 которого со ёдинен с первым входом 16 арифметико-логического блока 5, входом 17 блока 1 сверхоперативной памяти и с вторым входом 18 регистра состояния процессора 4, Процессор микро ЭВМ дополнительно включает накопитель 19 констант, представляющий собой постоянное запоминающее устройство (ПЗУ)) разрядность которого соответствует разрядности ариф метико-логического устройства 5. Первый 20 и второй 21 коммутирующие элементы, .регистр 22, источник 23 логических потенциалов (в процес соре соответствует шинам питания - источник логического потенциала земли источник логического потенциала О) и дешифра тор 24, вход 25 которого подключен к.управляющему выходу 15 блока 2 микропрограммного управления, а его выход 26 соединен со входом 27 накопителя 19 констант и с первыми входами 28 и 29 первого 20 и второг 21 коммутирующих элементов, выходы 30 и 31 которых и выход 32 накопителя 19 констант соединены со вторы входом 33 арифметико-логического блока 5. Второй вход 34 первого коммутиру щего элемента 20 (фиг. 2) соединен с выходом 35 регистра 22, вход 36 которого соединены с входом-выходом 9 интерфейсного блока 3, второй вхо 37 второго коммутирующего элемента 21 соединен с выходом 13 регистра 4 состояния процессора, а третьи входы 38 и 39 первого 20 и второго 21 коммутирующих элементов соединены с выходом 40 источника 23 логических потенциалов. Коммутирующий элемент 20 включае элемент И 41 и программируемый элемент 42, который представляет собой коммутирующую перемычку в схеме и программируется в ходе технологического процесса с помощью маски, прит чем, выход 43 э 1емента И 41 соединен с выходом 30 коммутирующего элемента 20, первый вход 44 элемента И 41 соединен первым входом 28 коммутирующего элемента 20; второй вход 45 - с выходом 46 программируемого элемента .42, первый вход 47 которого соединен со вторым входом 34 коммутирующего элемента 20, второй вход 48 программируемого элемента 42 соединен с тре.тьим входом 38 коммутирующего элемента. Блок 2 микропрограммного управления (фиг. 3) включает группу регистров 49, накопитель 50.микрокоманд, счетчик 51, генератор 52 тактовых импульсов, регистр 53 микрокоманд, логический узел 54 формирования начального адреса микропрограммы. Выход 55 генератора 52 тактовых импульсов 52 соединен ср входом 56 счетчика 51,выход 57 счетчика 51 - с первым входом 58 накопителя 50 микрокоманд, второй вход 59 которого соединен с выходом 60 логического узла :54 формирования начального адреса микропрограммы,служащего для оптимизации объема накопителя микрокоманд.В простейшем случае этот цзел вырождается в электрическую связь, в более сложных случаях может быть применен кодератор, а в наиболее сложных случаях в качестве логики формирования начального адреса микропрограммы используется микропрограммный автомат. Вход 61 логического . узла 54 формирования начального адреса микропрограммы подключен к выходам 62 и 63 регистров 64 и 65 группы регистров 49, которая состоит из двух регистров: регистра 64 команд вход 66 которого соединен с многоканальной шиной 10, и регистра 65 состояния, вход которого 67 -cbeAHHeH с многоканальной шиной 14. Выход 68 накопителя 50 микрокоманд соединен с входом 69 регистра 53 микрокоманд, выход 70 которого соединен с выходом 15 блока 2. Команда для исполнения поступает ;из интерфейсного блока 3 на вход . блока 2 микропрограммного управления и на вход регистра 22, где запоминается. Каждая команда, выполняемая процессором, интерпретируется блоком 2 микропрограммного управления в последовательность микрокоманд которые содержат следующие поля: поле управления арифметико-логическим блоком, поле адреса операнда в блоке сверхоперативной памяти и поле разрядов микрокоманды, поступающее на вход дешифратора 24. Дешифратор 24 формирует сигнал выборки или одной из констант накопителя 19 констант, или одного иэ коммутирующих элементов 20 и 21, ко торые передают на выход либо информ цию, поступающую на вторые их входы 34 и 37 с выхода регистра состояни процессора 4 или с выхода регистре 22, либо потенциал логической поступающий на третьи входы 38 и 39 коммутирующих элементов с выхода источника 23 логических потенциалов . Полярность ( О или ) передаваемой с выхода источника логических потенциалов информации определяется программируемым элементом. Выбранная константа или операнд часть разрядов которого совпадает с содержимым регистра 22 или с содержимым регистра 4 состояния процессора, поступает на второй вход блока 5, на вход-выход которого подается второй операнд из блока 1 сверхоперативной памяти. Арифметико-логический блок 5 выполняет операцию,ее результат записывается либо в блоке 1 сверхоперативной памяти, либо передается в интерфейсный блок 3. Описанный алгоритм работы поэгволяет выполнять команды инкремента и декремента с фиксированпьлм шагом 1,2,4.,., сравнение с литерой операции условных переходов и опера дни коррекции результата при работе с числами, представленными в двоично-десятичной форме за один машин ный цикл, Кроме-того, ускоряется выполнение команд, в которых адрес операнда задается полем разрядов ко манды. Тем самым повышается общее б тродействие процессора микроэвм и расширяются его функциональные возможности. Решение может быть использовано в све|рхбольшой интегральной схеме однокристальной микроэвм. Схема выполнена на п МДП технологии, содержит около 100,000 транзисторов и помещена в 42-х выводной металлокерамический корпус. Использование предлагаемого проi eccopa позволяет в однокристалльной микроэвм сократить аппаратуру в арифметико-логическом устройстве на 30%, так как наличие накопителя программируемых констант дает возможность заменить операции -5-1, -1, +Т1, -ТР, (триггер расширения, в нем содержится перенос из старшего раэ-7 (константа 1 и костанта ряда) на + 0000 ТР кодируется в накопителе констант); 7, на + (константа 111,1 кодируется в накопителе констант). При этом осуществляется экономия объема накопителя микрокоманд на 5 %. Техническое решение позволяет производить обработку операндов за один машинный цикл без увеличения объема накопителя микрокоманд, что повышает быстродействие процессора и, используя предоставленные возможности программирования коммутирующих элементов, расширить б ункци6нальные возможности процессора. Предлагаемая инструкция процессора обеспечивает ему функциональную гибкость. В частности, это позволяет реализовать на нем две различные системы команд без изменения структуры и связей, за счет перекодировки блока микропрограммного управления и накопителя констант.

30

J«

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор | 1976 |

|

SU670935A1 |

| Операционное устройство микропроцессорной вычислительной системы | 1982 |

|

SU1198532A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559341A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Процессор | 1974 |

|

SU526902A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ | 1994 |

|

RU2079877C1 |

ПРОЦЕССОР МИКРОЭВМ, содержащий блок .сверхоперативной памяти, блок микропрограммного управления, интерфейсный блок, регистр состояния процессора и арифметикологический блок, причем первый входвыход арифметико-логического блока соединен с входом-выходом блока сверхоперативной памяти, второй вход-выход - с входом-выходом интерфейсного блока и первым входом блока микропрограммного управления, выход арифметико-логического блока соединен с первым входом регистра состояния iпроцессора,выход которой соединен |со вторым входом блока микропрограмiMHoro управления, управляющий выход ; которого соединен с первым входом арифметико-логического блока, входом блока сверхоперативной памяти и со вторым входом регистра состояния процессора, о т л и i а ю щ и йс я тем, что, с целью повышения быстродействия и увеличения функциональных возможностей за счет реализации команд символьной обработки данных На микропрограммном уровне., в него введены накопитель констант, первый и второй коммутирующие элементы, регистр, источник логических потенциалов и дешифратор, причем вход дешифратора соединен с управляющим выходом блока микропрограммного управления, а его выход соедиI нен с входом накопителя констант и с первыми входами первого и второ(Л G го коммутирующих элементов, выходы которых, а также выход накопителя констант соединены с вторым входом арифметико-логического блока, второй вход первого коммутирующего элемента соединен с выходом регистра, вход котррого соединен с вкодом-выходом интерфейсного блока, второй вход второго коммутирующего элемента соединен с выходом регистра состояния процессора, а третьи входы первого и второго коммутирующих элементов соединены с выходом источника логических потенциалов.

rt/1.2

55

56 5f

58

sr

W

Я

5S

6/

60

69

ID,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4016546, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Себери DECLSFif - система на базе микроэвм, совместимая с миниЭВМ | |||

| ТИИЭР | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

Авторы

Даты

1983-09-15—Публикация

1979-12-24—Подача