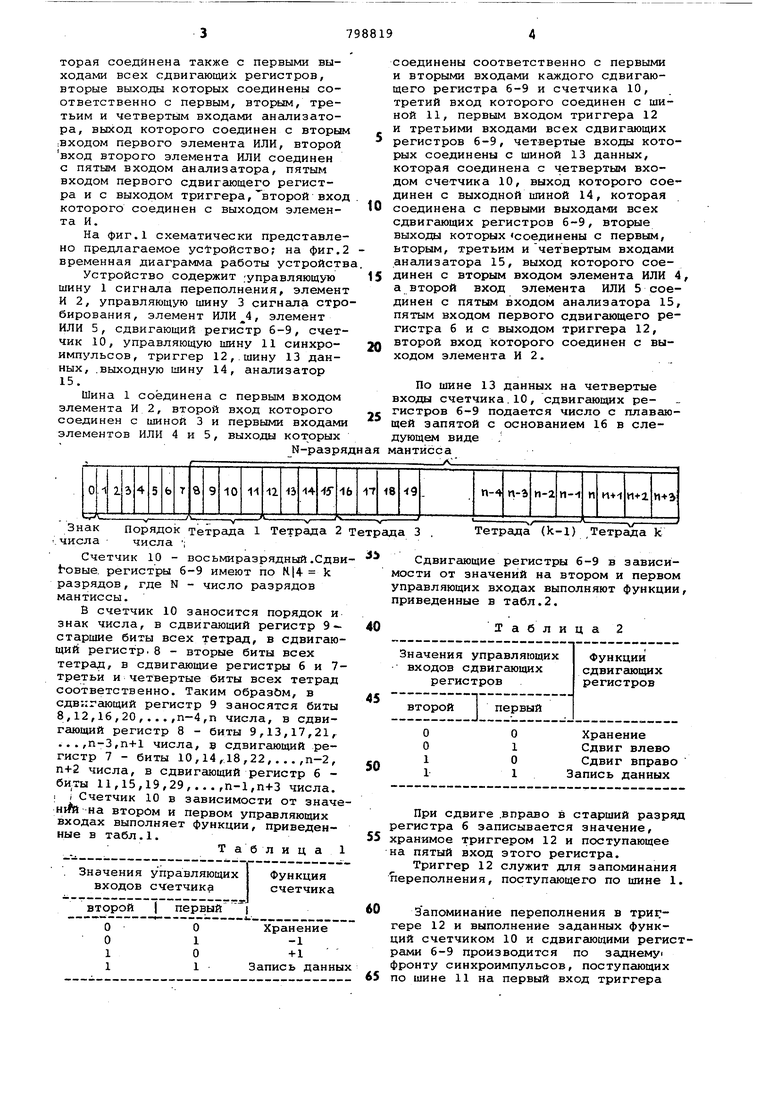

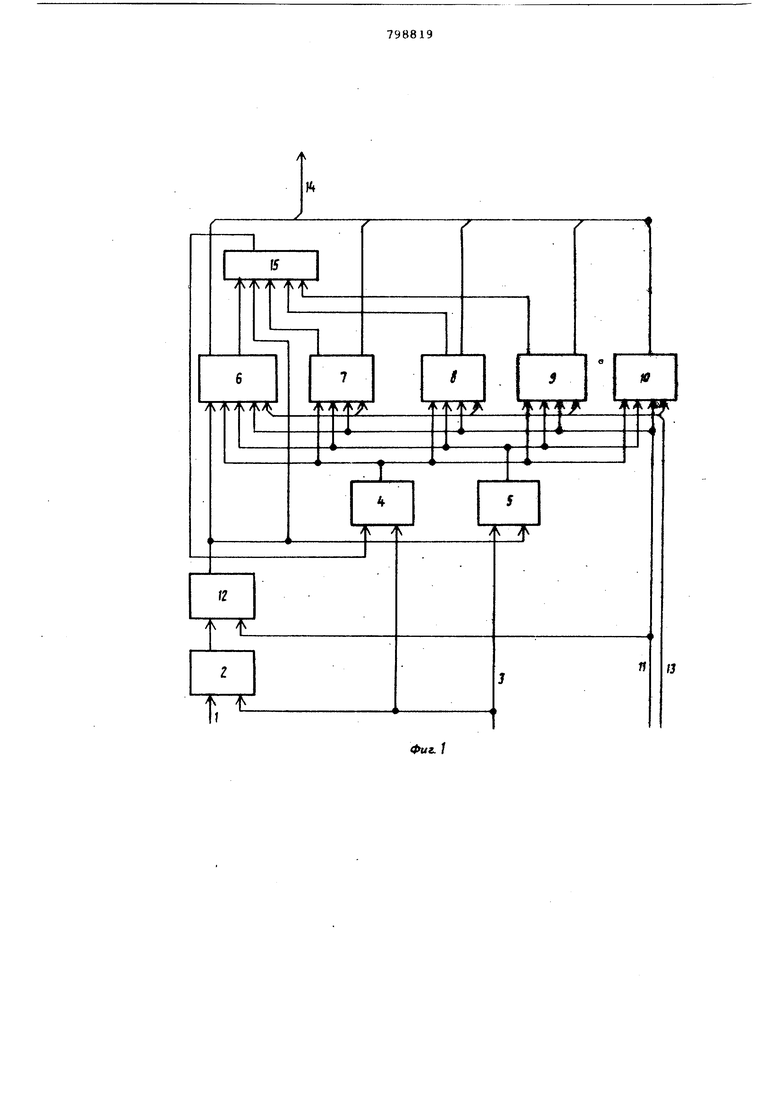

Изобретение относится к вычислительной технике и может быть использовано для нормализации чисел с пла.рающей запятой с основанием 16, как операндов, так и результата. Известны устройства для нормализации чисел, подразумевающие сдвиг мантиссы числа влево до появления в старшем бите и одновременное уменьшение порядка числа на количёст во сдвигов или сдвиг числа вправо . на , разряд с одновременным увеличением порядка числа на i ц« при переполнении разрядной сетки арифметического устройства в операциях над мантиссами, в ЦВМ третьего поколения числа с плавающей запятой имеют основание 16 и соответственно должны сдвигаться на тетрады (4 разряда) вправо и влево с корректировкой порядка на tl при каждом сдвиге 1, 2 и 3. Известно устройство для нормализации чисел/ имеющее входные шины, m анализаторов и выходные шины «ГГ.Недостатком указанного устройства является большой.объем оборудования отсутствие возможности работы с числами с плавающей.запятой по основанию 16, отсутствие возможности нормализации числа вправо при переполнении разрядной сетки арифметического устройства. Цель изобретения - экономия оборудования и расширение функциональных возможностей устройства, заключающиеся в возможности нормализации числа вправо. Поставленная цель достигается тем, что устройство для нормализации чисел, содержащее анализатор, шину данных, выходную шину, содержит четыре сдвигающих регистра, счетчик, элемент И, два элемента ИЛИ, триггер, управляющие шины, причем первая управляющая шина соединена с первым входом элемента И, второй :вхрд которого соединен с второй управляющей шиной и первыми входами элементов ИЛИ, выходы которых соединены соответственно с первыми и вторыми входами каждого сдвигающего регистра и счетчика, третий вход которого соединен с третьей управляющей шиной, первым входом триггера и третьими входами всех сдвигающих регистров, четвертые входы которых соединены с шиной данных, которая соединена с четвертым входом счетчика, выход которого соединен с выходной шиной, которая соединена также с первыми выходами всех сдвигающих регистров, вторые выходы которых соединены соответственно с первым, вторым, третьим и четвертым входами анализатора, выход которого соединен с вторым 1ВХОДОМ первого элемента ИЛИ, второй вход второго элемента ИЛИ соединен с пятым входом анализатора, пятым входом первого сдвигающего регистра и с выходом триггера, второй вход которого соединен с выходом элемента И. На фиг.1 схематически представлено предлагаемое устройство на фиг.2 временная диаграмма работы устройств Устройство содержит управляющую шину 1 сигнала переполнения, элемент И 2, управляющую шину 3 сигнала стро бирования, элемент , элемент ИЛИ 5, сдвигающий регистр 6-9, счетчик 10, управляющую шину 11 синхроимпульсов, триггер 12,.шину 13 данных, выходную шину 14, анализатор 15. Шина 1 соединена с первым входом элемента И 2, второй вход которого соединен с шиной 3 и первыми входами элементов ИЛИ 4 и 5, выходы которых N-разря соединены соответственно с первыми и вторыми входами каждого сдвигающего регистра 6-9 и счетчика 10, третий вход которого соединен с шиной 11, первым входом триггера 12 и третьими входаг ш всех сдвигающих регистров 6-9, четвертые входы которых соединены с шиной 13 данных, которая соединена с четвертым входом счетчика 10, выход которого соединен с выходной шиной 14, которая соединена с первыми выходают всех сдвигающих регистров 6-9, вторые выходы которых «соединены с первьам, вторым, третьим ичетвертым входами анализатора 15, выход которого соединен с вторым входом элемента ИЛИ 4, а второй вход элемента ИЛИ 5 соединен с пятым входом анализатора 15, пятым входом первого сдвигающего регистра бис выходом триггера 12, второй вход которого соединен с выходом элемента И 2. По шине 13 данных на четвертые входы счетчика.10, сдвигающих регистров 6-9 подается число с плавающей запятой с основанием 16 в следующем виде мантисса /С1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для нормализации чисел | 1986 |

|

SU1388849A1 |

| Устройство для нормализации чисел | 1986 |

|

SU1345189A2 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1985 |

|

SU1287144A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для преобразования двоичного кода в десятичный и обратно для чисел с плавающей запятой | 1977 |

|

SU717755A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

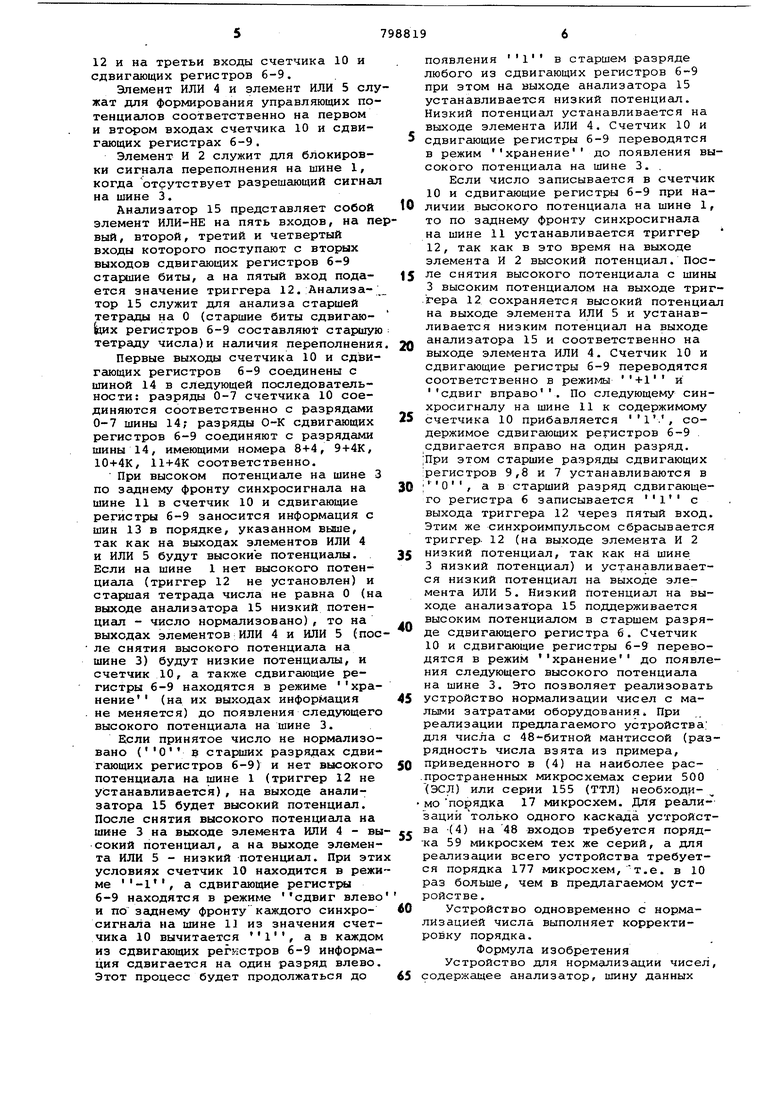

Знак порядок Тетрада 1 Тетрада 2 ч числа числа ; Счетчик 10 - восьмиразрядный.Сдви oвыe. регистры 6-9 имеют по Н|4- k разрядов, где N - число разрядов мантиссы. В счетчик 10 заносится порядок и знак числа, в сдвигающий регистр 9- старшие биты всех тетрад, в сдвигающий регистр.8 - вторые биты всех тетрад, в сдвигающие регистры 6 и 7третьи и четвертые биты всех тетрад соответственно. Таким образйм, в сдвигающий регистр 9 заносятся биты 8,12,16,20,...,п-4,п числа, в сдвигающий регистр 8 - биты 9,13,17,21, ...,п-3,п+1 числа, в сдвигающий регистр 7 - биты 10,14,18,22,...,п-2, п+2 числа, в сдвигающий регистр б биты 11,15,19,29,...,п-1,п+3 числа. ; i Счетчик 10 в зависимости от значе Hilft на втором и первом управляющих входах выполняет функции, приведенные в табл.1. Таблица Тетрада (k-l) Тетрада k а 3 Сдвигающие регистры 6-9 в зависимости от значений на втором и первом управляющих входах выполняют функции, приведенные в табл.2. Таблица 2 Значения управляющих Функции входов сдвигающих сдвигающих регистров регистров второй первый При сдвиге .вправо в старший разряд регистра 6 записывается значение, хранимое триггером 12 и поступающее на пятый вход этого регистра. Триггер 12 служит для запоминания переполнения, поступающего по шине 1. Запоминание переполнения в триггере 12 и выполнение заданных функций счетчиком 10 и сдвигающими регистрами 6-9 производится по заднему фронту синхроимпульсов, поступающих по шине 11 на первый вход триггера

12 и на третьи входы счетчика 10 и сдвигающих регистров 6-9.

Элемент ИЛИ 4 и элемент ИЛИ 5 служат для формирования управляющих потенциалов соответственно на первом и входах счетчика 10 и сдвигающих регистрах 6-9.

Элемент И 2 служит для блокировки сигнала переполнения на шине 1, когда отсутствует разрешающий сигнал на шине 3.

Анализатор 15 представляет собой элемент ИЛИ-НЕ на пять входов, на певый, второй, третий и четвертый входы которого поступают с вторых выходов сдвигающих регистров 6-9 стариие биты, а на пятый вход подается значение триггера 12. Анашиза- тор 15 служит для анализа старшей тетрады на О (старшие биты сдвигаюиих регистров 6-9 составляют ста Х11ую тетраду числа)и наличия переполнения

Первые выходы счетчика 10 и сдвигающих регистров 6-9 соединены с шиной 14 в следующей последовательности: разряды 0-7 счетчика 10 соединяются соответственно с разрядами 0-7 шины 14; разряды О-К сдвигающих регистров 6-9 соединяют с разрядами шины 14, имеющими номера 8+4, 9+4К, 10+4К, 11+4К соответственно.

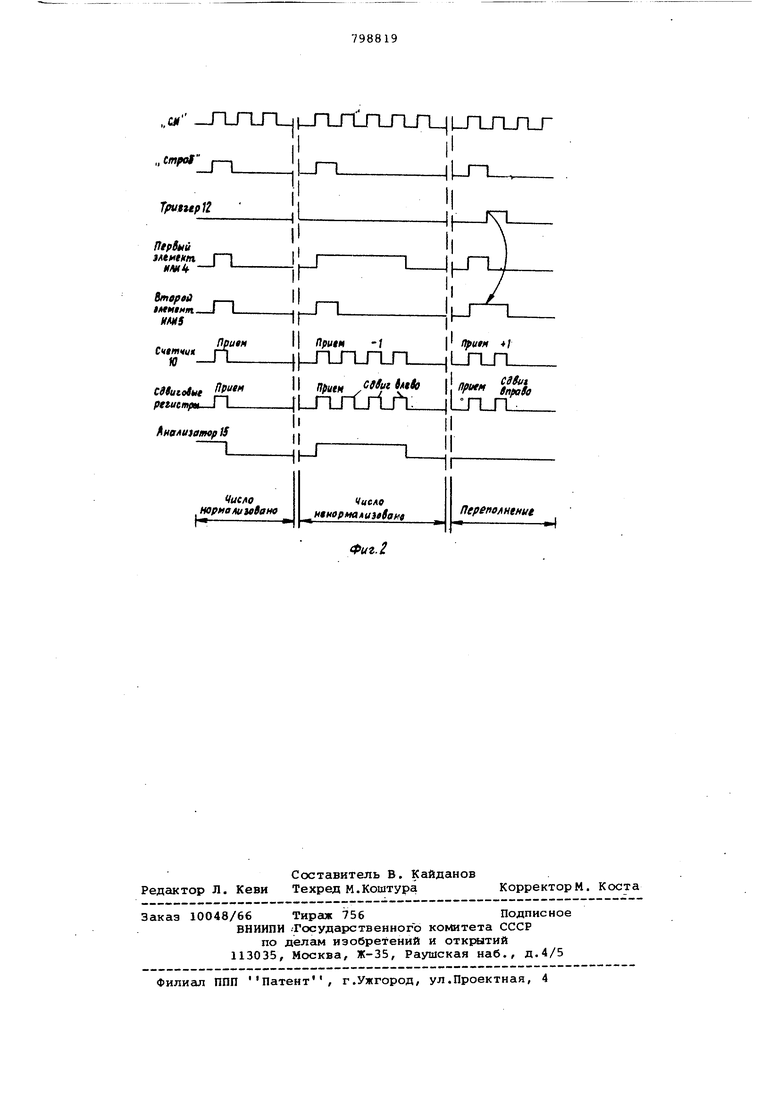

При высоком потенциале на шине 3 по заднему фронту синхросигнала на шине 11 в счетчик 10 и сдвигающие регистры 6-9 заносится информация с шин 13 в порядке, указанном выше, так как на выходах элементов ИЛИ 4 и ИЛИ 5 будут высокие потенциалы. Если на шине 1 нет высокого потенциала (триггер 12 не установлен) и старная тетрада числа не равна О (на выходе анализатора 15 низкий потенцисш - число нормализовано), то на выходах элементов ИЛИ 4 и ИЛИ 5 (после снятия высокого потенциала на шине 3) будут низкие потенциалы, и счетчик 10, а также сдвигающие регистры 6-9 находятся в режиме хранение (на их выходах информация не меняется) до появления следующего высокого потенциала на шине 3.

Если принятое число не нормализовано (О в старших разрядах сдвигсиощих регистров 6-9) и нет высокого потенциала на шине 1 (триггер 12 не устанавливается), на выходе анализатора 15 будет высокий потенциаш. После снятия высокого потенциала на шине 3 на выходе элемента ИЛИ 4 - вы сокий потенциал, а на выходе элемента ИЛИ 5 - низкий потенцисш. При эти условиях счетчик 10 находится в режиме , а сдвигающие регистры 6-9 находятся в режиме сдвиг влево и по Зс1днему фронту каждого синхросигнала на шине 11 из значения счетчика 10 вычитается , а в каждом из сдвигающих регистров 6-9 информация сдвигается на один разряд влево. Этот процесс будет продолжаться до

появления 1 в старшем разряде любого из сдвигающих регистров 6-9 при этом на выходе анализатора 15 устанавливается низкий потенциал. Низкий потенциал устанавливается на выходе элемента ИЛИ 4. Счетчик 10 и сдвигающие регистры 6-9 переводятся в режим хранение до появления высокого потенциала на шине 3. ,

Если число записывается в счетчик 10 и сдвигающие регистры 6-9 при наличии высокого потенциала на шине 1 то по заднему фронту синхросигнала на шине 11 устанавливается триггер 12, так как в это время на выходе элемента И 2 высокий потенциал. После снятия высокого потенциала с шины 3 высоким потенциалом на выходе триггера 12 сохраняется высокий потенциа на выходе элемента ИЛИ 5 и устанавливается низким потенцисШ на выходе анализатора 15 и соответственно на выходе элемента ИЛИ 4. Счетчик 10 и сдвигающие регистры 6-9 переводятся соответственно в режиг/ы и сдвиг вправо . По следующему синхросигналу на шине 11 к содержимому счетчика 10 прибавляется ., содержимое сдвигающих регистров 6-9 сдвигается вправо на один разряд. ;При этом старшие разряды сдвигающих :регистров 9,8 и 7 устанавливаются в :0, а в старший разряд сдвигающего регистра 6 записывается i с выхода триггера 12 через пятый вход. Этим же синхроимпульсом сбрасывается триггер. 12 (на выходе элемента И 2 низкий потенциал, так как на шине 3 низкий потенциал) и устанавливается низкий потенциал на выходе элемента ИЛИ 5. Низкий потенциал на выходе анализатора 15 поддерживается высоким потенциалом в старшем разряде сдвигающего регистра 6. Счетчик 10 и сдвигающие регистры 6-9 переводятся в режим хранение до появления следующего высокого потенциала на шине 3. Это позволяет реализовать устройство нормализации чисел с малыми затратами оборудования. При реализации предлагаемого устройства. для числа с 48-битной мантиссой (разрядность числа взята из примера, приведенного в (4) на наиболее рас.пространенных микросхемах серии 500 (ЭСЛ) или серии 155 (ТТЛ) необходимо порядка 17 микросхем. Для реализаций только одного каскада устройства -(4) на 48 входов требуется порядка 59 микросхем тех же серий, а для реализации всего устройства требуется порядка 177 микросхем, т.е. в 10 раз больше, чем в предлагаемом устройстве .

Устройство одновременно с нормализацией числа выполняет корректировку порядка.

Формула изобретения Устройство для нормализации чисел содержащее анализатор, шину данных

и выходную шину, отличающееся тем, что, с целью экономии оборудования и расширения функциональных возможностей, заключающегося в возможности нормализации числа вправо, оно содержит четыре сдвигающих регистра, счетчик, элемент И, два элемента ИЛИ, триггер, управляющие шины,-причем первая управляющая шина соединена с первым входом элемента И, второй вход 1 оторого соединен с второй управляющей шиной и пёрвьвиш входами элементов ИЛИ, выходы Ьсоторых соединены соответственно с первыми и вторыми входами каждого сдвигающего регистра и счетчика, третий вход которого соединен с третьей управляющей шиной, первым входом триггера и третьими входг1ми всех сдвигающих регистров, четвертые входы которах соединены с шиной данных, которая соединена с четвертым входом счетчи1 а, выход которого соединен с выходной, шиной, которая соединена также с первыми выходами всех сдвигающих регистров, вторые выходы которых соединены соответственно, с первым, вторым, третьим и четвертым входами аиёшизатора, выход которого соединен с вторым входом первого элемента ИЛИ, второй вход второго , элемента ИЛИ соединен с пятым входом анализатора, пятым входом первого сдвигающего регистра и с выходом триггера, второй вход которого соединен с выходом элемента И.

0 Источники информации,

принятые во внимание при экспертизе 1. Карцев М.А. Арифметика цифровых машин, М., Наука, 1969, с. 323-326.

0 системы. И., Энергия, 1973, с. 65-66.

(прототип). .

Авторы

Даты

1981-01-23—Публикация

1978-12-25—Подача