(54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1979 |

|

SU798821A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Устройство для вычисления функций | 1978 |

|

SU748418A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Арифметическое устройство | 1981 |

|

SU1012240A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1254506A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Конвейерное вычислительное устройство | 1987 |

|

SU1432512A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

1

Изобретение относится к цифровой вычислительной технике и может применяться в цифровых вычислительных лашинах для вычисления элементарных функций.

Известны арифметические устройства, работающие с информацией, представленной в виде векторов, предназначенные для решения задач, содержащих элементарные функции и содержащие регистры, блоки сдвига, сумматоры 1 и 2 .

Недостаток устройств - низкое быстродействие при вычислении функций

., sin arctg /X и arctg(/x, где х,| - аргументы, f , fy - значения функций.

Наиболее близким по технической сущности к предлагаемому является арифметическое устройство, содержа-щее первый, второй, третий и четвертый регистры, блок сдвига, сумматор, причем выходы первого и второго регистров подключены к первому и второму входам блока сдвига, соответственно, первый, вторые, третьи и четвертые входы сумматора подключены соответственно, к выходам первого, второго, четвертого регистров и к выходу блока сдвига, выход сумматора подключен к первым входам второго, третьего и четвертого регистров, со- . ответственно, выходы третьего регистра подключены ко входу первого регистра.

Известное устройство реализует алгоритм

..

М)

.,

где ,1,...,п-1, п - разрядность устройства; , м, в - значения координат и угла вектора на i-ой итерации;. -6. 1, 1 5 - функция, показывающая направление вращения векто0ра, d - угловая постоянная, равная arctg2-

Известное устройство вычисляет значения функций arctgv/x и f.cos arctgv/x в два этапа.

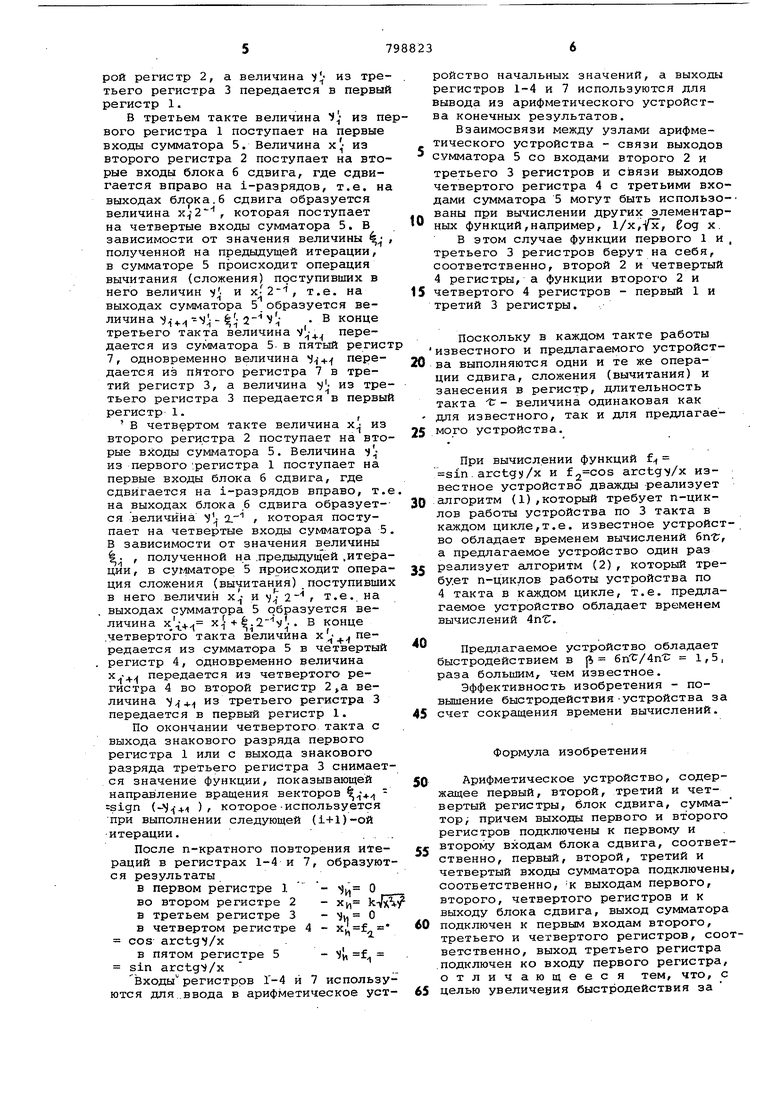

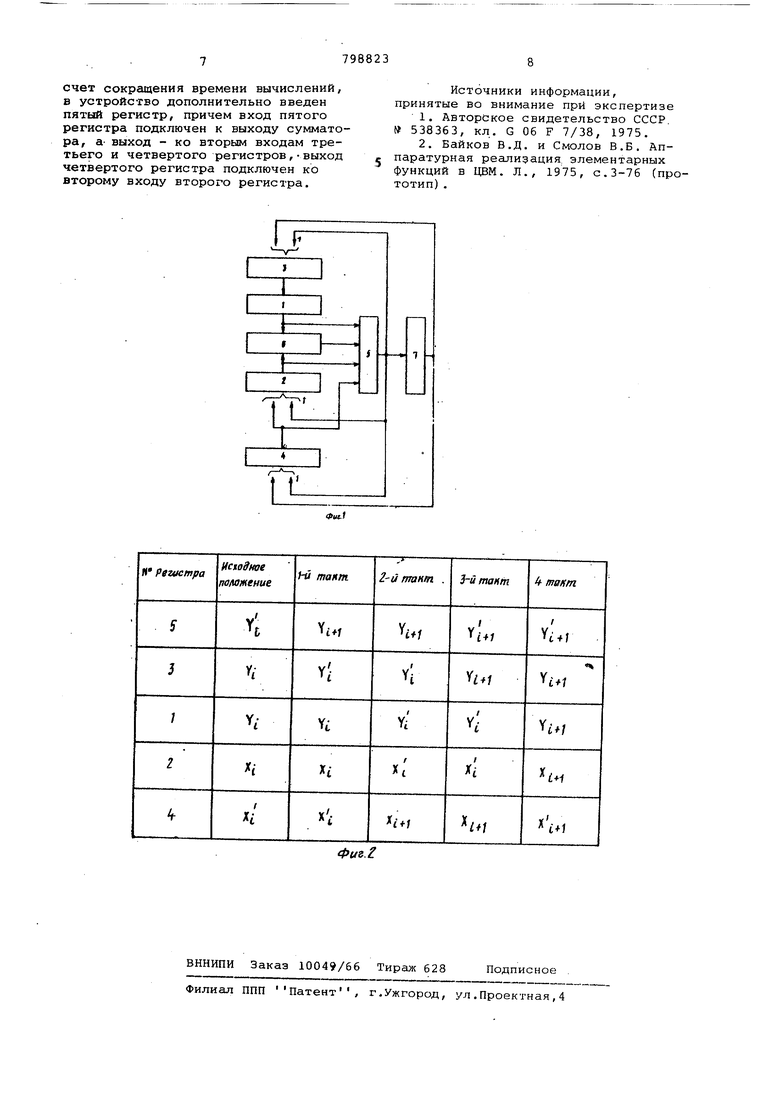

На первом этапе выражения (1) реализуются с начальными условиями X(j X, Vo V, BO -в, с выбором направления вращения вектора по закону sign (-V-I ) и с конечными результатами + N, Мм-0, ви arctgy/x, где k Н-vC-1+2 ) постоянный коэффициент удлинения вектора. На втором этапе выражения (1) реа лизуются с начальными условиями , Vo-o, ®о arctgy/x с выбором направления вращения вектора по закону sign 0 и с конечными результатами ху, fа cos arctgs/x, ,и f sin arctgv/K, ©„ О 2. Недостаток устройства - низкое быстродействие, ограниченное последовательным характером выполнения этапов вычислений о Цель изобретения - увеличение быстродействия арифметического устройства. Поставленная цель достигается тем что в устройство, содержащее перйый второй, третий и четвертый регистры блок сдвига, сумматор, причем выходы первого и второго регистров подключены к первому и второму входам блок сдвига, соответственно, первые, вто рые , третьи и четвертые входы сумматора подключены, соответственно, к выходам первого, второго, четвертого регистров и к выходу блока сдвига, выход сумматора подключен к первым входам второго, третьего и четвертого регистров, соответственно, выход третьего регистра подключен в входу первого регистра, дополнительно введен пятый регистр, причем вход пятого регистра подключен к выходу сумматора, а выход - ко вторым входам третьего и четвертого регистров выход четвертого регистра подключен ко второму входу второго регистра. .На фиг,1 представлена структурная схема арифметического устройства; на фиг,2 - временная диаграмма перемены содержимого регистров на i-ой итерации. Устройство содержит первый 1, вто рой 2, третий 3 и четвертый 4 регист ры, сумматор 5 блока 6 сдвига, регистр 7. Входы и выходы регистров 1-4 являются соответствующими входагли и вы ходами устройства. Устройство реализует алгоритм ., Х.,,,-, ,,,, ., где i 0,1,...,п-1, п - разрядность устройства, ,Vi и х , vj,- значения координат, соответственно, первого и второго вектора на 1-ой итер ции, , е --f,+-1 - функция,-.показыв ющая направление вращения векторов. Предлагаемое устройство вычисляе значения функций f sin arctg /x и ff2 cos arctgv/x в один этап путем реализации выражений (2) с начальны ми условиями Хс X, Уо 1 г Хо 1/k, о с выбором направления вращения векторов по закону - sign (-V-f ) и с конечными результатами Xj , arctg y x, )и f-i sin arctgv/x,гдe k . постоянный коэффициент удлинения вектора . Выходы пятого регистра 7 подключены ко входам третьего регистра 3, Тогда первый регистр 1 предназначен для хранения величины V-j , первоначально равной ii , второй регистр 2 предназначен для хранения величины , первоначально равной х, третий регистр 3 предназначен для хранения величины , первоначально равной N , четвертый регистр 4 предназначен для хранения величины , первоначально равной 1/k, пятый регистр 7 предназначен для хранения величины , первоначально равной 0. Устройство работает циклически. Каждая итерация состоит из четырех тактов. В каждом такте выполняются операции сдвига,сложения (вычитания) и занесения в регистр. Устройство работает следующим образом на i-ой итерации. В первом такте величина V-f из первого регистра 1 поступает на первые входы сумматора 5. Величина из второго регистра 2 поступает на вторые входы блока б сдвига, где сдвигается вправо на i-разрядов, т.е. на выходах блрка б сдвига образуется величина х , которая поступает на четвертые входы сумматора 5. В зависимости от значения величины - , полученной на предыдущей итерации, в сумматоре.5 происходит операция сложения (вычитания).поступивших в него величин 4 и , т.е. на выходах сумматора 5 образуется величина-ч -- + - 2-Х.|. В конце первого такта величина N передается из сумматора 5 в пятый регистр 7, одновременно величина передается из пятого регистра 7 в третий регистр 3, а величина из третьего регистра 3 передается в первый регистр 1. Во втором такте величина из второго регистра 2 поступает на вторые входы сумматора 5. Величина из первого регистра 1 поступает на первые входы блока 6 сдвига, где сдвигается на i-разрядов вправо, т.е. на выходах блока б сдвига образуется величина , которая поступает на четвертые .входы сумматора 5. В зависимости от значения величины Ц, полученной на предыдущей итерации, в сумматоре 5 происходит операция вычитания (сложения) поступивших в него величин и - l- , т.е. на выходах сумматора 5 образуется величина , 2v . В конце второго такта величина х. передается из сумматора 5 в четвертый регистр 4, одновременно величина передается из четвертого регистра 4 во второй регистр 2, а величина из третьего регистра 3 передается в первый регистр 1. В третьем такте величина i из пе вого регистра 1 поступает на первые входы сумматора 5. Величина из второго регистра 2 поступает на вторые входы блока 6 сдвига, где сдвигается вправо на i-разрядов, т.е. на выходах блока.б сдвига образуется величина , которая поступает на четвертые входы сумматора 5. В зависимости от значения величины полученной на предыдущей итерации, в сумматоре 5 происходит операция вычитания (сложения) поступивших в него величин и х2-, т.е. на выходах сумматора 5 образуется ве. л-1 v. личина 2-V В конце -1 третьего такта величина .. передается из сумматора 5. в пятый регис 7, одновременно величина Vi-«--f передается из питого регистра 7 в третий регистр 3, а величина из тре тьего регистра 3 передается в первый регистр 1. В четвертом такте величина х из второго регистра 2 поступает на вто рые входы сумглатора 5. Величина ; из первого .регистра 1 поступает на первые входы блока б сдвига, где сдвигается на i-разрядов вправо, т.е на выходах блока б сдвига образуется величина Vl,- О. , которая поступает на четвертые входы сумматора 5 В зависимости от значения величины . , полученной на .предьщущей .итерации, в сумматоре 5 происходит операция сложения (вычитания).поступивших в него величин х,- и v г т.е. на выходах сумматора 5 образуется величина . Xj + .. . В конце .четвертого такта величина . передается из сумматора 5 в четвертый регистр 4, одновременно величина XY. передается из четвертого регистра 4 во второй регистр 2 а. величина V-f-4-i из третьего регистра 3 передается в первый регистр 1. По окончании четвертого такта с выхода знакового разряда первого регистра 1 или с выхода знакового разряда третьего регистра 3 снимается значение функции, показывающей напрешление вращения векторов .J sign ( ), которое-используется при выполнении следующей (1+1)-ой итерации. После п-кратного повторения итераций в регистрах 1-4 и 7, образуют ся результаты в первом регистре 1 - - О во втором регистре 2 - хц k-J в третьем регистре 3 - % О в четвертом регистре 4 - cos arctgv/x . в пятом регистре 5 - (и f sin arctg- /x Входы регистров Г-4 и 7 используются для .ввода в арифметическое устройство начальных значений, а выходы регистров 1-4 и 7 используются для вывода из арифметического устройства конечных результатов. Взаимосвязи между узлами арифметического устройства - связи выходов сумматора 5 со входами второго 2 и третьего 3 регистров и связи выходов четвертого регистра 4 с третьими входами сумматора 5 могут быть использованы при вычислении других элементарных функций,например, l/x,-Vx, 6og х. В этом случае функции первого 1 и , третьего 3 регистров берут на себя, соответственно, второй 2 и четвертый 4 регистры, а функции второгО 2 и четвертого 4 регистров - первый 1 и третий 3 регистры. Поскольку в каждом такте работы известного и предлагаемого устройства выполняются одни и те же операции сдвига, сложения (вычитания) и занесения в регистр, длительность такта t- величина одинаковая как для известного, так и для предлагаемого устройства. При вычисл.ении функций f sin. arctg i/x и 003 arctgv/x известное устройство дважды реализует :алгоритм (1),который требует п-циклов работы устройства по 3 такта в каждом цикле,т.е. известное устройство обладает временем вычислений бпт, а предлагаемое устройство один раз реализует алгоритм (2), который требует п-циклов работы устройства по 4 такта в каждом цикле, т.е. предлагаемое устройство обладает временем вычислений 4псГ. Предлагаемое устройство обладает быстродействием в fi 6пС/4пС 1,5, раза большим, чем известное. Эффективность изобретения - повышение быстродействия-устройства за счет сокращения времени вычислений. Формула изобретения Арифметическое устройство, содержащее первый, второй, третий и четвертый регистры, блок сдвига, сумматор/ причем выходы первого и второго регистров подключены к первому и второму входам блока сдвига, соответственно, первый, второй, третий и четвертый входы сумматора подключены, соответственно, к выходам первого, второго, четвертого регистров и к выходу блока сдвига, выход сумматора подключен к первым входам второго, третьего и четвертого регистров, соответственно, выход третьего регистра .подключен ко входу первого регистра, отличающееся тем, что, с целью увеличения быстродействия за

счет сокращения времени вычислений, в устройство дополнительно введен пятый регистр, причем вход пятого регистра подключен к выходу сумматора, а- выход - ко вторым входам третьего и четвертого регистров,-выход четвертого регистра подключен ко второму входу второго регистра.

Источники информации, принятые во внимание при экспертизе

функций в ЦВМ. Л., 1975, с.3-76 (прототип) .

Авторы

Даты

1981-01-23—Публикация

1979-03-11—Подача