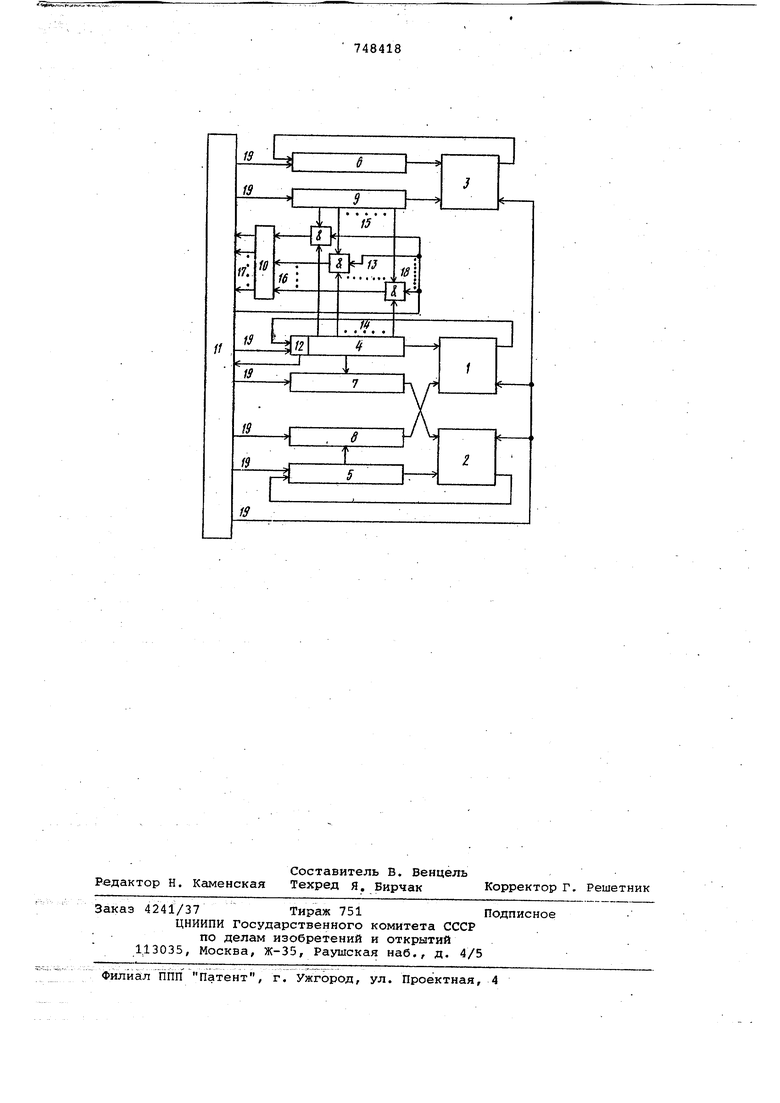

Устройство работает, используя следующие рекуррентные соотношения . . . (1) ...(gnУ, iM rt- -,aoctgaV . О-д.О. ; где : У| - текущее значение ординаты вектора, Xj - текущее значение абсциссы вектора., Uj - текущее значение аргумент ifi +1 или - 1 - рекуррентн оператор, 0,1,2,3,.. номер итерационного шага. Общее число итераций вычисления функций anctgf по этому методу ранно п , где г - число разрядов сдвиг щих регистров. j Недостатком устройства является низкое быстродействие при большой р рядности вычислительного устройстра Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для вычисления функции arctgv/x , содержащее блок управления, три накопительных сдвиговых регистра, регистр зайиси, два сдвигающих регистра и три сумматора-вычитателя, выходы которых соединены с первыми входами соответствующих накопительных сдвиговых регистров, выход знакового разряда первого накопительного сдвигового регистра соединен с первым входом блока управления, первый, вт рой, третий, четвертый, пятый и. шес той выходы блока управления подключены соответственно к управляющим входам первого, второго и третьего накопительных сдвигающих регистров, первого, второгЬ сдвигающих регистров и регистра записи, выходы младш разряда первого и второго накопител ного регистра соединены с первыми входами соответственно первого и второго сумматоров-вычитателей, в рой вход второго сумматора-вычитате подключен к выходу младшего разряда первого сдвигающего регистра, соединенного входом с выходом первого накопительного сдвигового регистра, а выход второго накопительного сдви вого регистра-СО входом второго сдв гового регистра, выход младшего раз да которого соединен со вторым входом первого сумматора-вычитателя, управляющий/вход которого соединен с седьмым выходом блока управления и управляющими входами второго и третьего сумматоров-вычитателей,первый и второй входы третьего сул4м тора-вычитателя соединены соответственно с выходами младших разрядов третьего накопительного сдвигового регистра и регистра записи, дополнительно введены элементы И и шифратор, причем выходы одноименных разрядов первого накопительного сдвигового регистра и регистра записи соединены соответственно с первыми и вторыми входами соответствующих элементов И, третьи входы которых соединены с восьмым выходом блока управления, а выходы элементов И подключены- ко входам шифратора, выходы которого соединены с соответствующими вторым -г (п + 1) см входами блока управления. На чертеже представлена структурная схема предлагаемого устройства, содержащего .сумматоры-вычитатели 1, 2,3, накопительные сдвиговые регистры 4, 5, б, первый и второй сдвигаю.щие регистры 7, 8, регистр записи 9, шифратор 10, -блок управления 11, знаковый разряд накопительного сдвигового регистра 12, элементы И 13, выходы разрядов накопительного сдвигового регистра 14, выходы разрядов регистра записи 15, выходы элементов И 16, выходы шифратора 17, управляющие входы элементов И 18, выходы блока управления 19. Работа устройства основана на следующем. Поскольку в конце операции величина у сводится к нулю, то можно задавать для первого шага Итерации вместо i - о некоторое начальное значение , зависящее от разности между V и нулем. То естью определяется номером разряда, содержащего первую значущую единицу в двоичном представлении аргумента. Например, v представлен кодом 0,000001101... Тогда VQ б, и число итераций будет равно n-io-ь 1. Устройство работает следуюврим образом. В регистр 9 записывается число, предс авленное единицами во всех разрядах после запятой, в регистр 4 заносится значение аргумента у . Затем на входы элементов И 13 поочередно, в соответствии с сигйалами управления входов 18, начиная со.старшего разряда, подаются значения содержимого одноименных разрядов 14 и 15 регистров 4 и 9. По сигналу первого же элемента И, на входы которого поступают обе единицы с регистров 4 и 9 и разрешающий сигнал из блока 11 управления, опрос регистров прекращается, а с соответствующего выхода 17 шифратора 10. на блок 11 управления передается,код начального шага итерации 1 о . Так элемент И вьщеляет первую значащую единицу аргумента v . В соответствии с итерационными соотношениями (1), блок 11 управления передает-команду сдвига содержимого регистра 4 на о разрядов в сторону младших разр5здов. Регистр отбрасывается в ноль,и на него из гистра записи вызывается константа arctga B регистр 5 заносится единиц в регистр б записывается ноль. Затем из содержимого регистра 4 в су маторе-вычитателе 1, с учетом знака ; , вычитается, сдвинутое в сторону младших разрядов , содержимое регистра 5, поступающее из вто рого сдвигающего регистра 8, а содержимое регистра -5 складывается с учетом знака Wj в сумматоре-вычитат 2 со сдвинутым в сторону младших разрядов содержимым регистра 4, поступающим из первого сдвигающего регистра 7. Содержимое регистра суммируется с учетом знака 9; с со держимым регистра 9 в сумматоревычитателе 3. На следующем цикле значение увеличивается на един в регистр 9 заносится из регистра записи константа a crigг) определяется очередное значение рекуррентного операто эач и итерационн соотнбшения (1) реализуются соглас но описанному алгоритму для новых значений i и , и т. д. В конце операции в регистре 4 получается ноль,в регистре 6 храни ся значение, равное arctg УД Эффективность изобретения зйклю ется в повышении быстродействия устройства для вычисления функции аглдг приблизительно в два раза за счет сокращения числа итераций на личину, определяемую номером разря да, содержащего первую значащую единицу в двоичном представлении аргумента, достигаемым за счет небольшого увеличения затрат оборудования. Формула изобретения: Устройство для вычисления функцииaгctlJ M , содержащее блок управления, три накопительных сдвиговых регистра, регистр записи, два сдви гающих регистра и три сумматора-вы тателя, выхЬды которых соединены с первыми входами соответствующих накопительных сдвиговых регистров, выход знакового разряда первого на копительного сдвигового регистра соединен с первым входом блока управления, первый, второй, третий, четвертьй, пятый и шестой выходы блока управления подключены соответственно к управляющим входам первого, второго и третьего накопительных сдвиговых регистров, первого, второго сдвигающих регистров и регистра записи, выходы младшего разряда первого и второго накопительных сдвиговых регистров соединены с, тервыми входами соответственно первого и второго сумматоров-вычитателей, второй вход второго сумматора-вычитателя подключен к выходу младшего разряда первого сдвигающего регистра, соединенного входом с (ВЫХОДОМ первого накопительного сдвигового регистра, а выход второго накопительного сдвигового регистрасо входом второго сдвигающего регистра, выход младшего разряда которого .соединен со вторым входом первого сумматора-вычитателя, управляющий вход которого соединен с седьмым выходом блока управления и управляющими входами второго и третьего сумматоров-вычитателей, первый и второй входы третьего сумматора-вычи|тателя соединены соответственно с ;выходами младших разрядов третьего на|копит льного сдвигового регистра ,и регистра записи, отличающееся тем, что, с целью повышения быстродействия за счет сокра:щения числа интераций, в него введены элементы И и шифратор, причем выходы одноименных разрядов первого накопительного сдвигового регистра и регистра записи соединены соответственно с первыми и вторыми входами соответствующих элементов И, третьи входы которых соединены с восьмым выходом блока упйавления, выходы элементов И подключены ко входаГл шифратора, выходы которого соединены с соответствующими вторым (п +1)м входами блоками управления. Источники информации, принятые во внимание при экспертизе 1.Гречишников А. Н. Лутай.В. Н, Чалабов Н. Г. Использование операций над векторами при выполнении быстрого преобразования Фурье, Автометрия № 3, 1973. 2.J. Е. Voider. The CORDIC trlgon6metric computing technique iRE Transactions on Electronic Computers, vol , 8, 1959, 3. . ,

748418

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Цифровой функциональный преобразователь | 2017 |

|

RU2642381C1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления корня к-ой степени | 1976 |

|

SU736096A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

Авторы

Даты

1980-07-15—Публикация

1978-05-10—Подача