1

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных устройств для выполнения операций сложения, вычитания, умножения, деления , извлечения квадратного корня при обработке больших массивов многоразрядных чисел.

Известны арифметические устройства, вычисляющие элементарные преобразования за время, приблизительно равное времени реализации операции умножения tl.

Однако структуры устройств не предназначены для обработки больших массивов чисел.

Известно арифметическое устройство, состоящее из последовательно соединенных однотипных блоков. Каждый блок арифметического устройства содержит три регистра, комбинационный сумматор, узел анализа переполнения сумматора, триггер переполнения, первый коммутатор, содержащий элемент И-ИЛИ, и второй коммутатор, содержащий п элементов И-ИЛИ.

Арифметическое устройство предназначено для выполнения операций сложения, вычитания, умножения, деления , извлечения квадратного корня

при обработке больших массивов многоразрядных чисел.

Недостаток устройства - :структурная сложность.

Наиболее близким по технической сущности к предлагаемому является арифметическое устройство, состоящее из п последовательно соединенных однотипных блоков, каждый из ко0торых содержит первь й, второй и третий регист1ил, сумматор, блок анализа, триггер, первый и второй коммутаторы 2.

Недостаток устройства - сложность

5 второго коммутатора и структуры устройства в целом.

Цель изобретения - упрощение структу1яа арифметического устройства.

Поставленная цель достигается тем,

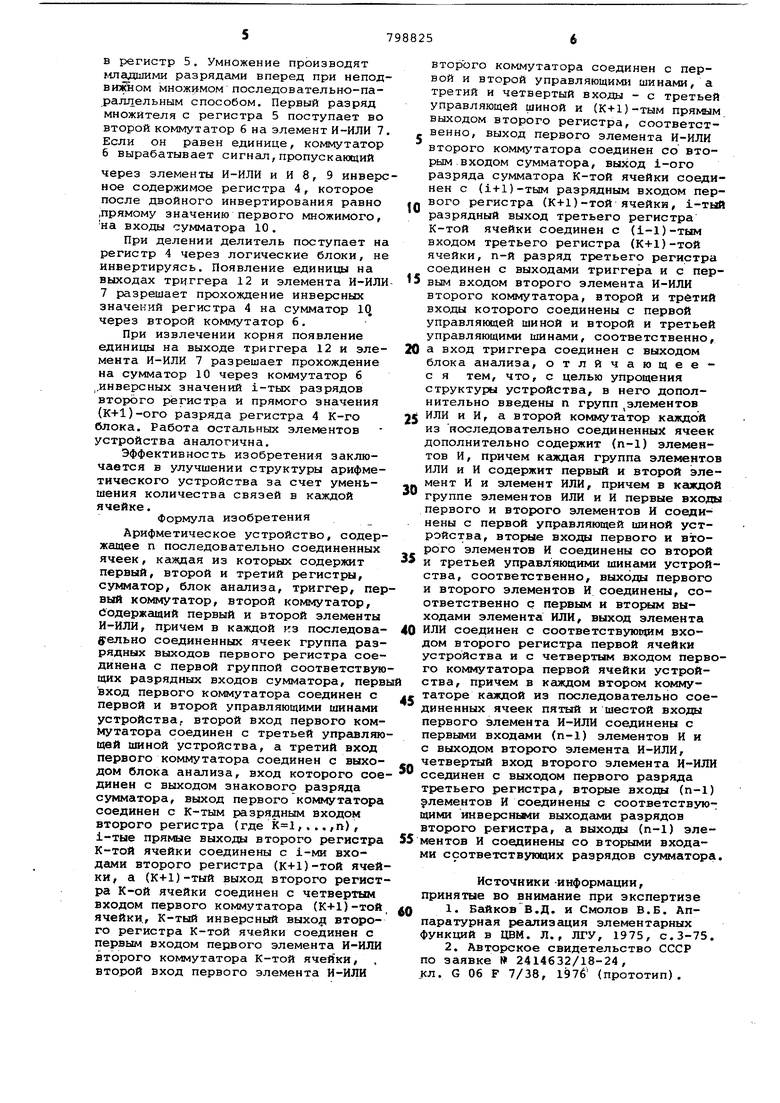

0 что в арифметическое .устройство, содержащее п последовательно соединенных ячеек, каждая из которых содержит первый, второй и третий регистры, сумматор, блок анализа, триггер, первый кс 1утатор, второй коммутатор, содержащий первый и второй элементы И-ИЛИ, причем в каждой из последовательно соединенных ячеек группа разрядных выходов первого регистра соединена с первой группой соответствуюгцих разрядных входов сумматора, пер вый вход первого коммутатора соединен с первой и второй управляющими шинами устройства, второй вход первого комм татора соединен с третьей управляющей шиной устройства, а тре тий вход первого коммутатора соединен с выходом блока анализа, вход которого соединен с выходом знаково го разряда су чматора, выход первого коммутатора соединен с. К-тым разрядным входом второго регистра (где ...,п), i-тые прямые выходы вторых регистров К-той ячейки соединены с 1-ми входами второго регистра (К+1)гой ячейки, а (К+1)-тый выход второго регистра К-той ячейки соединен четвертым входом первого коммутатора (К+1)-той ячейки, К-тый инверсный выход второго регистра К-той ячейки соединен с первым входом первого эле мента И-ИЛИ второго коммутатора К-то ячейки, второй вход первого элемента И-ИЛИ второго коммутатора соединен с первой и второй управляющими шинами, а третий и четвертый входы - с третьей управляющей шиной и (К+1)-ты прямым выходом второго регистра, выход первого элемента И-ИЛИ второго коммутатора соединен со вторым входом, сумматора, выход i-oro разряда сумматора К-той ячейки соединен с (i+l)-THM разрядным входом первого регистра (К+1)-той ячейки, i-тый разрядный выход третьего регистра К-той ячейки соединен с (±-1)-тым входом третьего регистра (К+1)-той ячейки, п-й разряд третьего регистра соединен с выходом триггера и с первым входом второго элемента И-ИЛИ второго коммутатора, второй и третий входы которого соединены с первой управляющей шиной и второй и третьей управляющими шинами, соответственно а вход триггера соединен с выходом блока анализа, дополнительно введены п групп элементов ИЛИ и И, а второй коммутатор каждой из последовательн соединенных ячеек дополнительно содержит (п-1) элементов И, причем каждая группа элементов ИЛИ и И содержит первый и второй элемент И и элемент ИЛИ, причем в каждой группе э ементов ИЛИ и И первые входы первого и второго элементов И соединенЫ cf первой и управляющей шиной устрой . а)(гв.а,вторые входы первого и второго элементов И соединены со второй и третьей управлянмцими шинами устройства, соответственно, выходы первого и второго элементов И соединены, соответственно, с первым и вторы входами элемента ИЛИ, выход элемента ИЛИ соединен с ссютветствукяцин входом второго регистра первой ячей,ки устройства и с четвертым входом первого коммутатора первой ячейки устройства, причем в каждом втором коммутаторе каждой из последователь соединенных ячеек пятый и шестой вхояы первого элемента И-ИЛИ соединены . с первыми входами (п-1) элементов И и выходом второго элемента И-ИЛИ четвертый вход второго элемента И-ИЛИ соединен с выходом первого разряда третьего регистра, вторые входы (п-1) элементов И соединены с соответствующими инверсными выходами разрядов второго регистра, а выходы (п-1) элементов И соединены со вторыми входами соответствующих разрядов сумматора. На чертеже представпена функциональная схема арифметического устройства. Арифметическое устройство содержит п логических блоков, образованных элементами И 1, 2 и ИЛИ 3, и п однотипных ячеек, каждая из которых содержит регистры 4 и 5, коммутатор 6 (содержащий элементы И-ИЛИ 7,8 и И 9), сумматор 10с дополнительными разрядами 11, триггер 12, выход 13 которого соединен со входом п-го разряда регистра 5, регистр 14, управляющие шины 15, 16 и 17, блок анализа 18, коммутатор 19. Первые входы элементов И 1, 2 являются входами 20 устройства, вторые входы соединены с управляющими шинами 17 и 16 умножения и деления, соответственно. Выходы элементов И 1, 2 (причем выход элемента И 2 - инверсный) объединены элементом ИЛИ 3. Выходы логических блоков (которыми являются выходы элементов ИЛИ 3) соединены с соответствующими входами регистра 4 первой ячейки, кроме первого входа регистра 4, соединенного с выходом логического блока через коммутатор 19. Первая группа входов элемента И-ИЛИ 8 коммутатора 6 соединена с управляющей шиной умножения 17 и деления 18, с выходом элемента И-ИЛИ 7 и инверсным выходом (К+1)-ого разряда регистра 4, вторая группа входов элемента И 2 соединена с управляющей шиной 16 извлечения корня, с пряным выходом (К-И)-ого разряда регистра 4 и с выходом элемента И-ИЛИ 7. Первые входы элементов И 9 соединены с 1-ми инверсными выходами регистра 4, а вторые входы всех элементов 9 объединены и соединены с выходом элемента И-ИЛИ 7. Первая группа входов элемента ИИЛИ 7 соединена с первым выходом регистра 5 и с управляющей шиной деления и извлечения корня и с выходом триггера 12. Арифметическое устройство работает следутопим образом. При умножении первое множимое Инвертируется в элементе И 2 и поступает через элемент ИЛИ 3 в регистр „4 первого блока, а первый множитель в регистр 5. Умножение производят младшими разрядами вперед при неподвижном множ1 мом последовательно-параллельным способом. Первый разряд множителя с регистра 5 поступает во второй коммутатор 6 на элемент И-ИЛИ 7 Если он равен единице, коммутатор 6вырабатывает сигнал,пропускающий через элементы И-ИЛИ и И 8, 9 инверс ное содержимое регистра 4, которое после двойного инвертирования равно .прямому значению первого множимого, на входы сумматора 10. При делении делитель поступает на регистр 4 через логические блоки, не инвертируясь. Появление единицы на выходах триггера 12 и элемента И-ИЛИ 7разрешает прохождение инверсных значений регистра 4 на сумматор 1Q через второй коммутатор 6. При извлечении корня появление единицы на выходе триггера 12 и элемента И-ИЛИ 7 разрешает прохождение на сумматор 10 через коммутатор б ,,инверсных значений i-тых разрядов второго регистра и прямого значения (К+1)-ого разряда регистра 4 К-го блока. Работа остальных элементов устройства аналогична. Эффективность изобретения заключается в улучшении структуры арифметического устройства за счет уменьшения количества связей в каждой ячейке. Формула изобретения Арифметическое устройство, содержащее п последовательно соединенных ячеек, каждая из которых содержит первый, второй и третий регистры, сумматор, блок анализа, триггер, пер вый коммутатор, второй коммутатор, Содержащий первый и второй элементы И-ИЛИ, причем в казкдой из последовацельно соединенных ячеек группа разрядных выходов первого регистра соединена с первой группой соответствую щих разрядных входов сумматора, перв вход первого коммутатора соединен с первой и второй управляющими шинами устройства, второй вход первого коммутатора соединен с третьей упргшляю щвй шиной устройства, а третий вход первого коммутатора соединен с выходом блока анализа, вход которого сое динен с выходом знакового разряда сумматора, выход первого коммутатора соединен с К-тым разрядным входом второго регистра (где ,,..,п), i-тые прямые выходы второго регистра К-той ячейки соединены с i-ми входами второго регистра (К+1)-той ячей ки, а (К+1)-тый выход второго регист ра К-ой ячейки соединен с четвертым входом первого коммутатора (К+1)-той ячейки., К-тый инверсный выхоц второго регистра К-той ячейки соединен с первым входом первого элемента И-ИЛИ второго коммутатора К-той ячейки, второй вход первого элемента И-ИЛИ второго коммутатора соединен с первой и второй управляющими шинами, а третий и четвертый входы - с третьей управляющей шиной и (К+1)-тым прямым выходом второго регистра, соответственно, выход первого элемента И-ИЛИ второго коммутатора соединен со вторым входом сумматора, выход i-oro разряда сумматора К-той ячейки соединен с (1+1)-тым разрядным входом первого регистра (К+1)-той ячейки, i-тый разрядный выход третьего регистра К-той ячейки соединен с (1-1)-тым входом третьего регистра (К+1)-той ячейки, п-й разряд третьего регистра соединен с выходами триггера и с первым входом второго элемента И-ИЛИ второго коммутатора, второй и трбтий входы которого соединены с первой управляющей шиной и второй и третьей управляющими шинги и, соответственно, а вход триггера соединен с выходом блока анализа, отлйчающеес я тем, что, с целью упрощения структуры устройства, в него дополнительно введены п групп элементов ИЛИ и И, а второй коммутатор каждой из последовательно соединенных ячеек дополнительно содержит (п-1) элементов И, причем Кс1ждая группа элементов ИЛИ и И содержит первый и второй элемент И и элемент ИЛИ, причем в каждой группе элементов ИЛИ и И первые входы первого и второго элементов И соединены с первой управляющей шиной устройства, вторые входы первого и второго элементов И соединены со второй и третьей управляющими шинами устройства, соответственно, выходы первого и второго элементов И соединены, соответственно с первым и вторым выходами элемента ИЛИ, выход элемента ИЛИ соединен с соответствующем входом второго регистра первой ячейки устройства и с четвертым входом первого коммутатора первой ячейки устройства, причем в каждом втором коммутаторе каждой из последовательно соединенных ячеек пятый ишестой входы первого элемента И-ИЛИ соединены с первыми входами (п-1) элементов И и с выходом второго элемента И-ИЛИ, четвертый вход второго элемента И-ИЛИ соединен с выходом первого раэряда третьего регистра, вторые входа (п-1) элементов И соединены с соответствующими инверсными выходами разрядов второго регистра, а выходы (п-1) элементов И соединены со вторыми входами соответствующих разрядов сумматора. Источники -информации, принятые во внимание при экспертизе 1.Байков В.Д. и Смолов В.Б. Аппаратурная ресшиэсщия элементарных функций в ЦВМ. Л., ЛГУ, 1975, с.3-75. 2.Авторское свидетельство СССР по заявке 2414632/18-24, кл. G 06 F 7/38, 1976 (прототип).

1/J7

|/

1

т.

/5 /б

h

44; го

tf I

го .„/5

If

/

ч и

«J -г

-F

I

д

«

г 3

J

Ч л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения ритма сердца | 1985 |

|

SU1284512A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР ЕРМАКОВА-КАЖДАНА СПЕКТРА КУСОЧНО-ПОСТОЯННЫХ ФУНКЦИЙ (ВАРИАНТЫ) | 2001 |

|

RU2213996C2 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Арифметическое устройство | 1982 |

|

SU1089577A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

Г7

Г

4

wto

И

S

15

I .

5

П

Авторы

Даты

1981-01-23—Публикация

1979-04-06—Подача