Недостатками устройства является снижение надежности из-за необходимости введения гибкой адресации, снжение коэффициента использования г аппаратуры из-за затрат времени на перераспределение модулей памяти меду процессорами в процессе работы.

Цель изобретения - повышение надежности и коэффициента использования оборудования.

Поставленная цель достигается тем что в устройство для управления резервированием информации в вычислительных комплексах, содержащее регистр операций, выход которого подключен ко входу дешифратора, блока управления записью, выход которого соединен с первым управляющим выход устройства, первый элемент И, первы и второй элементы ИЛИ, выходы которых подключены соответственно ко входам первого элемента И, входы пезого элемента ИЛИ соединены соответственно с первым и вторым входами устройства, входы второЬо элемен ИЛИ соединень соответственно с третьим и четвертым входами устройства, введены триггер, третий и четвертый элементы ИЛИ, второй и третий элементы И, причем первый вход третьего элемента - ИЛИ соединен с первым выходом.дешифратора, второй .выход которого подключен ко второму входу третьего элемента ИЛИ и к единичному входу триггера, выход третьего элемента ИЛИ соединен с первым входом блока управления записью, второй вход которого соединен с выходом четвертого элемента ИЛИ, а выход подключен к первому входу второго элемента И, второй вход которого подключен к единичному выходу триггера, выход второго элемента И соединен со вторым управляющим выходом устройства, нулевой вход триггера соединен с выходо первого элемента ИЛИ, входы третьего элемента И подключены соответст венно к нулевому выходу триггера и к выходу второго элемента ИЛИ, выходы первого и третьего элементов И подключены соответственнч ко входам четвертого элемента ИЛИ.

Введением указднных выше дополни тельных элементов и связей в состав операций процессоров комплекса вводится специальная, операция Запись с резервированием, при выполнени:и которой происходит резервирование информации. При выполнении остальных Операций такого резервирования н.е производится. Благодаря этому, при разработке программного обеспечения комплекса обеспечивается возможность записи одновременно в обе группы модулей памяти только той информации, которая необходима для организации взаимодействия процессоров и.продолжения работы комплекса при отказе отдельных, модулей памяти .

В отличие от известных устройств для кратковременного доступа процессора в резервные запоминающие с устройства не требуется выполнять дополнительных операций подключения процессора к этим устройствам, либо включать в состав комплексов дополнительную аппаратуру, обеспечивающую

Q постоянный доступ каждому из процессоров в резервируемые зоны общей оперативной памяти.

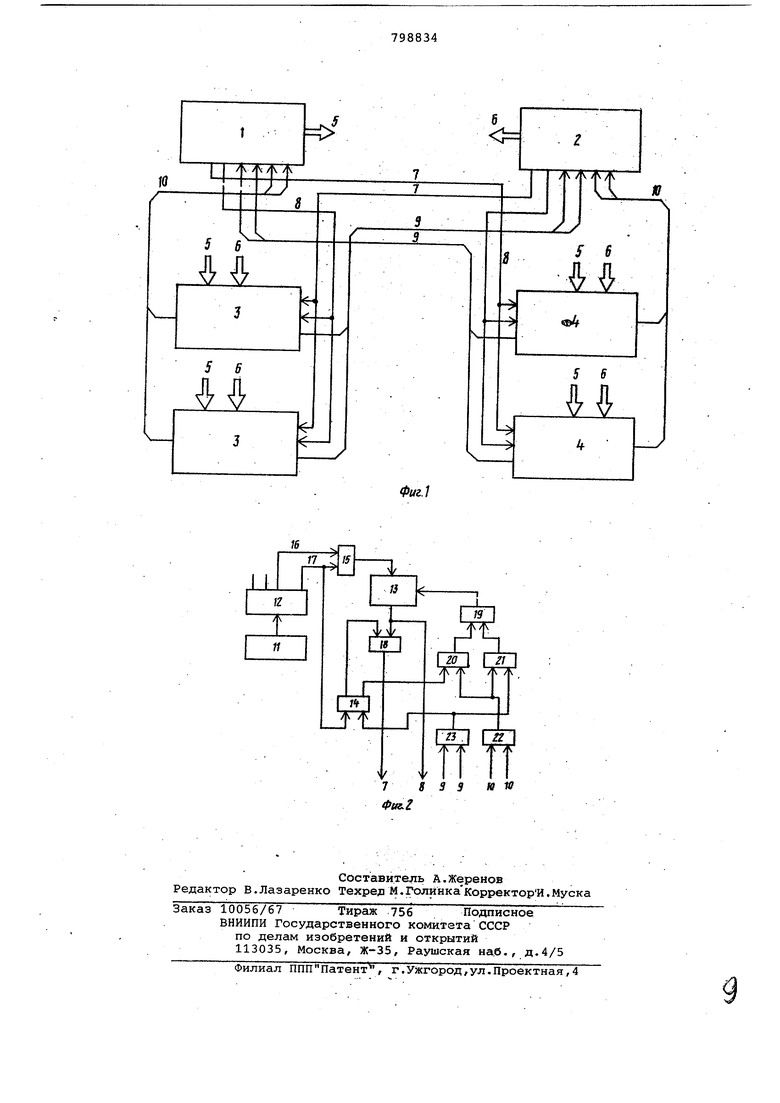

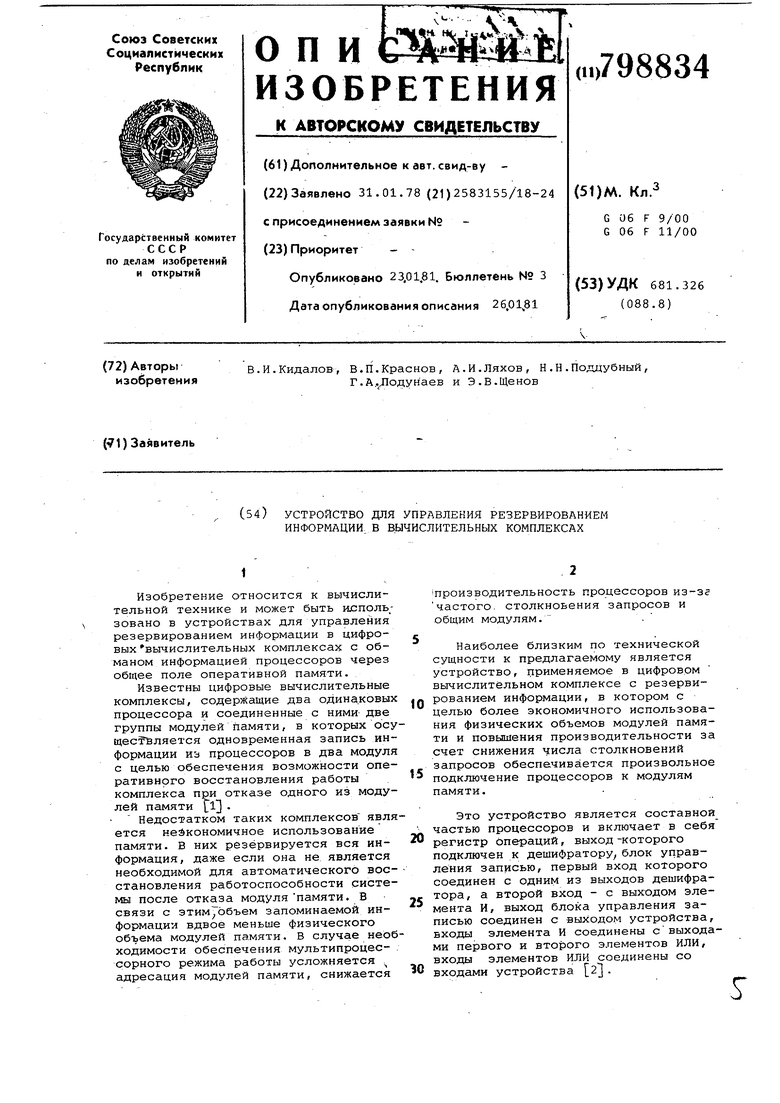

На фиг. 1 приведена структурная схема цифрового вычислительного - комплекса} на фиг. 2 - структурная

схема устройства для управления резервированием информации.

В состав комплекса входят первый процессор 1, второй процессор 2, модули 3 памяти первой группы и модули

0 4 памяти второй группы. Процессор 1 соединен с модулями 3 и 4 памяти кодовыми магистралями 5, а процессор 2 соединяется с модулями памяти кодовыми магистралями 6. Процессор 1 и

5 процессор 2 связаны с модулями 3 и 4 памяти шинами Запись 7 и 8, а также - Конец записи 9 и 10.

Устройство для управления резервированием информации включены в

Q состав процессоров цифрового вычислительного комплекса.

В устройство управления резервированием информации входят регистр 11 операции, подключенный к нему деe шифратор 12 операций блок 13 управления записью и триггер 14, предназначенный для оперативного управления резервированием информации.

Входы регистра операций соединяются с выходами .эегистра команд (на

0 чертеже регистр команд не показан).

Первый вход блока 13 управления записью соединяется с выходом элемента ИЛИ-15, первый вход которого соединен связью 1.6 с выходом дешифратора 12 операций, соответствующим операц.ии Запись. Второй вход элемента ИЛИ 15 соединен связью 17 с другим выходом дешифратора 12 операций, соответствующим операции Запись

0 с резервированием, а также с единичньм входом триггера 14. Выход блока 13 управления записью соединен с первым входом элемента И 18 и первым управляющим выходом устройства, котое рый, в свою очередь, соединен с шиной 8 Запись модулей памяти. Второй вход элемента И 18 соединён с единичным выходом триггера 1. Выход элемента И 18 соединён со вторым управляющим выходом устройства. Второй управляюQ щий выход устройства соединен с шиной 7 Запись модулей памяти. Второй вкод блока 13- управления записью соединен с 5ЫХОДОМ элемента ИЛИ 19.

Входы элемента ИЛИ 19 соединены с

5 выходами двух элементов И 20 и 21.

Первый вход элемента И 20 соединен с нулевым выходом триггера 14. Второй вход элемента И 20 соединен с первым входом элемента И 21 и выходом элемента ИЛИ 22. Второй вход элемента

И 21 соединен с нулевым входом триг гера 14 и выходом элемента ИЛИ 23. Входы элемента ИЛИ 22 соединены с первым и вторым входами устройства. Входы элемента JiJiIi 23 соединены с третьим и четвертым входами устройства. Первый, второй и третий., четвертый зходы устройства соединены с шинами 9 и 10 Конец записи модулей памяти соответственно.

По кодовьом магистралям 5 и 6 цифрового вычислительного комплекса передаются во все модули памяти адреса и записываемая информация. Сигналом, разрешающим выполнение записи информации, передаваемой по кодовым магистралям 5 и б, является сигнал Запись, передаваемый по шинам 7 и 8 из процессора. Об окончании записи информации в модуль памяти свидетельствует выдача сигнала по шинам 10 Конец записи из модулей памяти в процессор.

Модули памяти имеют адресные селекторы, с помощью которых фиксируется совпадение математических адресов присвоенных модулям, и адресов передаваемых по кодовым магистралям. Кроме того, в модулях памяти имеются устройства местного управления, которые организуют поочередное обслуживание запросов от двух процессоров.. Двум модулям памяти, находящимся в разных группах, назначаются одни и те же математические адреса .

Основным режимом работы комплекса ,является одновременное решение разных задач под управлением диспетчерской прощэаммы, выполняемой на одном из процессоров. В процессе работы в модулях памяти с одинаковыми математическими адресами, находящихся в разных группах , формируются общие информационные зоны, содержащие данные , необходимые как для одновременного выполнения задач двумя процессорами, так и для сохранения информации на случай выхода из строя: одного из модулей памяти. При отказе одного из модулей памяти работу продолжает один процессор (любой), который выполняет полный перечень задач, используя зарезервиро анную в модуле памяти другой группы информацию. Задачи в резервном режиме работы выполняются реже, чем в основном, либо выборочно не в полном составе, только наиболее важные..

Общие информационные зоны формируются при выполнении в процессоре операции Запись с резервированием, которая применяется программистом в случае необходимости записи информации в две группы модулей памяти.

Остальные зоны памяти формируются при выполнении процессорами других операций, являются индивидуальными для каждого из процессоров и не совпадают в двух группах модулей. Обращение на считывание проходит из каждого процессора только на соответствующую ему группу модулей памяти.

Операция: Запись выполняется в комплексе следующим образом.

0

После установки на регистре 11 .операций кода операции, с выхода дешифратора 12 операций по связи 16 поступает сигнал, который через элемент ИЛИ 15 подается на вход блока

s 13 управления записью.

При выполнении операции . Запись с резервированием с выхода дешифратора 12 операций псг связи 17 поступает сигнал на единичный вход триггера 14 и на вход элемента ИЛИ 15. Блок 13

0 управления записью запускается сигналом с выхода элемента ИЛИ 15, организует передачу информации и адреса из регистров процессора на кодовуй магистраль, выдает сигналы Запись

5 на шину В, поступающие в модули памяти соответствующей процессору группы, и сигналы Запись через элемент И 18, открытый потенциалом с единичного выхода триггера 14, на шины 7,

0 поступающие в другую группу модулей памяти. .

Этот блок организует передачу информации и адреса из регистров процессора на кодовую магистраль (сиг5налами, не показанньлу1и на чертеже) и с задержкойвыдает сигнал Запись на шину 8, который поступает в модули памяти соответствующей процессору группы. Сигнал Конец записи из модуля памяти, принявшего инфор0мацию, поступает по шине 10 в процессор на вход элемента ИЛИ 22. С выхода элемента ИЛИ 22 через элемент И 20, на второй вход которого поступает разрешающий потенциал с нулево5го нйхода триггера 14. Сигнал с выхода элемента И 20 поступает на вход элемента ИЛИ 19 и с выхода его - на второй вход блока управления записью. Блок 13 управления записью после

O этого организует переход процессора на выполнение следующей операции.

с

После завершения записи в модулях памяти обеих гоупп появляются сигналы Конец записи на входах элементов

5 ИЛИ 22 и 23. Сигналы с выходов элементов ИЛИ 22 и 23 поступают на вход элемента И 21.сли запись прошла в модулях памяти обеих групп, на выходе элемента И 21 появляется сигнал,

О который далее проходит через элемент

ИЛИ 19 на вход блока 13 управления записью. Триггер 14 сбрасывается в исходное состояние сигналом с выхода элемента ИЛИ 23. Блок 13 ynt5равления записью организует переход

процессора на выполнение следующих Операций.

В цифровом вычислительном комплек се, использующем описанное устройство, повышается гибкость управления составом резервируемой информации благодаря чему расширяются функциональные возможности комплекса и повышается его надежность, более полно используется физический объем памяти комплекса (повышается коэфиициент использования оборудования).

Формула изобретения

Устройство для управления резервированием информации в вычислительных комплексах, содержащее регистр операций, выход которого подключен ко входу дешифратора, блок управления записью, выход которого соединен с nepBfcJM управляющим выходом устройства, первый элемент И, первый и второй элементы ИЛИ, выходы которых подключены соответственно ко входам первого элемента И, входы первого элемента ИЛИ соединены соответственно с первым и вторым входами устройства, входы второго элемента ИЛИ соединены соответственно с третьим и четвертым входами устройства, отлича-ющееся тем, что, с целью повышения надежности и коэффициента использования оборудования, в него введены триггер, третий и четвертый элементы ИЛИ, второй и третий элементы И, причем первый вход третьего элемента ИЛИ соединен с первым выходом дешифратора, второй выход которого подключен ко второму входу третьего элемента ИЛИ и к единичному входу триггера, выход третьего элемента ИЛИ соединен с первым входом блока управления записью, второй вход которого соединен с выходом четвертого элемента ИЛИ, а выход - подключен к первому входу второго элемента И, второй вход которого подключен к единичному выхо5 ДУ триггера, выход второго элемента И соединен со вторым управляющим выходом устройства, нулевой вход триггера соединен с выходом первого элемента ИЛИ, входы третьего элемента И подключены соответственно ч; нулевому выходу триггера и к выходу второго элемента ИЛИ, выходы первого и третьего элементов И подключены соответственно ко входам четвертого элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3838261, кл. 235-153 А F (G 06 F 15/16), опублик. 1974.

- 2.Патент США № 3905023, кл. 235-153 ЛК {G Об F 11/06), опублик. 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированная вычислительная система | 1989 |

|

SU1798946A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1056267A1 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Устройство для связи процессоров | 1984 |

|

SU1193682A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Резервированная система | 1988 |

|

SU1584137A1 |

Авторы

Даты

1981-01-23—Публикация

1978-01-31—Подача