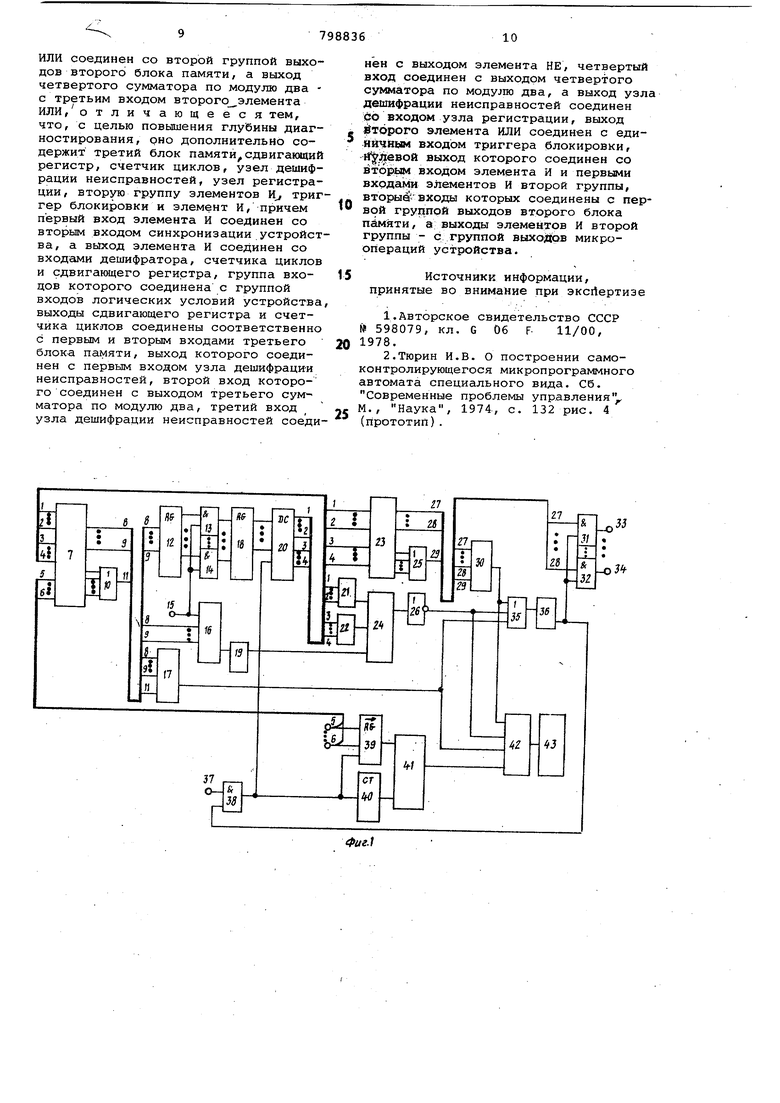

Изобретение относится к вычислительной технике и может быть использовано при построении микропрограммных управляющих устройств ЭВМ и дру гих систем. Известен самоконтролируемый микро программнйй автомат, содержащий регистры, дешифраторы 1 . Недостатком такого устройства является низкая глубина диагностирования, обусловленная локализацией от каза на уровне блока или группы блоков. Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому являет ся самоконтролируемый микропрограммный автомат, содержащий матрицы переходов и выходов, первый и второй регистры, дешифратор, узел формирования признака четности, четыре сумматора по модулю два, узел сравнения триггер признака, группу элементов И три элемента ИЛИ, элемент НЕ. В устройстве отказ обнаруживают точностью до контролируемого узла. Эт9 обуславливает низкую глубину диа ностирования, которую оценивают числом классов неразличаемых между собо неисправных состояний устройства PJ Однако низкая глубина диагностирования обуславливает большое время поиска отказавшего элемента (группы элементов), при восстановлении работоспособности устройства путем заземления отдельных элементов(групп элементов) . Цель изобретения - повышение глубины диагностирования устройства. Поставленная цель достигается тем, что микропрограммное устройство управления с контролем, содержащее дешифратор, первая группа выходов которого соединена с первыми группами входов кода микрокоманд первого и второго блоков памяти и с группой входов первого сумматора по модулю два, вторая группа выходов дешифратора соединена со вторыми группами входов кода микрокоманд первого и jBTOporo блоков памяти и с группой входов второго сумматора по модулю два, группа входов логических условий первого блока памяти соединена с группой входов логических условий устройства, первая группа выхо,цов первого блока памяти соединена с группой . информационных входов первого регистра-, группами входов узла формирования признака четности и третьего сумматора по модулю два, вход которого через первый элемент .ИЛИ соединен со второй группой первого блока памяти, а выход третьего сумматора по модулю два- с первым входом второго элемента. ИЛИ, второй вход которого через элемент.НЕ соединен с выходом узла сравнения ,v первый вход которого через триггер признака соединен с выходом узла формирования признака четности, вход которого соединен с первыгл входом синхронизации устройства и первыми входами элементов И первой группы, вторые входы которых соединены с соответствующими выходами первого регистра, а выходы элементов И первой группы соединены с соответствующими информационными входами второго регистра, группа разрядных выходов которого соединена с группо входов дешифратора,.выходы первого второго сумматоров по модулю два сое динены- соответственно со вторым и третьим входами узла сравнения, пер вая группа выходов второго блока па мяти соединена с группой входов чет вертого сумматора по модулю два, вход которого через третий элемент ИЛИ соединен со второй группой выходов второго блока памяти, а выход четвертого сумматора по модулю два-« с третьим входом второго элемента ИЛИ, содержит третий блок п амяти сдвигающий регистр, счетчики циклов узел дешифрации неисправностей, узел регистрации, вторую группу эле ментов И, триггер блокировки и элемент И, первый вход которого соединен со вторым входом синхронизации устройства, а выход - с входами дешифратора, счетчика циклов и сдви-. гающего регистра, группа входов которого соединена с группой входов логических условий устройства, выходы сдвигающего регистра и счетчика циклов соединены соответственно с первым и вторым входами третье го блока памяти, выход которого сое -динен. с первым входом узла дешифрации неисправностей, второй вход которого соединен с выходом огретьего сумматора по модулю .два, третий вход узла дешифрации неисправностей соединен с выходом элемента НЕ, чет вертый вход соединен с выходом четвертого .сумматора по модулю два, а выход узла дешифрации неисправносте соединен со входом узла регистрации выход второго элемента ИЛИ соединен с единичным входом триггера блокиро ки, нулевой выход которого соединен со вторым входом элемента И и первы входами элементов И второй группы, вторые входы которых соединены с первой.группой выходов второго блока памяти, а выходы - с группой выходов микроопераций устройства. Сущ ность изобретения состоит в повнулен глубины диагностирования путем сопоставления множества элементов микрс программного автомата участвующих в каждом цикле его работы. В предлагаемое устройство номер отказавшего узла определяется в зависимости от сигналов отказа, появляющихся на выходах средств контроля каждого из узлов. Для определения номера цикла- и элементов, участвующих в его выполнении, в устройство введены сдвигающий регистр, счетчик циклов и третий блок памяти. На фиг. 1 приведена функциональная схема самодиагностируемого микропрограммного устройства управления; на фиг.2 - пример определения отказавшего .элемента (группы элементов) . Схема содержит первую группу выходов дешифратора, первую группу входов первого и второго блоков памяти/ группу входов первого сумматора 1 и. 2 по модулю два, вторую группу выходов дешифратора, вторую группу входов .первого и второго блоков памяти, группу входов второго сумматора 3 и 4 по модулю два, группу входов логических условий устройства, группы входов сдвигающего регистра и первого блока 5 и б Ъамяти, первый блок 7 памяти, первую группу выходов первого блока памяти, первые группы входов узла формирования признака четности третьего сумматора по модулю два и группы входов 8 и 9 первого регистра первый элемент ИЛИ 10, выход первого элемента ИЛИ и второй вход 11 третьего сумматора по модулю два, первый регистр 12, первую группу элементов И 13 и 14, первый вход 15синхронизации устройства, узел . 16формирования признака четности, третий сумматор 17 по модулю два, второй регистр 18, триггер 19 признака, дешифратор .20, первый и второй сумматоры 21 и 22 по модулю два соответственно, второй блок 23 памяти, узел 24 сравнения, третий элемент .ИЛИ 25, элемент НЕ 26, первую группу выходов второго блока памяти, первую группу входов четвертого сумматора по модулю два и вторые входы второй группы элементов И 27 и 28, выход третьего элемента И и второй вход 29 четвертого сумматора по модулю, четвертый сумматор 30 по модулю два, вторую группу элементов И 31 и 32, группу выходов 33 и .34 микроопераций устройства, второй элемент ИЛИ 35, триггер 3fi блокировки, второй вход 37 синхронизации устройства, элемент И 38, сдвигающий регистр 39, счетчик 40-циклов, третий блок 41 памяти, узел 42 дешифрации неисправностей, узел регистрации 43. На фиг. 2 использованы следующие обозначения: М (, - множество элементов i-го контролируемого узла

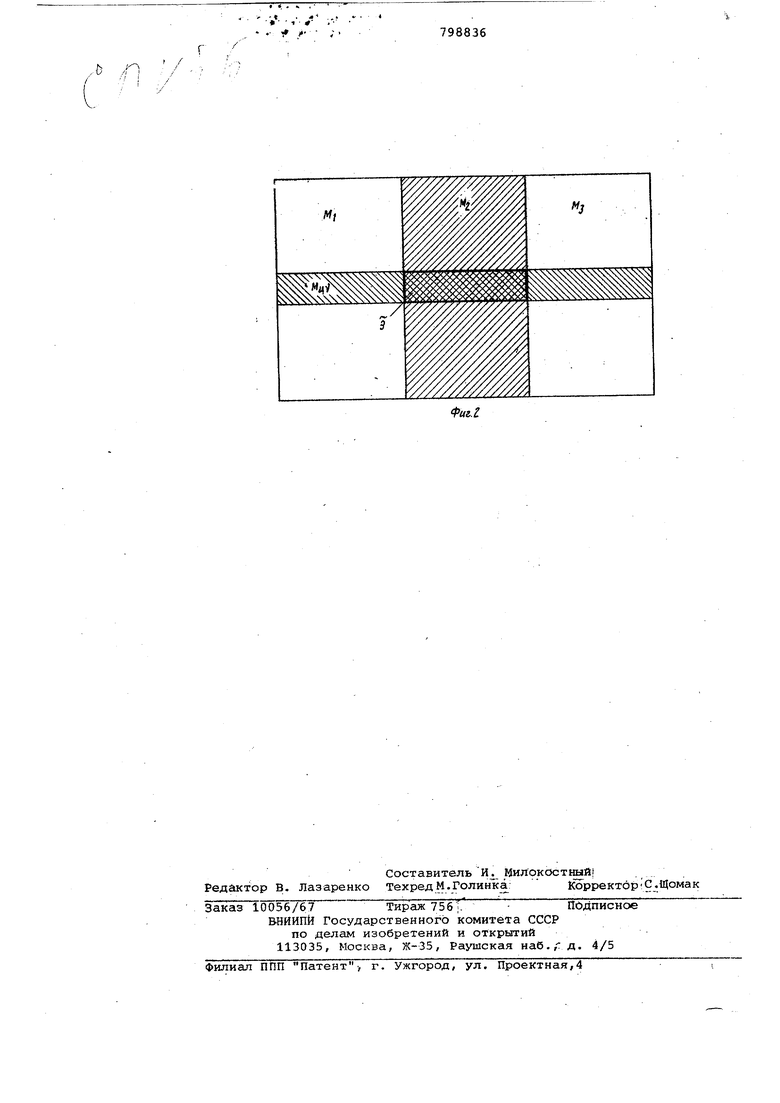

(,2 и 3),Мц, - множество элементо участвующих в выполнении -того цикла работы,. э - отказавший элемен (группа элементов) второго контролируемого узла.

Микропрограммное устройство с контролем состоит из трех частей: микропрограммного устройства управления средств контроля, основных узлов и средст, диагностики отказавших элементов.

Микропрограммное устройство управления состоит из трех контролируемых узлов, первого - первого блока 7, второго - первый 12| второй 18 регистры и дешифратор третьего блока 23 памяти. Первый контролируемый узел формирует код очередной микрокоманды в зависимости от кода предыдущей микрокоманды, поступающего на входы 1-4, и значений логических условий, поступающих на входы 5 и б.

Второй контролируемый узел предназначен для хранения и дешифрации кода очередной микрокоманды, который поступает на входы 8 и 9 первого регистра 12,а затем переписывается по первому синхроимпульсу через первую группу элементов И 13 и 14 во второй регистр 18 и дешифрируется дешифратором 20.

Третий контролируемый узел формирует сигналы микроопераций на выходах 27 и 28 в зависимости от кода микрокоманды, поступающего, с дешифратора 20 на входы .

Средства контроля состоят из первого элемента ИЛИ 10 и третьего сумматора 17 по модулю два - для первого контролируемого узла, узла 16 формирования признака .четности, триггера 19 признака, первого 21 и второго 22 сумматора по модулю два, узла 24 сравнения и элемента НЕ 26 для второго контролируемого узлаг третьего элемента ИЛИ 25 и четвертого сумматора 30 . по модулю два для третьего контролируемого узла, а также элементов управления - второго элемента ИЛИ 35, триггера 36блокировки элемента И 38 и второй группы элементов И 31 и 32.

Блок 7 контролируется следующим образом.

Выходы блока 7,,содержащие четное число единиц заводятся на первый элемент ЦЛИ 10, а выходы блока 7 и элемента ИЛИ 10 заводятся на третий сумматор 17 по модулю два. При правильной работе блока 7 выходной сигнал и сигнал с первого элемента ИЛИ 10 содержит нечетное число единиц. В противном случае на выходе третьего сумматора 17 по модулю два появится сигнал отказа.

Аналогично контролируется блок 23 элементом ИЛИ 25 и сумматором 30. На третий элемент ИЛИ 25 заводятся

выходы блока 23, содержащие четное число единиц.

Для контроля второго контролируемого узла выходы дешифратора 20 делятся на две группы, соответствующие кодам микрокоманд с четным и нечетным числом единиц. Первая группа выходов 1 и 2 подключается ко входам первого сумматора 21 по модулю два, а вторая 3 и 4 - ко входам второго сумматора 22 по модулю два.

o

Узел 16 формирования признака четности в зависимости от кода очередной микрокоманды, поступающего на входы 8 и 9, устанавливают по первому синхроимпульсу триггер 19 призна5ка в единицу, если число единиц в коде микрокоманды нечетно, и в нуль, если число единиц четно. Выходы первого 21, второго 2 сумматоров по модулю два и триггера 19 признака за0водятся .на узел 24 сравнения.

Работоспособному состоянию второго контролируемого узла соответствуют единичный.сигнал на выходе узла 24 сравнения, который появляется при поступле.нии на его входы комбинаций

5 сигналов 010 или 101, с выходов триггера 19 признака, первого 21 и второго 22 сумматоров по модулю два соответственно, в противном случае сигнал на выходе узла 24 сравнения

0 отсутствует и элемент НЕ 26 формируе.т сигнал отказа второго контролируемого узла.

Триггер 36 блокировки при поступлении сигналов отказа через второй элемент ИЛИ 35 блокирует выдачу сигналов микроопераций и работу автомата.

Средства диагностики отказов включают сдвигающий регистр 39, счетчик 40 циклов, блок 41, узлы 42 дешифрации неисправностей и регистрации 43.

По информации, записанной в сдвигающий регистр 39 и счетчик 40 циклов, блок 41 определяет номер выполняемого цикла и формирует на своем выходе коды элементов (групп элементов J соответствующих узлов автомата, участвующих в выполнении данного цикла. Узел 42 дешифрации неисправностей при появлении сигналов отказов на его втором- четвертом входах передает на узел 43 регистрации коды отказавших элементов соответствующих контролируемых узлов. . .

Микропрограммное устройство управления с контролем работает следующим Образом.

По синхроимпульсу на первом вхоце 15 синхронизации код очередной операции переписывается из первого регистра 12 через первую группу элементов И 13 и 14 во второй регистр 18. По синхроимпульсу на втором вхое 37 синхронизации, проходящему через открытый элемент и 38, на одном из выходов дешифратора 20 появляется сигнал. По этому сигналу блок 28 формирует на выходах 27 и 28 сигналы микроопераций, которые через вторую группу элементов И 31 и 32 поступают на выходы 33 34 устройства. Одновременно блок 7 в зависимости от зн чений логических условий на входах 5 и 6 формирует на-выходах 8 и 9 код очередной микрокоманды, который зап сывается в первый регистр 12, Этот код по синхроимпульсу на входе 15 переписывается во второй регистр 18 и работа автомата продолжается аналогично описанному. Параллельно с микропрограммным устройством управления функционируют средства контроля и диагностики. По синхроимпульсам на втором входе 37 синхронизации проходящим через элемент И 38, в сдвигающий регистр. 39 записывается значение очередного проверяемого логического условия, а в счетчик циклов 40 доба ляется единица. По информации, записанной в сдвигающем регистре 39 и счетчике 40 циклов, блок 41 формирует коды элементов (групп элемен тов), которые участвуют в выполнении данного цикла. При отсутствии сигналов отказа на выходе средств конт роля информации из блока 41 узлом 45 дешифрации неисправностей не дешифрируется и на узел регистрации 43 не проходит.; При появлении сиг нала отказа (например, на выходе элемента НЕ 26j через второй элемен ИЛИ 35 триггер 36 блокировки устанавливается в единицу, блокируя выд чу сигналов микроопераций через вто рую группу элементов И 31 и 32 и поступление синхроимпульсов оо второго входа 37 синхронизации устройс ва через элемент И 38 на дешифратор 20, сдвигающий регистр 39 и счетчик 40. Одновременно код элементов, участвовавших в выполнении цикла, поступает на узел 42 дешифрации неисправностей, который передает на регистрацию в узел 43 код отказавшего элемента (группа элементов), принадлежащего узлу, средства контроля которого сформировали сигнал отказа (в данном случае отказавший элемент (группа элементов) принадлежит второму контролируемому узлу На фиг. 2 иллюстрируется процесс определения отказавшего элемента. Средства контроля второго контролируемого узла уменьшают множество подозреваемых элементов домножества М2. Блок 41 формирует код множества элементов Мц-j) . Узел 42 дешифрации неисправностей дешифрирует отказавший элемент (группу элементов) и передает его на регистрацию. Это позволяет однозначно определить .отказавший элемент (группу элементов; и после устранения от-каза продолжить выполнение микропрограммы, начиная из состояния, в котором возник отказ. Таким образом, в предлагаемом микропрограммном устройстве управления отказ локализуется с точностью до элемента (группы .элементов) . Это дает возможность сократить время и повысить эффективность восстановления работоспособности микропрограммного устройства управления с контролем и расширить область его применения. изобретения Формула Микропрограммное устройство управлен1 я с контролем, содержащее дешифратор, первая группа выходов которого соединена с первыми группами входов кода микрокоманд первого и второго блоков памяти и с группой входов первого сумматора по модулю два, вторая группа выходов дешифратора соединена со вторыми группами входов кода Микрокоманд первого и второго блоков памяти и с группой входов второго сумматора по модулю два, группа входов логических условий первого блока памяти соединена с группой входов логических условий устройства, первая группа выходов первого блока памяти соединена с группой- информационных входов первого регистра, группами входов узла формирования признака четности и третьего сумматора по модулю два, вход которого через первый элемент ИЛИ соединен со второй группой выходов первого блока памяти, а выход третьего сумматора по модулю два - с первым входом второго элемента ИЛИ, второй вход которого через элемент НЕ соединен с выходом узла сравнения, первый вход которого через триггер признака соединен с выходом узла формирования признака четности, вход которого соединен с первым входом синхронизации устройства и первыми .входами элементов И первой группы, .вторые входы которых соединены с соответствующими выходами первого регистра, а выходы элементов И первой группы соединены с соответствующими информационными входами второго регистра, группа разрядных выходов которого соединена с группой входов дешифратора выходы первого и второго сумматоров по модулю два соединены соответственно со вторым и третьим входами узла сравнения, первая группа выходов второго блока памяти соединена с группой входов четвертого сумматора по модулю два, вход которого через третий элемент ИЛИ соединен со второй группой выходов второго блока памяти/ а выход четвертого сумматора по модулю два с третьим входом второго элемента ИЛИ /отличающееся тем, что, с целью повышения глубины диагностирования, оно дополнительно содержит третий блок памяти сдвигающий регистр, счетчик циклов, узел дешифрации неисправностей, узел регистрации, вторую группу элементов И триг гер блокировки и элемент и, причем первый вход элемента И соединен со вторым входом синхронизации устройст ва, а выход элемента И соединен со входами дешифратора, счетчика циклов и сдвигающего регистра, группа вхоцов которого соединена с группой входов логических условий устройства выходы сдвигающего регистра и счетчика циклов соединены соответственно с первым и вторым входами третьего блока памяти, выход которого соединен с первым входом узла дешифрации неисправностей, второй вход которого соединен с выходом третьего сумматора по модулю два, третий вход узла дешифрации неисправностей соеди иен с выходом элемента НЕ, четвертый вход соединен с выходом четвертого сумматора по мoдyJпo два, а выход узла дешифрации неисправностей соединен «|jo входом узла регистрации, выход ВТОРОГО элемента ИЛИ соединен с единичным входом триггера блокировки, tienoR выход которого соединен со BTopftJM входом элемента И и первыми входами элементов И второй группы, вторыевходы которых соединены с первой группой выходов второго блока пймяти, а выходы элементов И второй группы - с группой выходов микроопераций устройства. Источники информации, принятые во внимание при эксЛертизе 1.Авторское свидетельство СССР № 598079, кл. G Об F- 11/00, 1978. 2.Тюрин И.В. О построении самоконтролирующегося микропрограммного автомата специального вида. Сб. Современные проблемы управления М., Наука, 1974, с. 132 рис. 4 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с самоконтролем | 1985 |

|

SU1247871A1 |

| Микропрограммное устройство управления с контролем переходов | 1981 |

|

SU985787A1 |

| Устройство для восстановления информации цифровых вычислительных машин | 1982 |

|

SU1027728A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

Авторы

Даты

1981-01-23—Публикация

1979-01-10—Подача