триггеров соответственно, нулевые илходыкоторых соединены с третьими входами, соответственно второг о и первого элементов И и с прямым и инверсным входами первой и второй групп входов соответственно первого и второго блоков элементов И-ИЛИ, выходы которых соединены с группой адресных входов соответственно первого и второго блоков памяти, первая группа выходов первого и второго регистров соединена с вторыми входами первой группы входов сротвественно второго и первого блоков элементов И-ИЛИ, вторая группа выходов первого и второго регистров соединена с вторыми вхрдами второй группы входов соответственно второг и первого блоков элементов И-ИЛИ, нулевые выходы первого и второго триггеров соединены со счетными входами соответственно пятого и шестого триггеров, нулевые выходы которых соединены соответственно с первым ,и вторым тактовыми входами устройства, нулевые выходы пятого и шетого триггеров соединены с; четвертыми входами соответственно второго и первого элементов И.

2. Устройство по п. 1, о т л и чающее ся тем, что блок памяти содержит накопитель, сумматор по модулю два, элемент задержки, первую и вторую группы элементов И, первый и второй элементы И,причем управляющий вход 1итывания блока соединен с входом считывания накопителя и через элемент задержки с входом первого элемента И, первым входом второго элемента И и выходом считывания блока, адресные входы блока памяти соединены с адресными входами накопителя, операционные и адресные выходы которого соединены с первой и второй группалш информа г ционных входов сумматора по модулю два и первыми входами элементов И первой и второй групп соответственно, выход контрольного разряда накопителя соединен с входом сумматора п модулю два, выход которого соединен с инверсным входом первого и вторым входим второго элемента и, выход первого элемента И является выходом неисправности блока, выход второго элемента И соединен с вторыми входами элементов И первой и второй групп и является выходом исправности блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU888120A1 |

| Микропрограммное устройство управления | 1981 |

|

SU993261A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Реконфигурируемое устройство с программным управлением | 1981 |

|

SU1007108A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1309024A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1980 |

|

SU938283A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

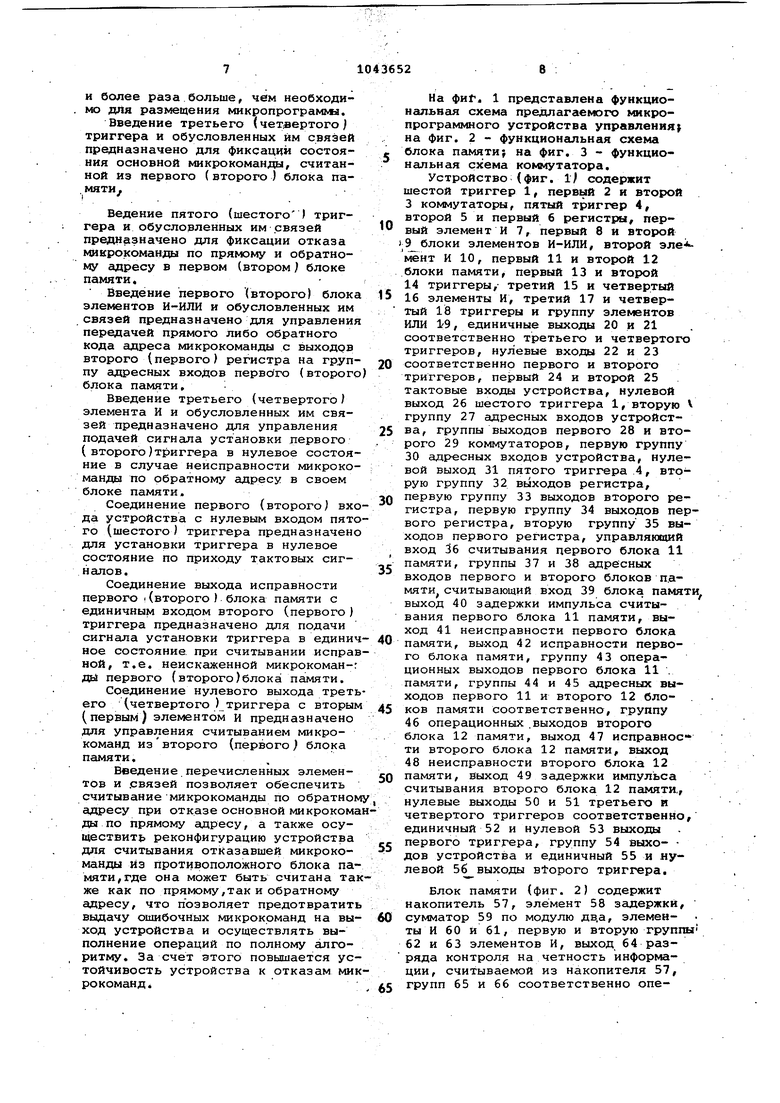

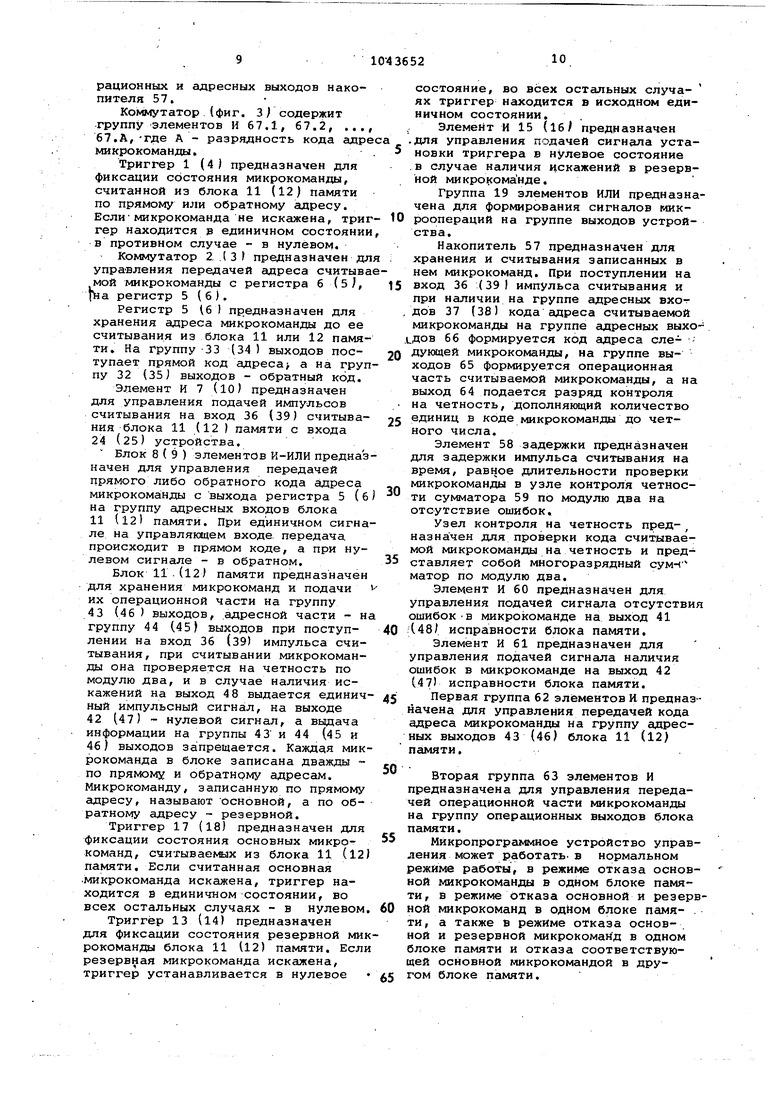

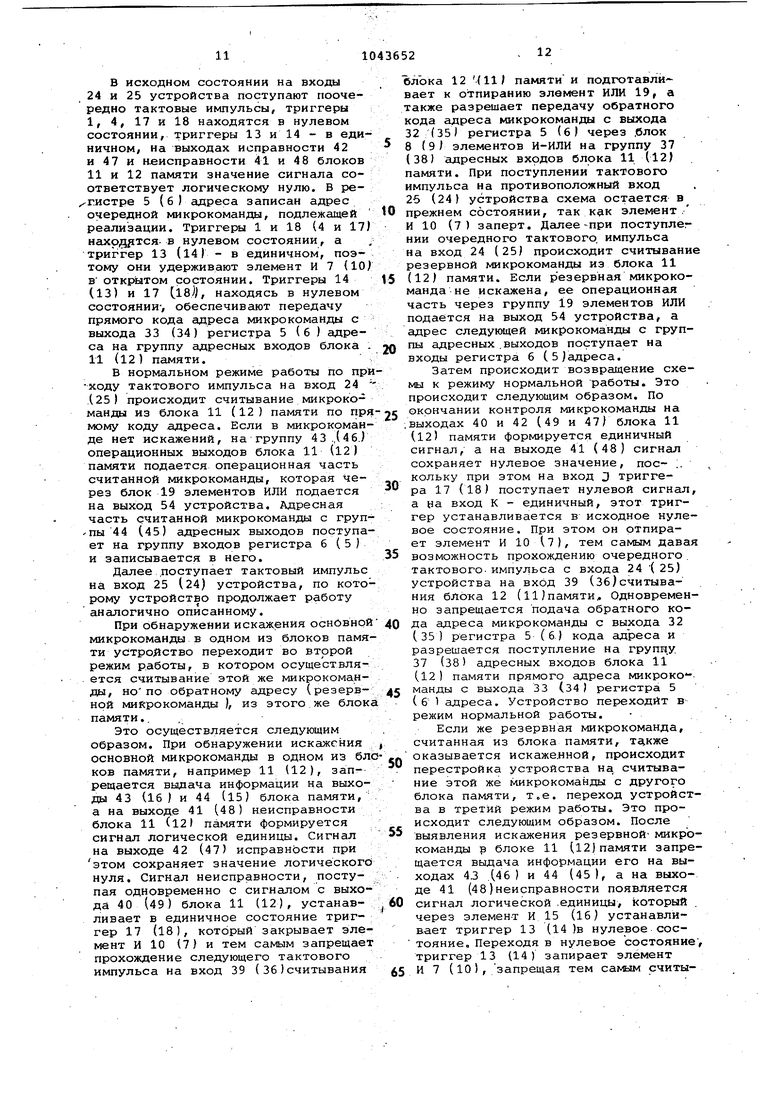

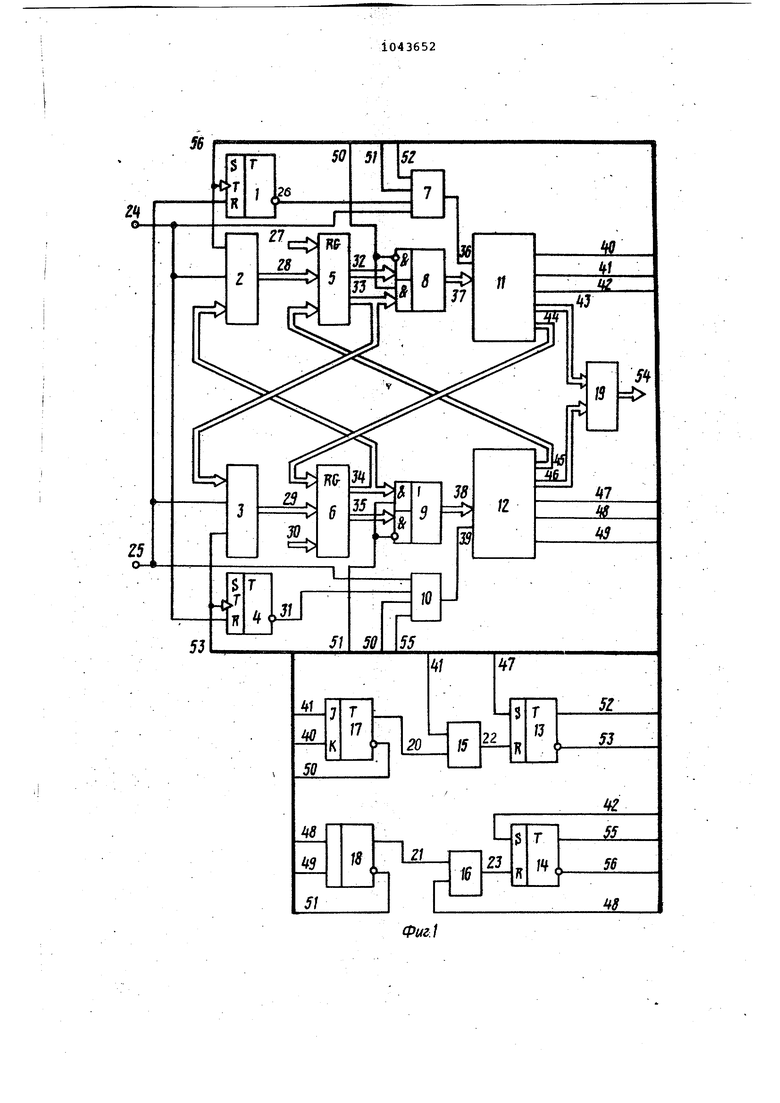

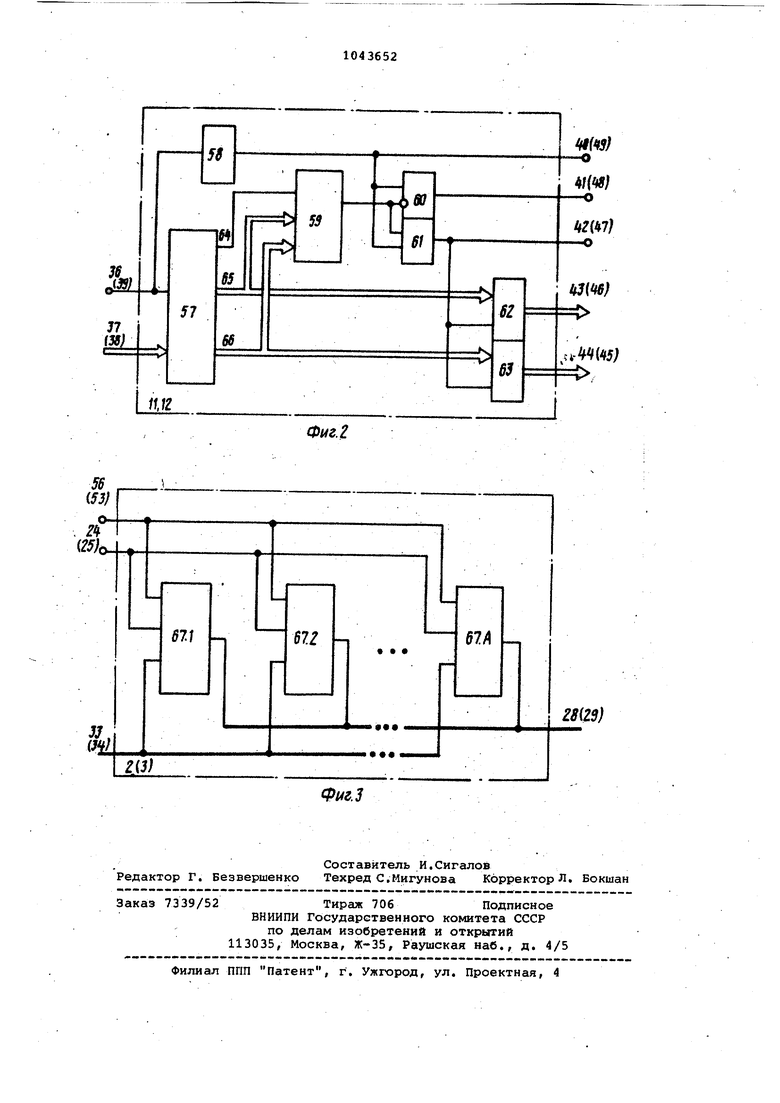

Изобретение относится к вычислительной технике и может быть исполь зовано в устройствах управления ЭВМ с повышенной надежностью, Известны микропрограммные устрой ства управления, содержащие два блока памяти, два регистра адреса, два коммутатора, два триггера, два элемента- И и группу элементов ИЛиС и С2. Недостатком данных устройств является низкая устойчивость к отка зам, вызванная отсутствием возможности автоматического восстановления работоспособности при отказе какого-либо элемента устройства, Известно также перестраивамое микропрограммное устройство управле ния, содержащее два блока памяти, два регистра адреса, два .коммутатора, два триггера, два элемента И и .группу элементов ИЛИ f3 J, Недостатком такого устройства яв ляется низкая устойчивость к отказам, обусловленная невозможностью автоматического восстановления рабо тоспособности устройства при наличи отказа хотя бы в одной микрокоманде первогр и хотябы в одной микрокоманде второго блока памяти. Такими же причинами объясняется наличие подобного недостатка и в микропрограммном устройстве управления, содержащем два блока памяти, два регистра адреса, два коммутатора j три триггера, две группы элементов И-ИЛИ, два коммутатора, два дополнительных регистра, три элемента задержки, группу элементов ИЛИ, пять элементов ИЛИ и шестнадцать элементов И, Известно также микропрограммное устройство управления, содержащее четыре блока памяти, четыре регистра, четыре триггера, два ко1« мутатора, группу элементов И-ИЛИ, группу элементов ИЛИ, десять элементов И и шесть элементов ИЛИ 4j, Недостатком этого устройства является низкая устойчивость к отказам, обусловленная невозможностью автоматического восстановления работоспособ1ности устройства при наличии отказа в одноименных микрокомандах основного и противоположного блока памяти, а также относительно высокой сложностю контрольно-переключающего -оборудования устройства. Известно также микропрограммное устройство управления, содержащее два блока памяти, два регистра адреса, два коммутатора, деиЫфратор, две группы элементов ИЛИ, шесть элементов И, две ГРУППЕ элементов И и три элемента ИЛИ fsj. Недостаток данного устройства низкая устойчивость к отказам. Это вызвано тем, что, хотя в устройстве и обеспечивается устойчивость к отказам регистров адреса и микрокоманд, однако для потери работоспособности устройства достаточно нали чия хотя бы одной отказавшей микрокоманды в первом и втором блоках памяти одновременно. Другой причиной снижения устойчивости устройств к отказам является сравнительно высокая сложность контрольно-переключаю щего оборудования устройства. Наиболее близким к изобретению по технической сущности и достигаемому эффекту является перестраиваемое микропрограммное устройство управления, которое содержит два блока памяти,- два регистра адреса, два триггера, два элемента И и группу элементов ИЛИ, причем группа адресных выходов первого и второго блока памяти соединена с первой группой информационных входов соответственно первого и второго регистров, одноименные выходы группы информацион ных выходов первого и второго блоко памяти соединены соответственно с первыми и вторыми входами блока эле ментов ИЛИ, группа выходов которого является выходом устройства, группа выходов первого коммутатора соединена с второй группой информационных входов второго регистра, первая группа выходов которого через второ коммутатор соединена с второй группой информационных входов первого регистра, первая группа выходов кот рого соединена с группой информацио ных входов первого коглмутатора, пер вый и второй входы устройства сое- динены с первыми входами первого и второго коммутатора соответственно, а также с первыми входами соответственно первого и второго элементов И, выходы которых соединены с входами считывания первого и второго блоков памяти, единичные выходы пер вого и второго триггеров соединенй с вторыми входами соответственно пе вого и второго элементов И, нулевые выходы первого и второго триггеров соединены с вторыми входами соответ ствен()о второго и первого коммутато ров . Недостатком известного устройств является низкая устойчивость к отказам, вызванная тем, что при отказ какой-либо микрокоманды в одном бло ке памяти устройство не может продолжить выполнение микропрограммы, а должно-прекратить ее реализацию и перейти к другой микропрограмме, которая записана полностью в противоположном блоке памяти и задает усеченный алгоритмвыполнения операции. Неисправный блок памяти при этом отключается. Если же отказ Микрокоманды происходит и в другчэм блоке памяти, он также-отключается, и устройство вообще прекращает функ- ционирование. В системах, не допус- : кающих их восстановление в процессе функционирования, такая ситуация приводит к невыполнению поставленной задачи и отказу всей система. В то же время, в устройстве может быть обеспечена возможность продолжения функционирования, причем даже не по усеченному алгоритму дающему менее точные результаты, а по основному алгоритму, без перезапуска выполнения микропрограммы. Эта возможность может быть реализована путем использования в устройстве идентичных блоков памяти, в каждом из которых каждая микрокоманда записана дважды: по прямому и по обратному (инверсному ) адресам, а также путем обеспечения восстановления . работоспособности устройства при отказе какой-либо микрокоманды путем считывания ее по обратному адресу в своем блоке памяти или по прямому или обратному адресу в противополож- . ном блоке памяти. Цель изобретения - повышение .надежности устройства. Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее первый и второй блоки памяти, первыйи второй регистры адреса, два первый и второй триггеры, первый и второй элементы И и группу элементов ИЛИ, причем группа адресных выходов первого и второго блоков памяти соединена с первой группой информацион- : ных входов соответственно первого и второго регистров, группа операционных выходов первого и второго блоков, памяти соединены соответственно с первым и вторым входами соответствующего элемента ИЛИ группы, выходы элементовИЛИ группы являются группой выходов устройства, группа выходов первого .коммутатора соединена с второй группой информационных входов второго регистра, первая группа выходов которого соединена с группой информационных входов второго коммутатора, группа выходов которого соединена с второй группой информационных входов первого регистра,, первая группа выходов которого соединена с второй группой информационных входов первого коммутатора, первый и второй тактовые входы устройства соединеиы с тактовыми входамк .первого и второго коммутаторов соответственно :и с первыми входами соответственно первого и второго элe feнтoв И, выходы которых соединены с управляющими входами считывания первого и второго блоков памяти соответственно, единичные выходы первого и второго триггеров соединены с вторыми входа/ИИ соответственно первого и второго элементов И, нулевые выходы первого и второго триггеров соединены с управлянвдими входами соответ ственно второго и первого комммутаторов, первая и вторая группы адресных входов устройства-соединены с третьими группами информационных .входов соответственно -первого и вто рого регистров, введены четыре триг гера, два элемента И и два блока элементов И-ИЛИ, причем выходы задержки импульсов считывания первого и второго блоков памяти соединены с нулевыми входами соответственно третьего и -четвертого триггерюв, единичные входы которых соединены .с выходами неисправности соответственно первого и второго блбков памяти, выходы неисправности второго и первого блоков памяти соединены с единичными входами соответст-. венно первого и второго триггеров, нулевые входы которых соединены с выходами третьего и четвертого элементов И соответственно, выходы неисправности первого и второго блоко памяти соединены с первыми входами третьего и четвертого элементов И соответственно, вторые входы которы соединены с единичными выходами . третьего и четвертого триггеров соо ветственно, нулевые выходы которых соединены с третьими входами соответственно второго и первого элемен тов И и с прямым и инверсным входами первой и второй групп входов соответственно первого и второго блок элементов И-ИЛИ, выходы которых сое динены с группой адресных входов соответственно первого и второго блоков памяти, первая группа выходов первого и второго регистров сое динена с вторыми входами первой гру пы входов соответственно второго и первого блоков элементов И-ИЛИ, вторая группа выходов первого и вто рого регистров соединена с вторыми входами второй группы входов соответственно второго и первого блоков элементов И-ИЛИ, нулевые выходы пер вого и второго триггеров соединены со счетными входами соответственно пятого и шестого триггеров, нулевые выходы которых соединены соответственно с первым и вторым тактовыми, входами устройства, нулевые- выходы ПЯ.ТОГС1, и шестого триггеров соединены с четвертыми входами соответственно второго и первого элементоЪ И. , . . Кроме того, блок памяти содержит Накопитель, суммйтор по модулю два, элемент задержки, первую и вторую группы элементов И, первый и второй элементы И, причем управляющий вход считывания .блока соединен с входом считывания накопители и через элемент задержки с входом первого элемента И, первым входом второго элемента И и выходом считывания блока , адресные входы блока памяти соединены с адресными входами наКопитёля, операционные и адресные выходы которого соединены с первой и второй группами информационных входов сумматора по модулю два, и первыми входами элементов И первой и второй групп соответственно, выход контрольного разряда накопителя соединен с входом сумматора по модулю дйа, выход которого соединен с инверсйым входом первого и вторым входом второго элемента И, выход первого элемента И является выходом неисправности блока, выход второго элемента И соединен с вторыми входами элементов И первой и второй групп и является выходом исправности блока памяти. Сущность изобретения состоит в повышении устойчивости устройства к отказам микрокоманд за счет использования идентичных блоков памяти, в каждом из которых каждая микрокоманда записана дважды - по прямому и обратному (инверсному) коду адреса, и обеспечения восстановления работоспособности устройства при отказе основной микрокоманды, записанной по прямому., адресу, путем считывания ее по обратному адресу из того же блока памятиj при отказе микрокоманды, считанной по обратному адресу, - путем реконфигурации устройства и считывания этой микрокоманды из противоположного блока памяти по прямому адресу; в случае отказа и этой микрокоманды - путем считывания ее по обратному адресу из противоположного блока памяти. Это позволяет существенно расширить множество неисправностей, при которых устройство сохраняет работоспособность. При этом не требуется осуществлять перезапуск микропрограммы и использовать усеченный алгоритм выполнения -операции, который обеспечивает менее точные результаты операции. Такой метод почти не требует дополнительного оборудования по сравнению с известным устройством при построении блоков памяти на стандартныхЪольших интегральных схемах, в которых количество храниких слов в отдельных случаях в два и более раза больше, чем необходимо для размещения микропрограм1«л. Введение третьего (четвертого ) триггера и обусловленных им связей предназначено для фиксаций состояния основной микрокоманда f считанной из первого (второго j блока памяти.. | . . Ведение пятого {шестого ) триггера и обусловленных им связей предназначено для фиксации отказа микрокоманды по прямому и обратному адресу в первом (втором) блоке памяти. Введение первого (второго) блока элементов И-ИЛИ и обусловленных им связей предназначено для управления передачей прямого либо обратного кода адреса микрокоманды с выходов второго (первого) регистра на группу адресных входов первсУго (второго блока памяти, Введение третьего (четвертого) элемента И и обусловленных им связей предназначено для управления подачей сигнала установки первого ( второго)триггера в нулевое состояние в случае неисправности микрокоманды по обратному адресу в своем блоке памяти. Соединение первого (второго) вхо да устройства с нулевым входом пято го (шестого) триггера предназначено для установки триггера в нулевое состояние по приходу тактовых сигналов. Соединение выхода исправности первого I (второго ) блока памяти с единичным входом второго (первого ) триггера предназначено для подачи сигнала установки триггера в едини ное состояние, при считывании испра ной, т.е. неискаженной микрокомандй первого (второго)блока памяти. Соединение нулевого выхода трет его (четвертого ) триггера с вторы (первым) элементом И предназначено для управления считыванием микрокоманд извторого (первого ) блока памяти. Введение перечисленных элементов и .связей позволяет обеспечить считывание микрокоманды по обратно адресу при отказе основной микроком ды по прямому адресу, а также осуществить реконфигурацию устройства для считывания отказавшей микрокоманды из противоположного блока па мяти, где она может быть считана та же как по прямому,так и обратному адресу, что позволяет предотвратит выдачу ошибочных микрокоманд на вы ход устройства и осуществлять выполнение операций по полному алгоритму. За счет этого повышается ус тойчивость устройства к отказам ми рокоманд. На фиГ. 1 представлена функциональвая схема предлагаемого микропрограммного устройства управления} на фиг. 2 - функционгшьная схема блока Пс1мяти; на фиг. 3 - функциональная схема коммутатора. Устройство (фиг. 1/ содержит шестой триггер 1, первый 2 и второй 3 коммутаторы, пятый триггер 4, второй 5 и первый б регистры, первый элемент И 7, первый 8 и второй 9 блоки элементов И-ИЛИ, второй эле кюнт И 10, первый 11 и второй 12 блоки памяти, первый 13 и второй 14 триггеры, третий 15 и четвертый 16 элементы И, третий 17 и четвертый 18 триггеры и группу элементов ИЛИ 19, единичные выходы 20 и 21 соответственно третьего и четвертого триггеров, нулевые входы 22 и 23 соответственно первого и второго триггеров, первый 24 и второй 25 тактовые входы устройства, нулевой выход 26 шестого триггера 1, вторую V группу 27 адресных входов устройства, группы выходов первого 28 и второго 29 коммутаторов, первую группу 30 адресных входов устройства, нулевой выход 31 пятого триггера .4, вторую группу 32 выходов регистра, первую группу 33 выходов второго регистра, первую группу 34 выходов первого регистра, вторую группу 35 выходов первого регистра, управляющий вход 36 считывания первого блока 11 памяти, группы 37 и 38 адресных входов первого и второго блоков памяти считывающий вход 39 блока памяти выход 40 задержки импульса считывания первого блока 11 памяти, выход 41 неисправности первого блока памяти, выход 42 исправности первого блока памяти, группу 43 операционных выходов первого блока 11 . памяти, группы 44 и 45 адресных выходов первого 11 и второго 12 бло- . ков памяти соответственно, группу 46 операционных .выходов второго блока 12 памяти, выход 47 исправности второго блока 12 памяти, выход 48 неисправности второго блока 12 памяти, выход 49 задержки импульса считывания второго блока 12 памяти., нулевые выходы 50 и 51 третьего и четвертого триггеров соответственно, единичный 52 и нулевой 53 выходы первого триггера, группу 54 выхо- дов устройства и единичный 55 и нулевой 56 выходы Btoporo триггера. Блок памяти (фиг. 2) содержит накопитель 57, элемент 58 задержки, сумматор 59 по модулю дв,а, элементы И 60 И 61, первую и вторую группы 62 и 63 элементов И, выход 64 разряда контроля на четность информации, считываемой из накопителя 57, групп 65 и 66 соответственно oneрационных и адресных выходов накопителя 57.

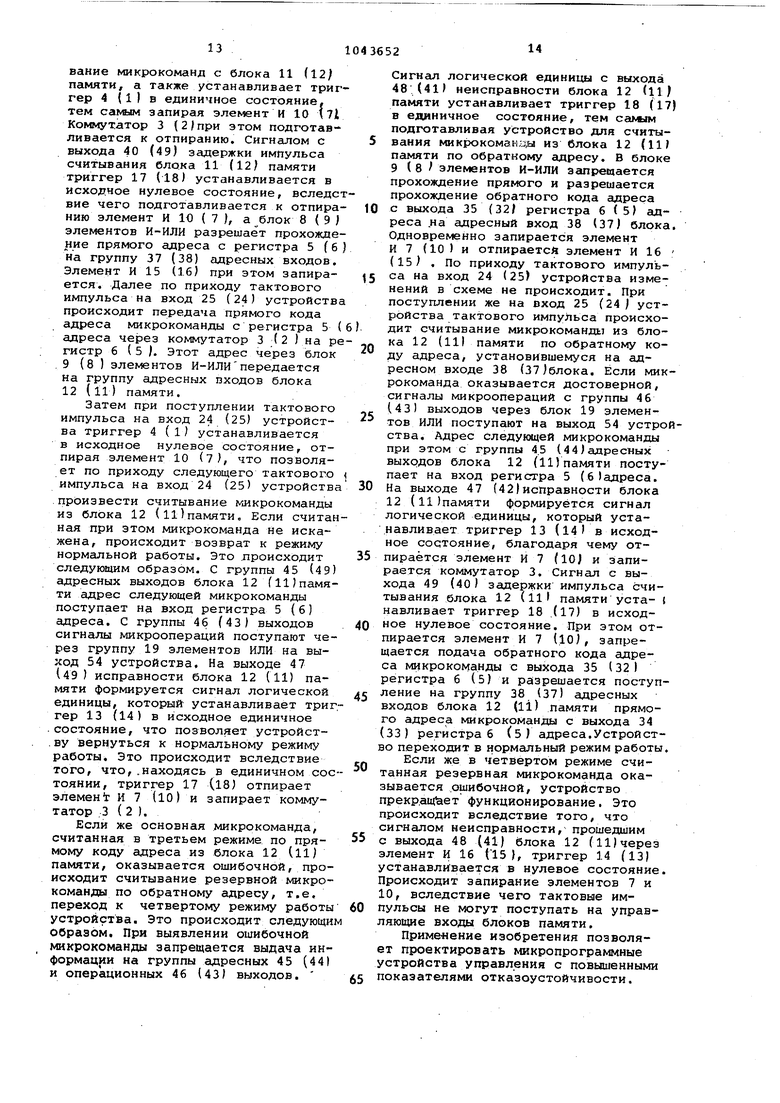

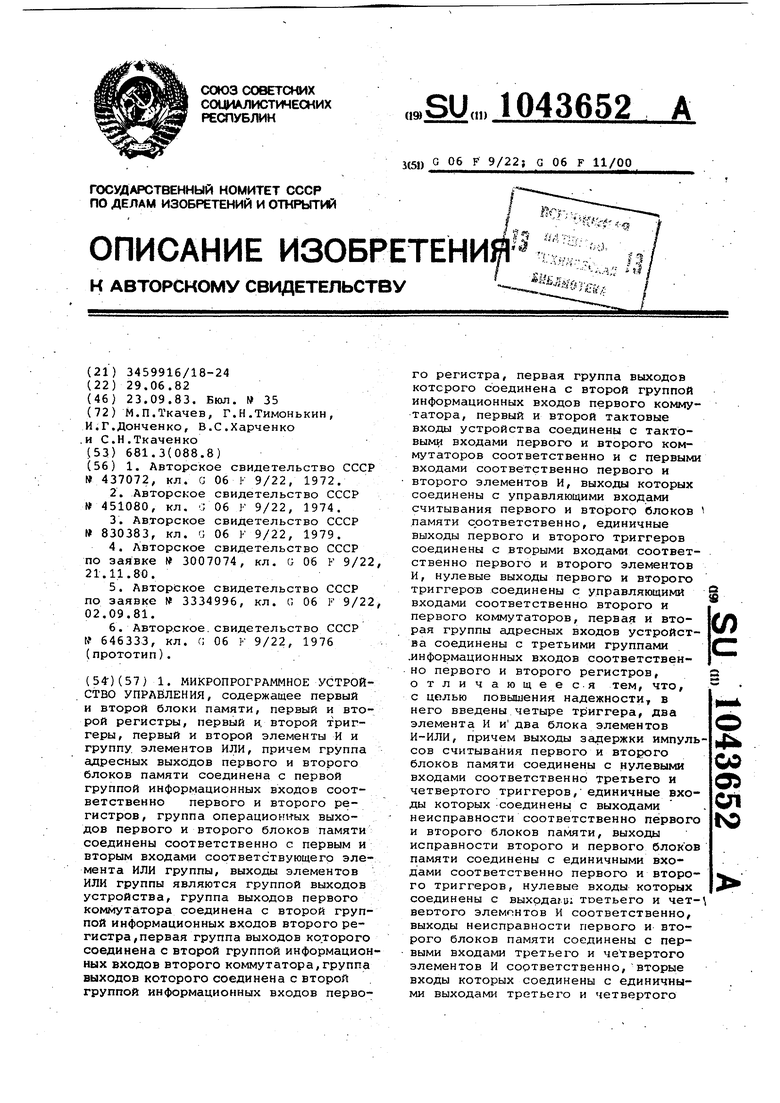

Кокмутатор (фиг. 3) содержит группу элементов И67.1, 67.2, ..., 67.А, -где А - разрядность кода адрес микрокоманды..

Триггер 1 (4| предназначен для фиксации состояния микрокоманды, считанной из блока 11 (12) памяти по прямому или обратному адресу. Если-микрокоманда не искажена, триггер находится э единичном состоянии в противном случае - в нулевом.

Коммутатор 2. .( 3 I предназначен для управления передачей адреса считываемой микрокоманды с регистра 6 (5, на регистр 5(6),

Регистр 5 (6 ) предназначен для хранения адреса микрокоманды до ее считывания из блока 11 или 12 памяти.. На группу 33 (34 ) выходов поступает прямой код адреса а на группу 32 (35) выходов - обратный код.

Элемент И 7 (Ю) предназначен для управления подачей импульсов считывания на вход 36 (39) считывания блока 11 (12 ) памяти с входа 24 (25) устройства.

Блок 8(9) элементов К-ИЛИ предназначен для управления передачей прямого либо обратного кода адреса микрокома:нды с выхода регистра 5 (6) на группу адресных входов блока 11 (12) памяти. При единичном сигнале на управлякхцем входе, передача происходит в прямом коде, а при нулевом сигнале - в обратном.

Блок 11 (12) памяти предназначен для хранения микрокоманд и подачи их операционной части на группу 43 (46 ) выходов, .адресной части - на группу 44 (45) выходов при поступлении на вход 36 (39) импульса считывания, при считывании микрокоманды она проверяется на четность по модулю два, и в случае наличия искажений на выход 48 выдается единичный импульсный сигнал, на выходе 42 (47) - нулевой сигнал, а выдача информации на группы 43 и 44 (45 и 46) выходов за прещается. Каждая микрокоманда в блоке записана дважды по прямому и обратному адресам. Микрокоманду, записанную по прямому адресу, называют основной, а по обратному адресу - резервной.

Триггер 17 (18) предназначен для фиксации состояния основных микрокоманд, считываеь«дх из блока 11 (12) памяти. Если считанная основная микрокоманда искажена, триггер находится в единичном состоянии, во всех остальных случаях - в нулевом.

Триггер 13 (14) предназначен для фиксации состояния резервной микрокоманды блока 11 (12) памяти. Если резервная микрокоманда искажена, триггер устанавливается в нулевое

состояние, во всех остальных случаях триггер находится в исходном единичном состоянии.

Элемент И 15 (16/ предназначен для управления подачей сигнала установки триггера в нулевое состояние в случае наличия искажений в резервной микрокоманде.

Группа 19 элементов ИЛИ предназначена для формирования сигналов микроопераций на группе выходов устройства.

Накопитель 57 предназначен для хранения и считывания записанных в нем микрокоманд. При поступлении на вход 36 (391 импульса считывания и при наличии на группе адресных вхот дов 37 (38) кода адреса считываемой микрокоманды на группе адресных выхоДoв 66 формируется код адреса еледующей микрокоманды, на группе выходов 65 формируется операционная часть считываемой микрокоманды, а на выход 64 подается разряд контроля на четность, дополняющий количество единиц в коде микрокоманды до четного числа.

Элемент 58 задержки предназначен для задержки импульса считывания на время, равное длительности проверки микрокоманды в узле контроля четности сумматора 59 по модулю два на отсутствие ошибок.

Узел контроля на четность пред-, назначен для проверки кода считываемой микрокоманды на четность и представляет собой многоразрядный сум-с матор по модулю два.

Элемент И 60 предназначен для управления подачей сигнала отсутствия ошибокВ микрокоманде на выход 41 (48/ исправности блока памяти.

Элемент И 61 предназначен для управления подачей сигнала наличия ошибок в микрокоманде на выход 42 (47) исправности блока памяти.

Первая группа 62 элементов R предназачена для управления передачей кода адреса микрокоманды на группу адресных выходов 43 (46) блока 11 (12) памяти.

Вторая группа 63 элементов И предназначена для управления передачей операционной части микрокоманды на группу операционных выходов блока памяти.

Микропрограммное устройство управления может работать-в нормальном ежиме работы, в режиме отказа основной микрокоманды в одном блоке памяти, в режиме отказа основной и резервной микрокоманд в одйом блоке памя- . ти, а также в режиме отказа основной и резервной микрокоманд в одном блоке памяти и отказа соответствующей основной микрокомандой в другом блоке памяти. В исходном состоянии на входы 24 и 25 устройства поступают поочередно тактовые импульсы, триггеры 1, 4, 17 и 18 находятся в нулевом состоянии, триггеры 13 и 14 - в еди ничном, на выходах исправности 42 и 47 и неисправности 41 и 48 блоков 11 и 12 памяти значение сигнала соответствует логическому нулю. В ре гистре 5 {6 ) сщреса записан адрес очередной микрокоманды, подлежащей реализации. Триггеры 1 и 18 (4 и 17 иахрдртся- в нулевом состоянии, а триггер 13 (14) - в единичном, поэтому они удерживают элемент И 7 (10 В открытом состоянии. Триггеры 14 (13) и 17 (.18)), находясь в нулевом состоянии-, обеспечивают передачу прямого кода адреса микрокоманды с выхода 33 (34) регистра 5(6) адреса на группу адресных входов блока 11 (12) памяти. В нормальном режиме работы по пр ходу тактового импульса на вход 24 .(,25) происходит считывание микрокоманды из блока 11 (12 ) памяти по пр мому коду адреса. Если в микрокоман де нет искажений, на группу 43.,(46.) операционных выходов блока 11 (12) памяти подается операционная часть считанной микрокоманды, которая Через блок 19 элементов ИЛИ подается на выход 54 устройства. Адресная часть считанной микрокоманды с груп Пы44 (45) адресных выходов поступа ет на группу входов регистра 6 (5 ) и записывается в него, Далее поступает тактовый импульс на вход 25 124) устройства, по кото рому устройство продолжает работу аналогично описанному. При обнаружении искажения основно микрокоманды в одном из блоков памя ти устройство переходит во второй режим работы, в котором осуществляется считывание этой же микрокоманды, нопо обратному адресу (резервной микрокоманды ), из этого же блок памяти.. Это осуществляется следующим образом. При обнаружении искажения основной микрокоманды в одном из бл ков памяти, например 11 (12), запрещается выдача информации на выходы 43 (16) и 44 (15) блока памяти, а на выходе 41 (48) н.еисправности блока 11 (12( памяти формируется сигнал логической единицы. Сигнал на выходе 42 (47) исправности при этом сохраняет значение логического нуля. Сигнал неисправности, поступая одновременно с сигнгшом с выхода 40 (49) блока 11 (12), устанавливает в единичное состояние триггер 17 (18), который закрывает элемент И 10 (7) и тем самым запрещает прохождение следующего тактового импульса на вход 39 (36)считывания лока 12 411) памяти и подготавливает к отпиранию элемент ИЛИ 19, а акже разрешает передачу обратного кода адреса микрокоманды с выхода 32 (35) регистра 5 (б) через .блок 8 (9) элементов И-ИЛИ на группу 37 (38) адресных вхрдов блока 11 (12) памяти. При поступлении тактового импульса на противоположный вход 25 (24) устройства схема остается в прежнем состоянии, так элемент. И 10 (7) заперт. Дсшее-при поступлег НИИ очередного тактового, импульса на вход 24 (25) происходит считывание резервной микрокоманды из блока 11 (12) памяти. Если резервная микрокоманда не искажена, ее операционная часть через группу 19 элементов ИЛИ подается на выход 54 устройства, а адрес следующей микрокоманды с группы адресных .выходов поступает на входы регистра 6 (5)адреса. Затем происходит возвращение схемы к режиму нормальной работы. Это происходит следующим образом. По окончании контроля микрокоманды на выходах 40 и 42 (49 и 47) блока 11 (12) памяти формируется единичный сигнал, а на выходе 41 (48) сигнал сохраняет нулевое значение, пос- .. кольну при этом на вход Э триггера 17 (18) поступает нулевой сигнал, а на вход К - единичный, этот триггер устанавливается в исходное нулевое состояние. При этом он отпирает элемент И 10 (7), тем самым давая возможность прохождению очередного, тактового, импульса с входа 24 ( 25) устройства на вход 39 (Зб)считывания блока 12 (11)памяти, Одновременно запрещается подача обратного кода адреса микрокоманды с выхода 32 (35) регистра 5 (б) кода адреса и разрешается поступление на группу 37 (38) адресных входов блока 11 (12) памяти прямого адреса микроко. манды с выхода 33 (34) регистра 5 (б 1 адреса. Устройство переходит в режим нормальной работы. Если же резервная микрокоманда, считанная из блока памяти, та.кже оказывается искаже.нной, происходит перестройка устройства на считывание этой же микрокоманды с другого блока памяти, т.е. переход устройства в третий режим работы. Это происходит следующим образом. После выявления искажения резервной микрокоманды р блоке 11 (12)памяти запрещается выдача информации его на выходах 4.3 .(46 ) и 44 (45 ), а на выходе 41 (48) неисправности появляется сигнал логической .единицы, который через элемен.т И 15 (16) устанавливает триггер 13 (14 )в нулевое состояние. Переходя в нулевое состояние , триггер 13 (14) запирает элемент И 7 (10), запрещая тем самым считывание микрокоманд с блока 11 (12/ памяти, а также устанавливает триггер 4 (1 I в единичное состояние, тем самлн запирая элемент И 10 л7i Коммутатор 3 ( этом подготавливается к отпиранию. Сигналом с выхода 40 (49) задержки импульса считывания блока 11 (12) памяти триггер 17 (18) устанавливается в исходное нулевое состояние, вследствие чего подготавливается к отпиранию элемент И 10 ( 7 ), а блок 8(9/ элементов И-ИЛИ разрешает прохождение прямого адреса с регистра 5 f б ) на группу 37 (38) адресных входов. Элемент И 15 (l6) при этом запирается. Далее по приходу тактового импульса на вход 25 (24) устройства происходит передача прямого кода адреса микрокоманды с регистра 5 ( адреса через коммутатор 3 (2 ) на регистр 6 (5 /. Этот адрес через блок .9 (8 ) элементов И-ИЛИпередается на группу адресных пходов блока 12 (11) памяти.

Затем при поступлении тактового импульса на вход 24 (25) устройства триггер 4(1) устанавливается в исходное нулевое состояние, отпирая элемент 10 (7), что позволяет по приходу следующего тактового импульса на вход 24 (25) устройства

произвести считывание микрокоманды из блока 12 (11)памяти, Если считанная при этом микрокоманда не искажена, происходит возврат к режиму нормальной работы. Это .происходит следующим образом. С группы 45 (49) адресных выходов блока 12 (11)памяти адрес следующей микрокоманды поступает на вход регистра 5 (6) адреса. С группы 46 (43) выходов сигналы микроопераций поступают через группу 19 элементов ИЛИ на выход 54 устройства. На выходе 47 (49 ) исправности блока 12 (11) памяти формируется сигнал логической единицы, который устанавливает триггер 13 (14) в исходное единичное .состояние, что позволяет устройст.ву вернуться к нормальному режиму работы. Это происходит вследствие того, что,.находясь в единичном состоянии, триггер 17 (18) отпирает элемен г И 7 (Ю) и запирает коммутатор ,3(2).

Если же основная микрокоманда, считанная в третьем режиме по прямому коду адреса из блока 12 (11) памяти, оказывается ошибочной, происходит считывание резервной микрокоманды по обратному адресу, т.е. переход к четвертому режиму работы устройства. Это происходит следующим образом. При выявлении ошибочной микрокоманды запрещается выдача информации на группы адресных 45 (441 и операционных 46 (43) выходов.

Сигнал логической единицы с выхода 48 (41) неисправности блока 12 (11 памяти устанавливает триггер 18 (17 в единичное состояние, тем санам подготавливая устройство для считывания кмкрокомакды из блока 12 (11 памяти по обратному адресу. В блоке 9(8 элементов И-ИЛИ запрещается прохождение прямого и разрешается прохождение обратного кода адреса с выхода 35 (32/ регистра 6(5) адреса на адресный вход 38 (37) блока Одновременно запирается элемент И 7 (10 ) и отпирается элемент И 16 (15) . По приходу тактового импульса на вход 24 (25) устройства изменений в схеме не происходит. При поступлении же на вход 25 (24 / устройства тактового импульса происходит считывание микрокоманды из блока 12 (111 памяти по обратному коду адреса, установившемуся на адресном входе 38 (37)блока. Если микрокоманда оказывается достоверной, сигналы микроопераций с группы 46 (43) выходов через блок 19 элементов ИЛИ поступают на выход 54 устроства. Адрес следующей микрокоманды при этом с группы 4.5 (44) адресных выходов блока 12 (11)памяти поступает на вход регистра 5 (6 )адреса. На выходе 47 (421 исправности блока 12 (11)памяти формируется сигнал логической единицы, который уста.навливает триггер 13 (14) в исходное состояние, благодаря чему отпирается элемент И 7 (10) и запирается коммутатор 3. Сигнал с выхода 49 (40) задержки импульса считывания блока 12 (ill памяти устанавливает триггер 18 .(17) в исходное нулевое состояние. При этом отпирается элемент И 7 (.10), запрещается подача обратного кода адреса микрокоманды с выхода 35 (321 регистра 6 (5) и разрешается поступление на группу 38 (37) адресных входов блока 12 (li) памяти прямого адреса микрокоманды с выхода 34 (33) регистра 6 (5 ) адреса.Устройство переходит в нормальный режим работы

Если же в четвертом режиме считанная резервная микрокоманда оказывается .ошибочной, устройство прекр. функционирование. Это происходит вследствие того, что сигналом неисправности, прошедшим с выхода 48 (41) блока 12 (11)через элемент И 16 t15 ), триггер 14 (13) устанавливается в нулевое состояние Происходит запирание элементов 7 и 10, вследствие чего тактовые импульсы не могут поступать на управляющие входы блоков памяти.

Приме«ение изобретения позволяет проектировать микропрограммные устройства управления с повышенными показателями отказоустойчивости.

Фиг.1

56 (53)

, f« (25)(

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1972 |

|

SU437072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1972 |

|

SU451080A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти, первый и второй регистры, первый и | |||

| второй триггеры, первый и второй элементы И и группу, элементов ИЛИ, причем группа адресных выходов первого и второго блоков памяти соединена с первой группой информационных входов соответственно первого и второго регистров, группа операционных выходов первого и второго блоков памяти соединены соответственно с первым и вторым входами соответствующего элемента ИЛИ группы, выходы элементов ИЛИ группы являются группой выходов устройства, группа выходов первого коммутатора соединена с второй группой информационных входов второго регистра, первая группа выходов которого соединена с второй группой информационных входов второго коммутатора,группа выходов которого соединена с второй группой информационных входов первоSU.,., 1043652 А 3 | |||

Авторы

Даты

1983-09-23—Публикация

1982-06-29—Подача