(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля выполнения тестовой программы | 1986 |

|

SU1317442A1 |

| Устройство для группового контроля логических блоков | 1986 |

|

SU1372323A1 |

| Устройство для контроля радиоэлектронных блоков | 1988 |

|

SU1640694A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для тестового контроля временных соотношений | 1985 |

|

SU1260962A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Устройство для контроля электрических цепей | 1985 |

|

SU1270729A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для контроля схем сравнения | 1985 |

|

SU1297057A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

Изобретение относится к устройств для испытания цифровых электронных схем и предназначено для обнаружения ошибок в их работе. Известны устройства для обнаруже ния ошибок в работе отдельных цифровых блоков, построенные на основе сравнения работы испытуемой схемы с эталЪнной схемой или моделью эталон ной схемы f, В качестве модели эталонной схемы используется специализированное вычислительное устройство, реализующее программу испытаний. Задача кон роля цифровых блоков решается в пла не создания высокопроизводительных установок с применением ЭВМ для обе печения контроля в крупносерийном произвсадстве 2, Недостатком устройства является сложность конструкции. Известно устройство отвечающее требОЕ1аниям по простоте конструкции и эксплуатации 3. Однако, поскольку как контролируемый блок, так и контрольное устройство собираются из элементов со сравнимыми надежностямй, то в принципе, сравнимы и вероятности их отказов. Целью изобретения является повышение достоверности контроля исправности цифровых блоков. Поставленная цель достигается тем, что в устройство для контроля цифровых блоков содержащее генератор импульсов, первый кольцевой регистр сдвига, блок индикации, регистр входных комбинаций тестовых сигналов и регистр ответных реакций, выполненные в виде фотоприемной матрицы возбуждаемой посредством перфокарты, основной осветитель и группу блоков сравнения, причем выход генератора импульсов соединен со входом первого кольцевого регистра сдвиха, введены первый, второй, третий, четвертый и пятый и шестой элементы ИЛИ, первый и второй блоки контроля кольцевого регистра сдвига, первый и второй триггеры, первый, второй и третий элементы И, переключатель режимов работы, первая, вторая, третья, четвертая и пятая группы элементов ;, первая, вторая и третья группа элементов ИЛИ, первый и второй блоки сравнения и вспомогательный осветитель, оричем выходы первого и второго кольцевых регистров сдвигов соецинены с соответствующими входами соответствующих блоков контроля кольцевого регистра сдвига, первый выход первого кольцевого регистра сдвига соединен с единичным входом первого триггера и первым входом первого элемента ИЛИ, второй выход первого кольцевого регистра сдвига соединен с первым входом второго элемента ИЛИ, третий выход первого кольцевого регистра сдвига соединен со вторым входами первого и второго элементоа ИЛИ,с нулевшли входами первого и, второго триггеров, единичные выходы которых соединены соответственно со вспомогательным и основным осветителем, четвертый выхо первого кольцевого регистра сдвига соединен со входом второго блока контроля кольцевого регистра сдвига и со входом второго кольцевого регис ра сдвига, выходы которого соединены с первыми входами соответствующих элементов И первой группы, пятый выход первого кольцевого регистра сдвига соединен с единичным входом второго триггера, со вторьв и входами всех элементов И первой группы, с управляющим входом первого блока сравнения, с первыми входами элементов И второй группы,с первыми входами элементов И третьей группы, с первыми входами элементов И четвертой и с управляющим входом второго блока сравнения, с первыми входами элементов И пятой группы, выходы элементов И первой группы соединены с первыми входами элементов ИЛИ первой группы, выходы элементов ИЛИ первой группы соединены с соответствующими управляющими входами регистра входных комбинаций тестовых сигналов и регистра ответных реакций, выходы регистра входных комбинаций тестовых сигналов и регистра ответных реакций соединены со входами первого элемента И и третьего элемента ИЛИ, выходы которых соединены соответственно с первым и вторым входами первого блока сравнения, выходы регистра входных комбинаций тестовых сигналов соединены со вторьми входам соответствующих элементов И второй группы, выходы которьйх соединены со входами контролируемого блока, выходы контролируемого блоха соединены со вторыми входами соответствующих элементов. И третьей группы, выходы регистра ответных реакций соединены со вторыми входами соответствующих элементов И четвертой группы, выходы элементов И третьей и четвертой группы соединены соответственно с первыми входами элементов ИЛИ второй и третьей групп, выходы первого элемента ИЛИ соединены со вторыми входами элементов ИЛИ третьей группы, выход второго элемента ИЛИ соединен со вторыми входами элементов ИЛИ пер вой и второй групп,выхода элементов

или второй и третьей групп попарно соединены со входами соответствующих блоков сравнения группы, выходы блока сравнения группы соединен с соответствующими входами второго элемента И и четвертого элемента ИЛИ выход которого соединен с первым входом второго блока сравнения, выход второго элемента-И соединен со вторь входом второго блока сравнения, выходы блоков сравнения группы соединены со вторыми входами элементов И пятой группы, выходы которых соединены со входами пятого элемента ИЛИ, четвертый выход второго кольцевого регистра сдвига соединен с первыми входс1ми третьего элемента И и шестого элемента ИЛИ, выход которого соединен с управляющим входом генератора импульсов, выходы первого и второго блоков сравнения, третьего элемента И „и элементов И пятой группы соединены со входами блока индикации, выход которого соединен с инверсным входом третьего элемента И, второй, третий, четвертый, пятый и шестой входы шестого элемента ИЛИ соединены соответственно с выходами первого блока контроля кольцевого сдвигового регистра, второго блока контроля кольцевого сдвигового регистра, первого блока сравнения, второго блока сравнения и через переключатель режимов с пятым элементом ИЛИ.

Блок контроля кольцевого регистра сдвига содержит элемент задержки, первый, второй и третий элементы ИЛИ первый .и второй триггеры, схему сравнения и элемент И, причем четные входы группы входов блока соединены со входами первого элемента ИЛИ, нечетные входы группы входов блокасоединены со BTOpbBvj элементом ИЛИ, выходы первого и второго элементов ИЛИ соедикены соответственно с единичным входом первого триггера и с первым входом элемента И, выход которого соединен с первьм входом третьего элемента ИЛИ, второй вход которог соединен с единичным выходом начального состояния контролируемогокольцевого регистра сдвига, и с /установочным входс 1 второго триггера, выход третьего элемента ИЛИ соединен с нулевым входом первого триггера, единичный выход которого соединен с первым входом схемы сравнения и со входом элемента И, управляющий вход блока соединен со входом элемента задержки, выход г с торого соединен со счетным входом второго триггера, выход которого соединен со вторым входом схемы.сравнения, выход которой является выходом блока.

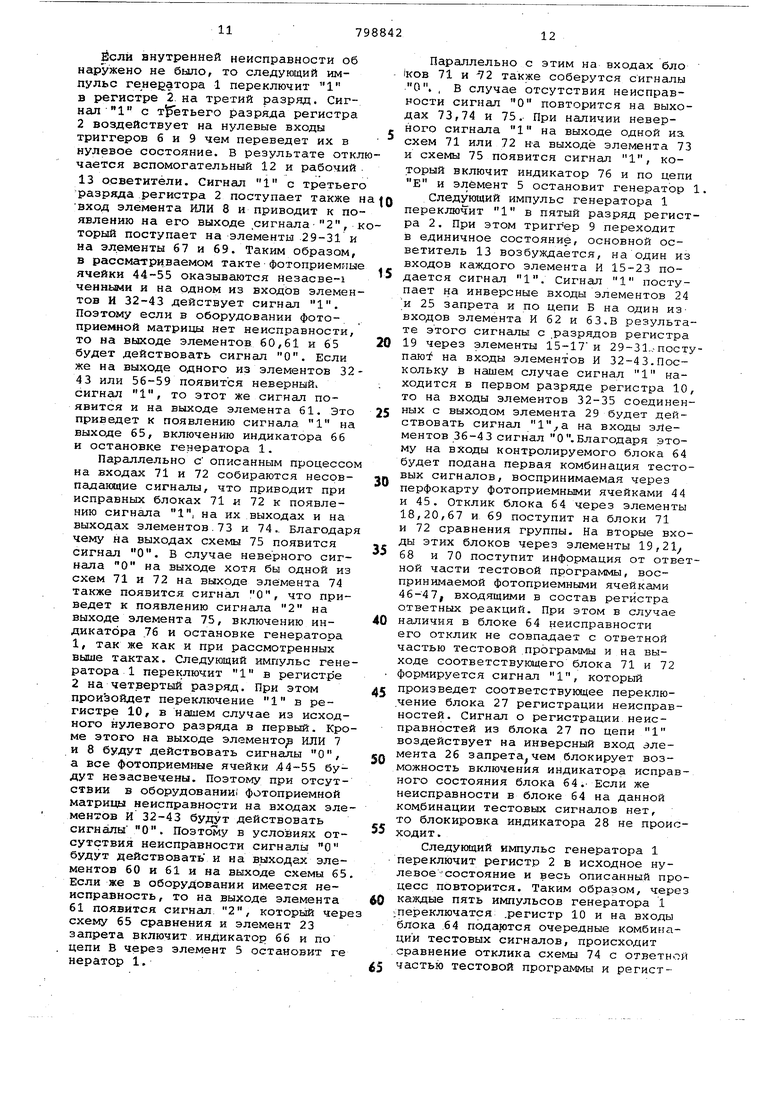

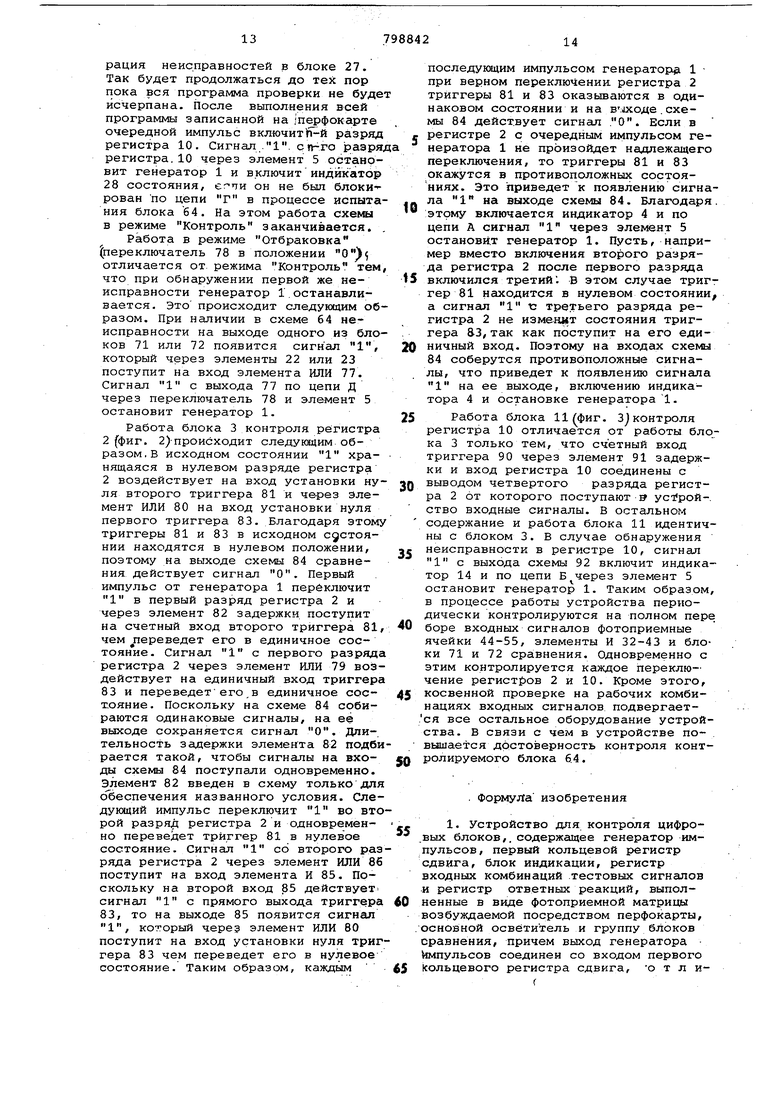

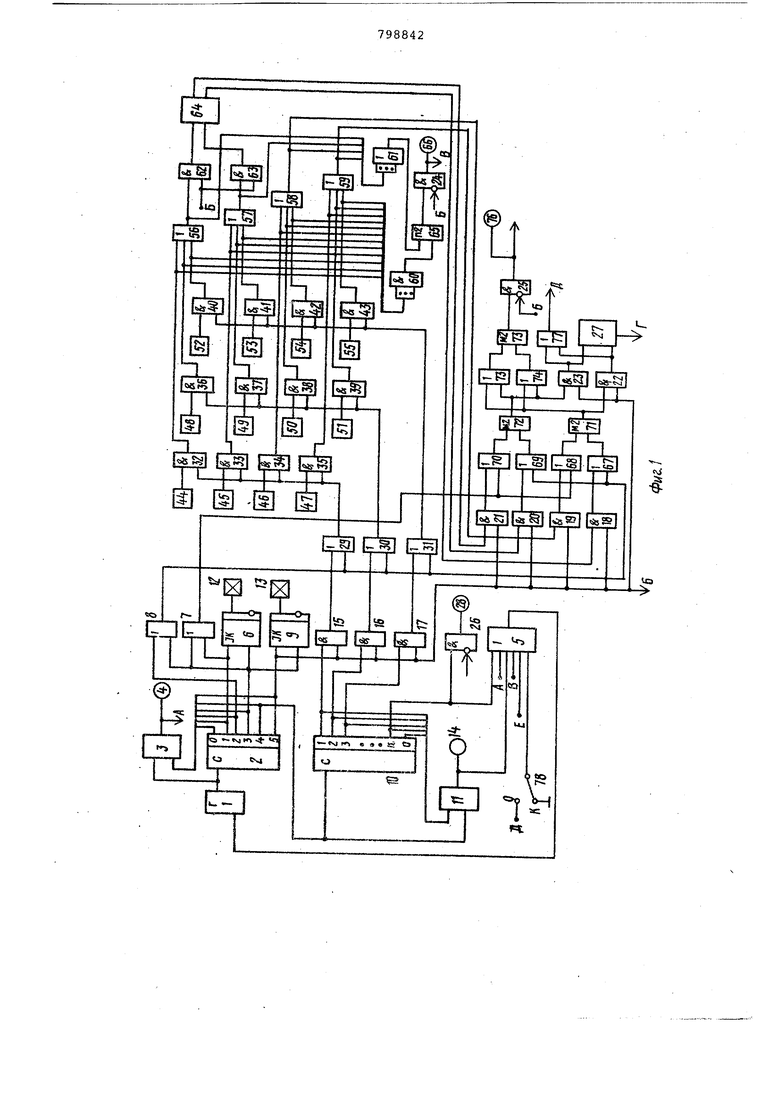

На фиг, 1 изображена принципиаль,ная схема предлагаемого устройства на фиг. 2 - схема включения блока контроля регистра; на фиг. 3 - схема включения второго блока регистра. Устройство со,аержит .генератор 1 импульсов, первый кольцевой регистр 2 сдвига, блока 3 контроля регистра индикатор 4 неисправности регистра, шестой элемент ИЛИ 5, первый триггер 6, первый и второй .элементы ИЛИ 7 и 8, второй триггер 9, второй кольцевой регистр/ 10 сдвига, блок 1 контроля регистра 10, вспомогательны осветитель 12, основной осветитель 13, индикатор 14 неисправности регистра 10, элементы И 15-23, элемен ты 24-26 запрета, блок 27 регистрации неисправностей, индикатор 28 ис правности контролируемого блока, пер вая группа элементов ИЛИ 29-31, эле менты И 32-43, фотоприемные ячейки 44-55, элементы ИЛИ 56-59, первый элемент И 60/третий элемент ИЛИ 61, вторая группа элементов И 62 и 63, контролируемый блок 64, схема 65 сравнения,индикатор 66 неисправности фотоприемной матрицы, элементы ИЛИ 67-70, блоки. 71 и 72 сравнения группы, четвертый элемент ИЛИ 73, второй элемент И 74, схема 75 сравнения, индикатор 76 неисправности блоков сравнения, пятый элемент ИЛИ 77 пере ключатель 78 режимов работы, второй и третий элементы ИЛИ 79 и 80, второй триггер 81 со счетным входом элемент 82 задержки, первый триггер 83, схема 84 сравнения, элемент И , первый элемент ИЛИ 86, элемент ИЛИ 87, триггер 88, .элемент ИЛИ 89, триггер 90 со счетным входом, элемент 91 задержки, схема 92 сравнения, элемент И 93, элемент ИЛИ 94. Элементы 15-17 образуют первую группу элементов И, элементы 18 и 20 - третью группу элементов И, элементы 19 и 21 - четвертую, группу элекГентов И, а элементы 22 и 23 пятую группу элементов И. Элементы 67 и 69 и 68 и 70 соответственно образуют вторую и третью группы элементов ИЛИ. Совокупность элементов 24 к 65 и 25 и 75 являются соответст венно первым и вторым блоками сравнения. Совокупность элементов 27,28, 66 и 76 составляет блок индикации. Совокупность элементов 32, 33,36,37, 40,41,44,45,48,49,52,53,56 и 57 составляет регистр входных комбинаций тестовых сигналов, а совокупность элементов-34,35,38,39,42,43,46,47, 50,51,54,55,58 и 59 - регистр ответных реакций. Генератор 1 импульсов соединен выходом со входом кольцевого регис ,ра 2 сдвига, содержащего шесть разрядов - пять рабочих и один вспомогательный (нулевой разряд). Выводы всех разрядов регистра 2 и вывод генератора 1 подведены к блоку 3 контроля регистра 2. Выход блока 3 подключен к индикатору 4 нeиcпpaвнoc ти регистра 2 и по цепи А ко входу элемента ИЛИ 5. Вывод первого разряда регистра 2 подведен к единичному входу первого триггера о, к его нулевому входу подведен вывод третьего разряда регистра 2. Выводы первого и третьего разрядов подведены также ко входам первого элемента ИЛИ 7. Вывод третьего разряда регистра 2 qpeдинен также со входом элемента ИЛИ 8 и с нулевым входом триггера 9. . Второй вход элемента ИЛИ 8 соединен со вторЕлм разрядом регистра 2. Четвертый разряд регистра 2 соединен со входом кольцевого регистра 10 сдвига с блоком 11 контроля регистра 10. Пятый разрядрегистра 2 соединен с единичным входом триггера 9. Прямые входы триггеров 6 и 9 соединены соответственно со схемами включения вспомогательного 12 и основного 13 осветителей. Выход блока 11 соединен с индикатором 14 неисправности регистра 10 и со входом шестого элемента ИЛИ 5. Вывод пятого разряда регистра 2 подведен ко входам эле- ментов И 15-23 и по цепи -Б к инверсным входам элементов запрета 24 и 25. Ко вторым входам первой группы элементов И 15-17 подведены соответственно выводы первого, второго и третьего разрядов регистра 10. На фиг. 1 показаны, соединения только первых трех разрядов регистра 10. Аналогично соединяются со входами элементов И, соединенных вторыми входами с пятым разрядом регистра 2, все последующие разряды регистра 10 вплоть до -1 разряда (-1 число адресных входов регистра тестов) -и разряд регистра 10 соединен с прямым входом элемента 26 запрета и со входом элемента ИЛИ 5. Инверсный вход элемента 26 по цепи Г соединен с блоком 27 регистрации неисправностей. Выход элемента 26 соединен , с индикатором 28 исправного состояния контролируемого блока, выходы элементов 15-17 соединены со входами элементов ИЛИ 29-31 соответственно. Вторые входы элементов 29-31 соединены с выходом элемента ИЛИ 8. Выход элемента 29 соединен со входом группы элементов И 32-35. Аналогично выход элемента 30 соединен со входами элементов И 36-39, а выходы элемента 31 - со входами элементов И 40-43. Вторые входы элементов 32-43 соединены соответственно с фотоприемными ячейками 44-45. Ячейки 44,45,48, 49, S3 и 55 входят в состав фотоприемной матрицы регистра входных комбинаций тестовых сигналов, а ячейки 46,47,50,51,54,55 входят в состав фотоприемной матрицы регистра ответных реакций. На фиг. 1 изображено оборудование составляющее первые .две строки первых трех столбцов помянутых фотоприемной матрицы. Выход элементов И 32-43 построчно объединены элементами ИЛИ 56-59, т.е выходы элементов 32,36 и 40 соединены со входами элемента ИЛИ 56, элементы 33,37 и 41 - с элементом 57, элементы 34,38 и 42 - с элементом 58 и элементы 35,39 и 43 - с элементом 59. Кроме этого, выходы всех элементов И 32-43 подведены ко входам элемента И 60. Выходыэлементов ИЛИ 5659 подведены ко входам элемента ИЛИ 61. Выходы элементов ИЛИ 56 и 57 под ведены соответственно ко входам элементов И 62 и 63, вторые входы которых. по цепи Б соединены с выводом пятого разряда регистра 2. Выходы элементов 62 и 63 подведены ко входам контролируемого блока 64. Выходы элементов 60 и 61 подведены ко входам схемы 65 сравнения, выход которо соединен с прямым входом элемента 24 запрета, йлход элемента 24 соединен с индикато)ром 66 неисправности фотоприемной матрицы и по цепи В со входом элемента ИЛИ 5. Выход элементов ИЛИ 58 и 59 подведены соответственно ко входам элементов И 19 и 21. Выходы контролируемого блока 64 подведены ко входам элементов И. 18 и 20, Вы ходы элементов 18-21 соединены соответственно со входс1ми элементов ИЛИ 67-70. Вторые входы элементов 67 и 69 соединены с выходом элемента ИЛИ 8, а вторые входы элементов 68 и 70 соединены с выходом элемента ИЛИ 7. Выходы элементов 67 и 68 подведены ко входам блока. 71 сравнения группы а выходы элементов 68 и 70 - ко входам блока 72 сравнения группы. Выход блоков 71 и 72 соединены со входами элементов И 22 и 23 и со входами элемента ИЛИ 73 и элемента И 74. Выходы элементов 73 и 74 соединены со входами схемы 75 сравнения. Выходы схелш 75 соединены с прямым входом элемента 25 запрета. Выход элемента 26 соединён с .индикатором 76 неисправности блока сравнения и по цепи Е - со входом элемента ИЛИ 5. Выходы элементов И 22 и 23 соединены с блоком 27 регистрации неисправностей и со входами ИЛИ 77.Выход элемента 77 по цепи Д соеди нен с переключателем 78 режимов рабо ты, соед5иненном в свою очередь со вх дом элемента ИЛИ 5. Блок 3 контроля регистра 2 (фиг.2) содержит элемент ИЛИ 79, соединенный входами с выводами нечетных разрядов регистра 2. Вспо1УЮгаГельный - нулевой разряд регистра 2 соединен со входом элемента ИЛИ 80 и со входом установки нуля триггера 81 со счетным входом. С выходом генератора 1 через элемент 82 задержки соединен счетный вход триггера 81. Выход элемента 79 соединен с единичным вхо {ДОМ триггера 83, а выход элемента 1,80 соединен с нулевым входрм тригге а 83. Прямые выходы триггеров 81 83 соединены со входами схемы 84 равнения, выход которой по цепи А оединен со входом элемента ИЛИ 5 и индикатором 4, Прямой выход триггеа 83 соединен также со. входом элеента И 85. Второй вход элемента 85 соединен с выходом элемента ИЛИ 86, входы которого соединены с выводами етных разрядов регистра 2. Выход элемента 85 соединен со входом элемента 80. Блок 11(фиг. З)контроля регистра 10 аналогичен по содержанию с блоком 3 и содержит элемент ИЛИ 87входами соединенный с выводами нечетных разрядов регистра 10. Выход элемента 87 соединен с единичным входом триггера -88. Нулевой вход триггера 88 соединен с выходом элемента ИЛИ 89. Один из входов элемента 89 соединен с выводом вспомогательного нулевого разряда регистра 10. Вывод вспомогательного разряда регистра 10 соединен также со входом установки нуля триггера 90 со счетным входом. Счетный вход триггера 90 соединен через элемент 9.1 задержки с выходом четвертого разряда регистра 2. Прямые выходы триггеров 88 и 90 соединены со входами схемы 92 сравнения, выход которой по цепи Б соединен со входом элемента 5 и с индикатором 14. Прямой выход триггера 88 соединен также со входом элемента И 93,второй вход которого соединен с выходом элемента ИЛИ 94.Выходы элемента 94 соединены с выводами .четных разрядов регистра 10. Фотоприемная матрица регистра входных комбинаций тестовых сигналов и регистра ответных реакций возбуждается, с помощью просветной перфокарты вспомогательным 12 и основным 13 осветителями. Перфокарта выполняется из прозрачного материала и покрывается люминесцентным красителем, свечение которого возбуждается светом в.спомогательного осветителя 12, спектральный состав которого согласован с областью возбуждения люминесцентного красителя. Работа устройства происходит в двух режимах - Контроль и Отбраковка, осуществляемых переводом переключателя 78 соответственно в положения К и О J В режиме Контроль работа устройства происходит следующим образом. В исходном состоянии регистры 2 и 10 хранят 1 в нулевых разрядах, триггер 9 хранит 1 на прямом выходе, а триггер 6 на прямом выходе хранит сигнал Первый импульс генератора 1 переключит 1 в регистре 2 из нулевого разряда в первый. Сигнал 1 с первого разряда регистра 2 переключит триггер 6 в состояние характеризующееся наличием 1 на прямом выходе - единичное достояние. Благодаря этому произойдет включение вспомога тельного осветителя 12, Свет освети теля 12 возбудит люминесцентное све чение перфокарты. Поскольку при это основной осветитель 13 также возбуж исходное состояние триггера 9 - еди ничное)то все фотоприемные ячейки, фотоприемной матрицы регистров вход ных комбинаций тестовых сигналов и регистра ответных реакций окажутся засвеченными возбуждающим их светом Если фотоприемная ячейка исправна, при засветке.на ее выходе должен появиться сигнал 1, Сигнал 1 С фотоприемных ячеек 44-55 (фиг. ) поступит на входы соответствукхцих элементов И 32-43. Поскольку в рассматриваемый такт сигнал на выходе элемента ИЛИ 8 - О, а элементы И 15-17 заперты сигналом О с пятого разряда регистра 2, то при верной работе фо.топриемной матрицы на выхо элементов 32-43 должны наблюдаться сигналы О. По этой причине на выходе элементов ИЛИ 56-59,61 и элемента И 60 также должны наблюдаться сигналы О. Поэтому на выходе схем 65 сравнения будет действовать сигнал О и включение индикатора 66 не произойдет. Если же на выходе хотя бы одного из элементов И 32-43 появится неверный сигнал 1, то появится и на выходе эле сигнал мента 61. На выходе же элемента И 60 будет сигнал О. Поэтому на выходе схемы 65 тоже появится сигнал 1, который включит индикатор 66, что сигнализирует о неисправности оборудования фотоприемной матрицы; При этом по цепи В на вход элемента ИЛИ 5 поступят сигналы 1.Появившийся в результате этого сигнал 1 на выходе элемента 5 остановит гене ратор 1. Параллельно с описанным процессом контроля фотоприемной матрицы при включении первого разряда регистра сигнал 1 появится и на выходе элемента ИЛИ 7, соединенного одним из входов с выводом от первого -разряда регистра 2. Сигнал 1 с выход элемента 7 поступит на входы элемен тов ИЛИ 68 и 70, на вторые входы которых действует сигнал О с выхо дов элементов И-19 и 21 в рассматриваемом такте запертых сигналом О с пятого разряда регистра 2. При это на выходе элементов 67 и 69 будут действовать сигналы О. Поэтому-на выходе блоков 71 и 72 сравнения при их верной работе должны появитьбя сигналы 1. Благодаря этому на выходе элемента И 74 и элемента ИЛИ 73 также появится сигнал 1, поэтому на выходе схемы сравнения 75 будет действовать сигнал О. Если же один из блоков сравнения(71 или 72)сработает неверно, то на выходе элемента И 74 будет сигнал О и на выходе элемента ИЛИ 73 - сигнал 1 Благодаря этому на выходе схемы сравнения 75 появится скгнал .1, который пройдет элемент запрета 25, так как на его инверсный вход действует сигнал О и включит индикатор 76, и далее по цепи Е через элемент ИЛИ 5 остановит генератор 1. Одновременно с описанным процессом происходит и переключение блока 3, о работе которого сказано ниже. Если в результате описанных процессов неисправности Обнаружено не было, то .следующий импульс генератора 1 переключит 1 во второй разряд регистра 2. При этом сигнал 1 с вывода второго разряда через элемент ИЛИ 8 поступит на входы элементов ИЛИ 2931 и на входы элементов ИЛИ 67 и 69. Поскольку источники 12 и 14 находятся в возбужденном состоянии, то на оба входа элементов И 32-43 при исправных фотоприемных ячейках 44-55 действует сигнал 1. Это приводит при исправной фотоприемной матрице к появлению сигналов на выходе элементов 60 и 61 и следовательно к появлению сигналов О на выходе схемы сравнения 65. В случае если на выходе какого-либо из элементов И 32-43 отсутствует сигнал 2, то на выходе элемента И 60 появится сигнал О, а на выходе элемента 61 сигнал 1. В результате несовпадения этих сигналов на выходе схемы 65 появится сигнал 1, который пройдет элемент 24 запрета, так как на его инверсный вход действует сигнал О с вывода пятого разряда регистра 2. Сигнал 1 с выхода 24 включит индикатор 66 и по цепи В через элемент ИЛИ 5 остановит генератор 1. Параллельно с описанным процессом при включении 1 на втором разряде регистра 2 сигнал 1 появится на выходах элементов ИЛИ 67и 69, на выходах же элементов ИЛИ 68и 70, будет сигнал О, так как в рассматриваемый такт на выходе элемента ИЛИ 7 действует сигнал О. Таким образом,на выходе схем сравнения 71 и 72 в случае их исправности появится сигнал 2. В результате на выходе элементов 73 и 74 также появится сигнал 1, а на .выходе схемы 75 появится сигнал О. В случае если же на выходе хотя бы одной из схем 71 или 72 будет неверный сигнал О, то на выходе элемента 74 тоже появится сигнал О, Это приведет к появлению на выходе схемы 75 сигнала 1 который пройдет элемент запрета 25, так как на его инверсный вход действует сигнал О с пятого разряда регистра 2. Сигнал 1 с выхода 25 включит индикатор 76 и по цепи Е через элемент 5 остановит генератор 1. Вели внутренней неисправности об наружено не бьоло, то следующий импульс re,HegaTOpa 1 переключит 1 в регистре 2. на третий разряд. Сигнал 1 с третьего разряда регистра 2 воздействует на нулевые входы триггеров 6 и 9 чем переведет их в нулевое состояние, в результате откл чается вспомогательный 12 и рабочий 13 осветители. Сигнал 1 с третьег разряда регистра 2 поступает также вход элемента ИЛИ 8 и приводит к по явлению на его выходе сигнала торый поступает на элементы 29-31 и на элементы 67 и 69. Таким образом, в рассматриваемом такте фотоприемпы ячейки 44-55 оказываются незасве-i ченнъФАи и на одном из входов элемен тов И 32-43 действует сигнал 1. Поэтому если в оборудовании фотоприемной матрицы нет неисправности, то на выходе элементов 60,61 и 65 будет действовать сигнал О. Если же на выходе одного из элементов 32 43 или 56-59 появится неверннЙ1 сигнал 1, то этот же сигнал появится и на вьлходе элемента 61. Это приведет к появлению сигнала 1 на выходе 65, включению индикатора 66 и остановке генератора 1. Параллельно с описанным процессо на входах 71 и 72 собираются несовпадающие сигналы, что приводит при исправных блоках 71 и 72 к появлению сигнала 1, на их выходах и на выходах элементов. 73 и 74.. Благодар чему на выходах схемы 75 появится сигнал О. В случае неверного сигнала О на выходе хотя бы одной из схем 71 и 72 на выходе элемента 74 также появится сигнал О, что приведет к появлению сигнала 2 на выходе элемента 75, включению индикатора 76 и остановке генератора 1, так же как и при рассмотренных выше тактах. Следующий импульс гене ратора 1 переключит 1 в регистре 2 на четвертый разряд. При этом произойдет переключение 1 в регистре 10, в нашем случае из исходного нулевого разряда в первый. Кро ме этого на выходе элементо ИЛИ 7 и 8 будут действовать сигналы О, а все фотоприемные ячейки 44-55 будут незасвечены. Поэтому при отсутствии в оборудовании фотоприемной матрицы неисправности на входах эле ментов И 32-43 будут действовать сигналы О. Поэтбму в условиях отсутствия неисправности сигналы О будут действовать и на выходах элементов 60 н 61. и на выходе схемы 65 Если же в оборудовании имеется неисправность , то на выходе элемента 61 появится сигнал 2, которьй чер схему 65 сравнения и элемент 23 запрета включит индикатор 66 и по цепи В через элемент 5 остановит ге нератор 1. Параллельно с этим на входах бло KOB 71 и 72 также соберутся сигналы О. , В случае отсутствия неисправности сигнал О повторится на выходах 73,74 и 75. При наличии неверного сигнала 1 на выходе одной иа схем 71 или 72 н-а выходе элемента 73 и схемы 75 появится сигнал 1, который включит индикатор 76 и по цепи Е и элемент 5 остановит генератор 1. Следующий импульс генератора 1 переключит 1 в пятый разряд регистра 2. При этом триггер 9 переходит в единичное состояние, основной осветитель 13 возбуждается, на один из входов каждого элемента И 15-23 подается сигнал 1. Сигнал 1 поступает на инверсные входы элементов 24 и 25 запрета и по цепи Б на один извходов элемента И 62 и 63.В результате этого сигналы с разрядов регистра 19 через элементы 15-17 и 29-31...-поступают на входы элементов И 32-43.Поскольку в нашем случае сигнал 1 находится в первом разряде регистра 10, то на входы элементов 32-35 соединенных с выходом элемента 29 будет действовать сигнал на входы элементов 36-43 сигнал 0.Благодаря этому на входы контролируемого блока 64 будет подана первая комбинация тестовых сигналов, воспринимаемая через перфокарту фотоприемными ячейками 44 и 45. Отклик блока 64 через элементы 18,20,67 и 69 поступит на блоки 71 и 72 сравнения группы. На вторые входы этих блоков через элементы 19,21 68 и 70 поступит информация от ответной части тестовой программы, воспринимаемой фотоприемными ячейками 46-47, входящими в состав регистра ответных реакций. При этом в случае наличия в блоке 64 неисправности его отклик не совпадает с ответной частью тестовой программы и на выходе соответствующего блока 71 и 72 формируется сигнал 1, которьй произведет соответствующее переклю.чение блока 27 регистрации неисправностей. Сигнал о регистрации неисправностей из блока 27 по цепи 1 воздействует на инверсный вход элемента 26 запрета чем блокирует возможность включения индикатора исправного состояния блока 64.- Если же неисправности в блоке 64 на данной комбинации тестовых сигналов нет, то блокировка индикатора 28 не происходит . Следующий импульс генератора 1 переключит регистр 2 в исходное нулевое : состояние и весь описанный процесс повторится. Таким образом, через каждые пять импульсов генератора 1 переключатся .регистр 10 и на входы блока .64 подаются очередные комбинации тестовых сигналов, происходит сравнение отклика схемы 74 с ответной частью тестовой программы и регистрация неисправностей в блоке 27. Так будет продолжаться до тех пор пока вся программа проверки не буде исчерпана. После выполнения всей программы записанной на перфокарте очередной импульс включит -й разряд регистра 10. Сигнал,., сп-го разря регистра.10 через элемент 5 обтановит генератор 1 и включит индикатор 28 состояния, егтти он не был блокирозан по цепи Г в процессе испыта ния блока 64. На этом работа cxeNOi в режиме Контроль заканчивается. Работа в режиме Отбраковка {переключатель 78 в положении 0) отличается от режима Контроль тем что при обнаружении первой же неисправности генератор 1.останавливается. Это происходит следующим об разом. При наличии в схеме 64 неисправности на выходе одного из бло ков 71 или 72 появится сигнал 1, который через элементы 22 или 23 поступит на вход элемента ИЛИ 77. Сигнал 1 с выхода 77 по цепи Д через переключатель 78 и элемент 5 остановит генератор 1. Работа блока 3 контроля регистра 2 (фиг. 2)-происходит следукнцим образом, В исходном состоянии 1 хранящаяся в нулевом разряде регистра 2 воздействует на вход установки ну ля второго триггера 81 и через элемент ИЛИ 80 на вход установки нуля первого триггера 83. Благодаря этом триггеры 81 и 83 в исходном сдстоянии находятся в нулевом положении. поэтому на выходе схемы 84 сравнения действует сигнал О. Первый импульс от генератора 1 переключит 1 в первый разряд регистра 2 и через элемент 82 задержки поступит на счетный вход второго триггера 81 чем 1ереведет его в единичное состояние. Сигнал 1 с первого разряд регистра 2 через элемент ИЛИ 79 воздействует на единичный вход триггера 83 и переведетего,в единичное соетояние. Поскольку на схеме 84 собираются одинаковые сигналы, на ее выходе сохраняется сигнал О. Длительность задержки элемента 82 подби рается такой, чтобы сигналы на входы схемы 84 поступали одновременно. Элемент 82 введен в схему только для обеспечения названного условия. Следующий импульс переключит 1 во вто рой разряд регистра 2 и одновременно переведет триггер 81 в нулевое состояние. Сигнал 1 со второго раз ряда регистра 2 через элемент ИЛИ 86 поступит на вход элемента И 85. Поскольку на второй вход 85 действует сигнал 1 с прямого выхода триггера 83, то на выходе 85 появится сигнал 1, который через элемент ИЛИ 80 поступит на вход установки нуля триг гера 83 чем переведет его в нулевое состояние. Таким образом, каждым последукнцим импульсом генератору 1 при верном переключаем и и. регистра 2 триггеры 81 и 83 оказываются в одинаковом состоянии и на . схемы 84 действует сигнал .О. Если в регистре 2 с очередным импульсом генератора 1 не произойдет надлежащего переключения, то триггеры 81 и 83 окажутся в противоположных состояниях. Это приведет к появлению сигнала 1 на выходе схемы 84. Благодаря, этому включается индикатор 4 и по цепи А сигнал 1 через элемент 5 остановй.т генератор 1. Пусть, например вместо включения второго разряда регистра 2 после первого разряда включился третий , в этом случае триггер 81 находится в нулевом состоянии, а сигнал 1 гз третьего разряда регистра 2 не изменит состояния триггера аз, так как поступит на его единичный вход. Поэтому на входах схемы 84 соберутся противоположные сигналы, что приведет к появлению сигнала 1 на ее выходе, включению индикатора 4 и остановке генератора1. Работа блока И(фиг. 3J контроля регистра 10 отличается от работы блока 3 только тем, что счетный вход триггера 90 через элемент 91 задержки и вход регистра 10 соединены с выводом четвертого разряда регистра 2 от которого поступают э устрой-, ство входные сигналы. В остальном содержание и работа блока 11 идентичны с блоком 3. В случае обнаружения неисправности в регистре 10, сигнал 1 с выхода схемы 92 включит индикатор 14 и по цепи Б через элемент 5 остановит генератор 1. Таким образом, в процессе работы устройства периодически контролируются на полном пере боре входных сигналов фотоприемные ячейки 44-55, элементы И 32-43 и блоки 71 и 72 сравнения. Одновременно с этим контролируется каждое переключение регист)ов 2 и 10. Кроме этого, косвенной проверке на рабочих комбинациях входных сигналов подвергается все остальное оборудование устройства. В связи с чем в устройстве Повышается достоверность контроля контролируемого блока 6.4. . Формула изобретения 1. Устройство для контроля цифровых блоков,, содержащее генератор импульсов, первый кольцевой регистр сдвига, блок индикации, регистр входных комбинаций .тестовых сигналов и регистр ответных реакций, выполненные в виде фотоприемной матрицы возбуждаемой посредством перфокарты, сновной освётитель и группу блоков сравнения, причем выход генератора Импульсов соединен со входом первого koльцeвoгo регистра сдвига, о т л и( чающееся тем, что, с целью повьдиения достоверности контроля, в устройств.о введены первый, второй, третий, четвертый, пятый и шестой элементы ИЛИ, первый и второй блоки контроля кольцевого регистра сдвига, первый и второй триггеры, первый, второй и третий элементы И, переклюjчaтeль режимов работы, первая, вторая, третья четвертая и пятая группа элементов Иг первая, вторая и третья группа элементов ИЛИ, первый и второй блоки сравнения и вспомогательный осветитель, причем выходы первого и .второго кольцевых регистров сдвигов соединены с соответствующими входами соответствующих блоков контроля кольцевого регистра сдвига, пер вый выход первого кольцевого регистра сдвига соединен с единичным входо первого триггера и первым входрм первого элемента ИЛИ, второй выход перБсгс кольцевого регистра сдвига соединен с первым входом второго эле мента ИЛИ, третий выход первого кольцевого регистра сдвига соединен со вторыми входами первого и второго элементов ИЛИ, с нулевыми входами первого и второго триггеров, единичные выходы которых соединены соответ ственно со вспомогательным и основным осветителем, четвертый выход первого кольцевого регистра сдвига соединен со входом второго блока контроля кольцевого регистра сдвига и со входом второго кольцевого регистра сдвига, выходы которого соединены с первыми входами соответстг вующих элементов И первой группы, пя тый выход первого кольцевого регист ра сдвига соединен с единичным входом второго триггера, со вторыми входами всех элементов И первой груп пы, с управляющим входом первого бло ка сравнения, с первыми входами эле ментов И второй группы, с первыми входами элементов И третьей группы, с первыми входами элементами И четвертой и с управляющим входом второ го блока сравнения, с первыми входа ми элементов И пятой группы выходы элементов И первой группы соединены с первыми входами элементов ИЛИ пер вой группы, выходы элементов ИЛИ пе вой группы соединены с соответствую щими управляющими входами регистра входных комбинаций тестовых сигнало и регистра ответных реакций, выхо.ссы регистра входных комбинаций тестовых сигналов и регистра ответных реакций соединены со входами первог элемента И и третьего элемента ИЛИ, выходы которых соединены соответственно с первым и вторым входами пер вого блока сравнения, выходы регист ра входных комбинаций тестовых сигналов соединены со вторыми входами соответствующих элементов И второй группы, выходы которых соединены со входами контролируемого блока, выходы контролируемого блока соединены со вторыми входами соответствующих элементов И третьей группы, выходы регистра ответных реакций соединены со вторыми входами соответствующих элементов И четвертой группы, выходы элементов И третьей и четвертой группы соединены соответственно с первыми входами элементов ИЛИ второй и третьей групп, выходы первого элемента ИЛИ соединены со вторыми входами элементов ИЛИ третьей группы, выход второго элемента ИЛИ соединен со вторыми входами элементов ИЛИ первой и второй групп, выходы элементов ИЛИ второй и третьей групп попарно соединены со входами соответствующих блоков сравнения группы, выходы каждого блока сравнения группы соединены с соответствующими входами второго элемента И и четвертого элемента ИЛИ, выход которого соединен с первым входом второго блока сравнения, выход второго элемента И соединен со вторым входом второго блока сравнения, .выходы блоков сравнения группы соединены со вторыми входами элементов И пятой группы, выходы которых соединены со входами пятого элемента ИЛИ, четвертый выход второго кольцевого регистра сдвига соединен с первыми входами третьего элемента И и шестого элемента ИЛИ, выход которого соединен с управляющим входом генератора импульсов, выходы первого и второго блоков сравнения, третьего элемента И и элементов И пятой группы соединены со входами блока индикации, выход которого соединен с инверсным входом третьего элемента И, второй, третий, четвертый, пятый и шестой входы шестого элемента ИЛИ соединены соответственно с выходами первого блока контроля кольцевого сдвигового регистра, второго блока контроля кольцевого сдвигового регистра, первого блока сравнения, второго блока сравнения и через переключатель режимов с пятым элементом ИЛИ. 2. Устройство по п. 1, отличающееся тем, что блок контроля кольцевого регистра сдвига содержит элемент задержки, первый, второй и третий элементы ИЛИ, первый и второй триггеры, схему сравнения и элемент И, причем четные входы группы входов блока соединены со входами первого элемента ИЛИ, нечетные входы группы входов блока соединены со вторым элементом ИЛИ, выходы первого и второго элементов ИЛИ соединены соотв.етственно с единичным входом первого триггера и с первым входом элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого CORдинен с единичным выходом iia ajrbnoio

состояния контролируемого кольцевого регистра сдвига, и с установочным входом второго тpиггepa выход третьего элемента ИЛИ соединен с нулевым входом первого триггера, единичный выход которого соединен с первым входом схемы сравнения- и со входом элемента-И, управляющийвход блока соединен со входом элемента задержки, выход которого соединен со счетным входом BTOpoio триггера, выход которого соединен со вторым входом

схемы сравнения, выход которого является выходом блока.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 525900, кл. Q06 Р 11/00, 1976,

.3. Авторское свидетельство СССР по заявке 2458199/24,, кл. Q 06 Р 11/00, 1977(прототип).

Авторы

Даты

1981-01-23—Публикация

1978-05-12—Подача