Изобретение относится к цифровой вычислительной технике и может быть использовано для поиска неисправностей в сложных цифровых схемах.

Целью изобретения является расши- рение функциональных возможностей устройства, за счет обеспечения контроля момента появления выходных сигналов контролируемого узла.

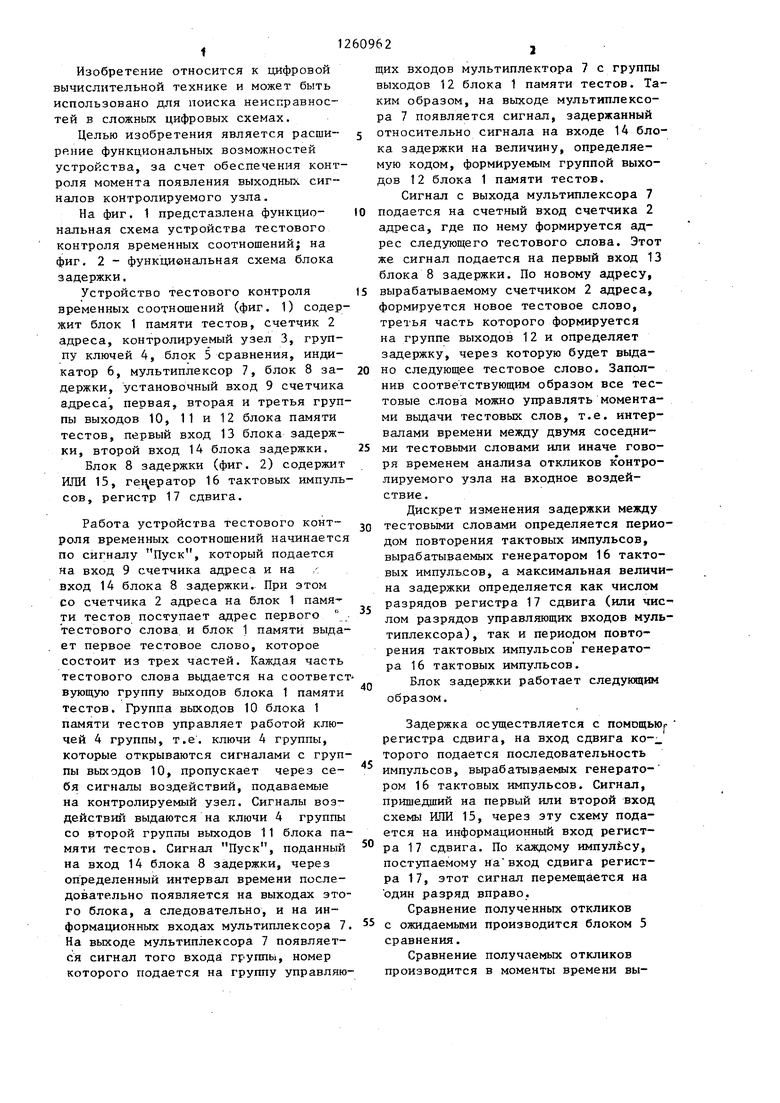

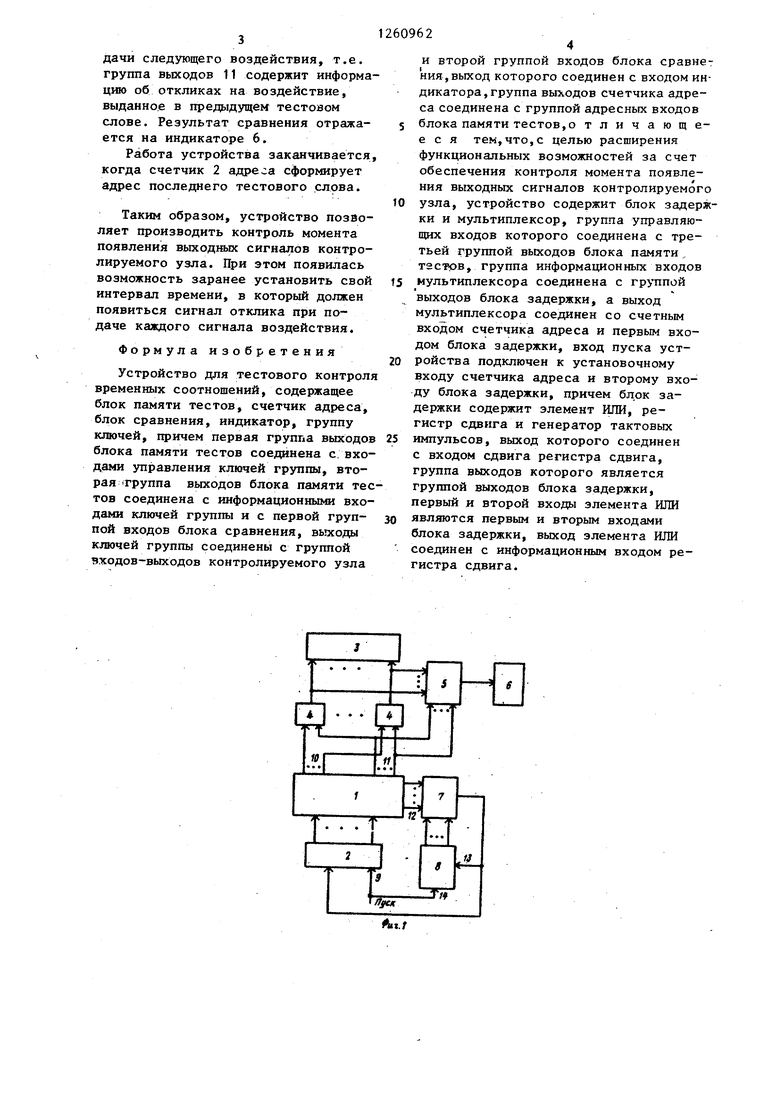

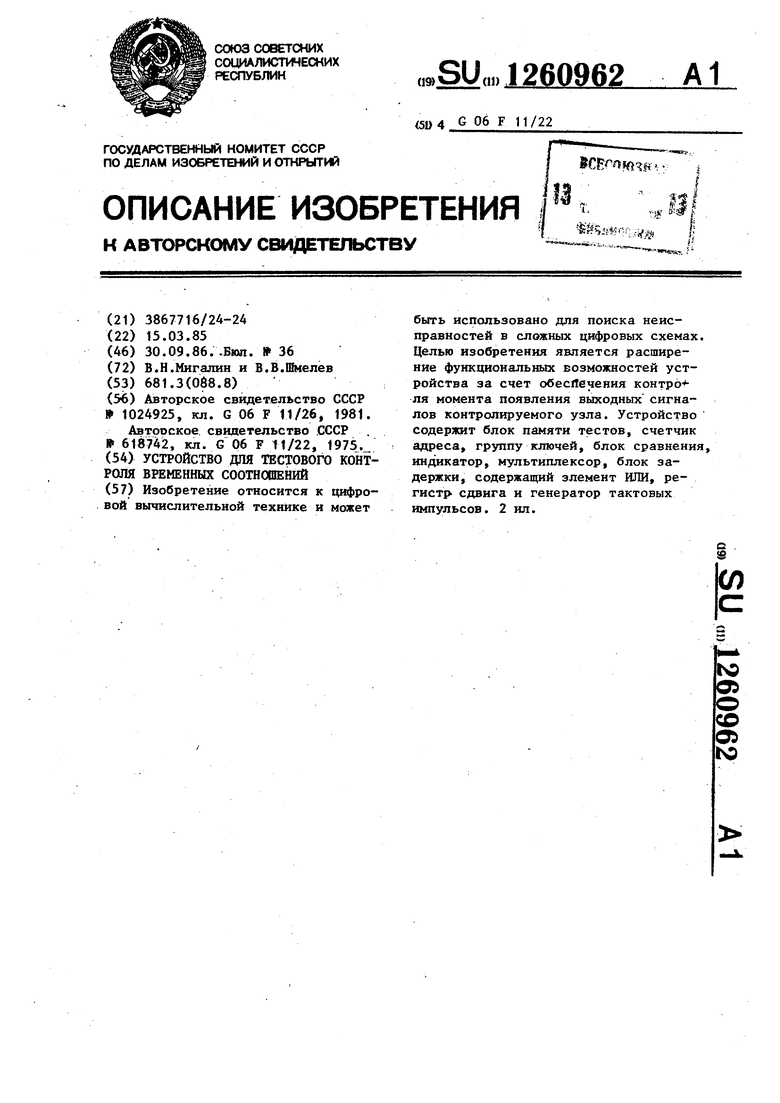

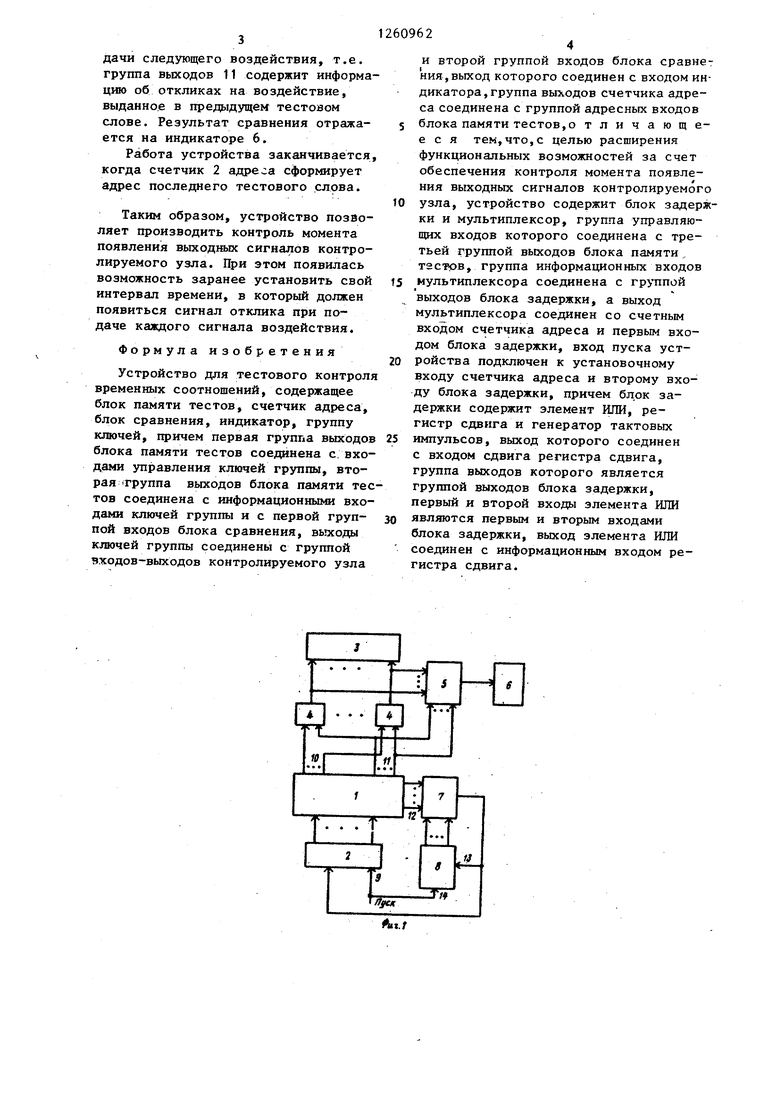

На фиг. 1 представлена функцио- нальная схема устройства тестового контроля временных соотношений; на фиг, 2 - функциональная схема блока задержки.

Устройство тестового контроля временных соотношений (фиг. 1) содержит блок 1 памяти тестов, счетчик 2 адреса, контролируемый узел 3, группу ключей 4, блок 5 сравнения, индикатор 6, мультиплексор 7, блок 8 за- держки, установочный вход 9 счетчика адреса, первая, вторая и третья группы выходов 10, 11 и 12 блока памяти тестов, первый вход 13 блока задержки, второй вход 14 блока задержки,

Блок 8 задержки (фиг, 2) содержит HJIli 15, геь ератор 16 тактовых импульсов, регистр 17 сдвига.

Работа устройства тестового контроля временных соотношений начинается по сигналу Пуск, который подается на вход 9 счетчика адреса и на ,-: Вход 14 блока 8 задержки. При этом со счетчика 2 адреса на блок 1 памя ти тестов поступает адрес первого тестового слова и блок 1 памяти выдает первое тестовое слово, которое состоит из трех частей. Каждая часть тестового слова вьодается на соответст вующую группу выходов блока 1 памяти тестов. Группа выходов 10 блока 1 памяти тестов управляет работой ключей 4 группы, т.е, ключи 4 группы, которые открываются сигналами с группы выходов 10, пропускает через себя сигналы воздействий, подаваемые на контролируемый узел. Сигналы воздействий выдаются на ключи 4 группы со второй группы выходов 11 блока памяти тестов. Сигнал Пуск, поданный на вход 14 блока 8 задержки, через определенный интервал времени последовательно появляется на выходах этого блока, а следовательно, и на информационных входах мультиплексора 7 На выходе мультиплексора 7 появляется сигнал того входа группы, номер которого подается на группу управляю

щих входов мультиплектора 7 с группы выходов 12 блока 1 памяти тестов. Таким образом, на выходе мультиплексора 7 появляется сигнал, задержанный относительно сигнала на входе 14 блока задержки на величину, определяемую кодом, формируемым группой выходов 12 блока 1 памяти тестов.

Сигнал с выхода мультиплексора 7 подается на счетный вход счетчика 2 адреса, где по нему формируется адрес следующего тестового слова. Этот же сигнал подается на первый вход 13 блока 8 задержки. По новому адресу, вырабатываемому счетчиком 2 адреса, формируется новое тестовое слово, тре1 ья часть которого формируется на группе выходов 12 и определяет задержку, через которую будет вьща- но следующее тестовое слово. Заполнив соответствующим образом все тестовые слова можно управлять моментами вьщачи тестовых слов, т.е, интервалами времени между двумя соседними тестовыми словами или иначе говоря временем анализа откликов контролируемого узла на входное воздействие.

Дискрет изменения задержки между тестовьми словами определяется периодом повторения тактовых импульсов, вырабатываемых генератором 16 тактовых импульсов, а максимальная величина задержки определяется как числом разрядов регистра 17 сдвига (или числом разрядов управляющих входов мультиплексора) , так и периодом повторения тактовых импульсов генератора 16 тактовых импульсов.

Блок задержки работает следующим образом.

Задержка осуществляется с помощьюг регистра сдвига, на вход сдвига ко- торого подается последовательность импульсов, вырабатываемых генерато- ром 16 тактовых импульсов. Сигнал, пришедший на первый или второй вход схемы РШИ 15, через эту схему подается на информационный вход регистра 17 сдвига. По каждому импульсу, поступаемому на вход сдвига регистра 17, этот сигнал перемещается на один разряд вправо.

Сравнение полученных откликов с ожидаемыми производится блоком 5 сравнения,

Сравнение получаемых откликов производится в моменты времени выдачи следующего воздействия, т.е. группа выходов 11 содержит информацию об откликах на воздействие, выданное в предыдущем тестовом слове. Результат сравнения отражается на индикаторе 6.

Работа устройства заканчивается, когда счетчик 2 адреса сформирует адрес последнего тестового слова.

Таким образом, устройство позволяет производить контроль момента появления выходных сигналов контролируемого узла. При этом появилась возможность заранее установить свой интервал времени, в который должен появиться сигнал отклика при подаче каждого сигнала воздействия.

Формула изобретения

Устройство для тестового контроля временных соотношений, содержащее блок памяти тестов, счетчик адреса, блок сравнения, индикатор, группу ключей, причем первая группа выходов блока памяти тестов соединена с. входами управления ключей группы, вторая труппа выходов блока памяти тестов соединена с информационными входами ключей гр5шпы и с первой группой входов блока сравнения, выходы ключей группы соединены с группой входов-выходов контролируемого узла

и второй группой входов блока сравнения, выход которого соединен с входом индикатора, группа выходов счетчика адреса соединена с группой адресных входов блока памяти тестов, о тличающе- е с я тем,что,с целью расширения функциональных возможностей за счет обеспечения контроля момента появления выходных сигналов контролируемого

узла, устройство содержит блок задержки и мультиплексор, группа управляющих входов которого соединена с третьей группой выходов блока памяти Т2СТОВ, группа информационных входов

мультиплексора соединена с группой

Iч

выходов блока задержки, а выход мультиплексора соединен со счетным входом счетчика адреса и первым входом блока задержки, вход пуска устройства подключен к установочному входу счетчика адреса и второму входу блока задержки, причем блок задержки содержит элемент ИЛИ, регистр сдвига и генератор тактовых

импульсов, выход которого соединен с входом сдвига регистра сдвига, группа выходов которого является группой выходов блока задержки, первый и второй входы элемента ИЛИ

являются первым и вторым входами блока задержки, выход элемента ИЛИ соединен с информационным входом регистра сдвига.

1

пуск

лТГ

0

EH

Редактор А.Долинич

Составитель Д.Ванюхин

Техред Л.Олейник. Корректор1А.Тяско

5233/50

Тираж 671 Подписное ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

- .

/7

Фи.г.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1191911A1 |

| Устройство для тестового контроля временных соотношений | 1987 |

|

SU1596337A1 |

| Устройство для контроля коммутационной системы | 1986 |

|

SU1401639A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Устройство для контроля цифровых узлов | 1990 |

|

SU1756894A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для поиска неисправностей в сложных цифровых схемах. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения контро ля момента появления выходных сигналов контролируемого узла. Устройство содержит блок памяти тестов, счетчик адреса, группу ключей, блок сравнения, индикатор, мультиплексор, блок задержки, содержащий элемент ИЛИ, регистр сдвига и генератор тактовых импульсов. 2 ил.

| Устройство для диагностики неисправностей цифровых блоков | 1981 |

|

SU1024925A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Автооское | |||

| Устройство для тестового контроля цифровых узлов цифровой вычислительной машины | 1975 |

|

SU618742A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-30—Публикация

1985-03-15—Подача