Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах на базе ЭВМ,

Целью изобретения является расширение функциональных возможностей устройства за счет осуществления контроля выполнения тестовой программы системы на базе ЭВМ и автоматического запуска системы при начальном включении или в случае сбоя.

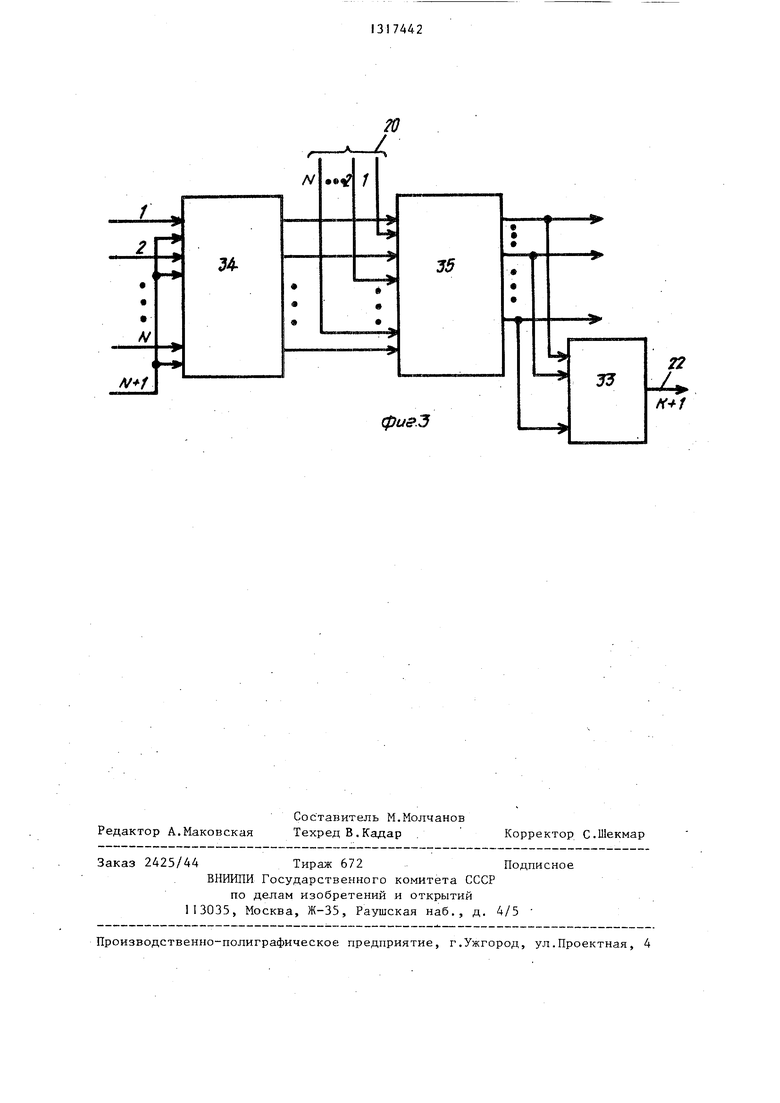

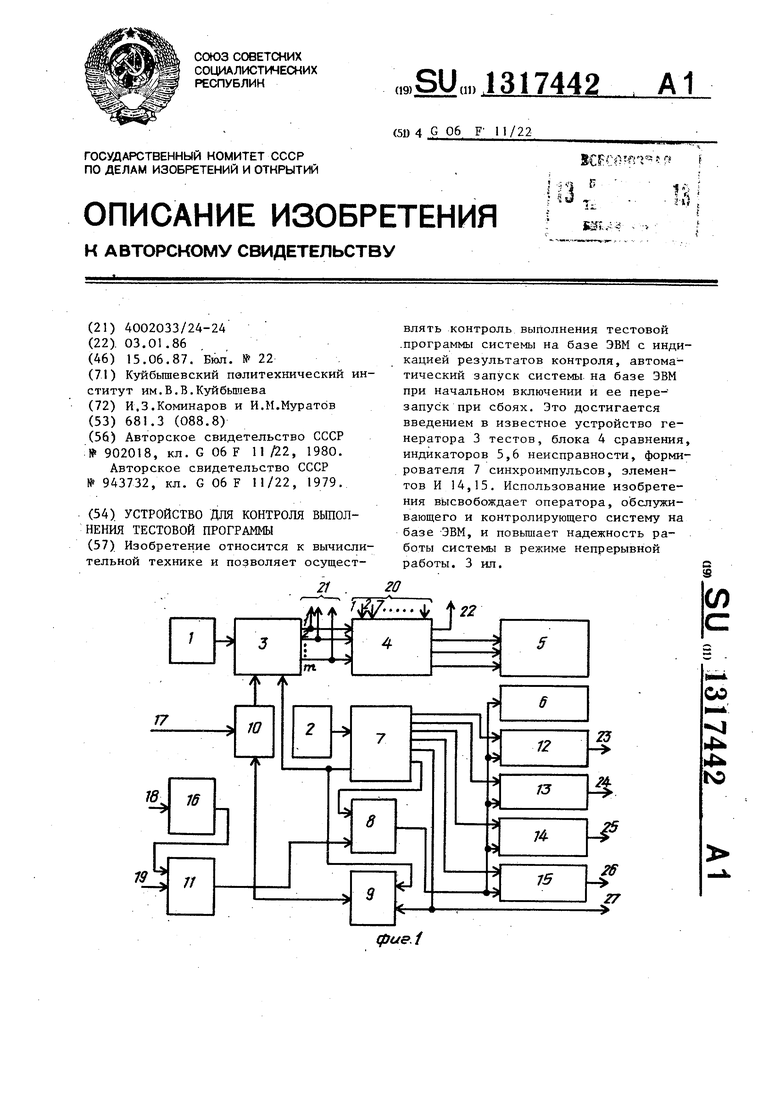

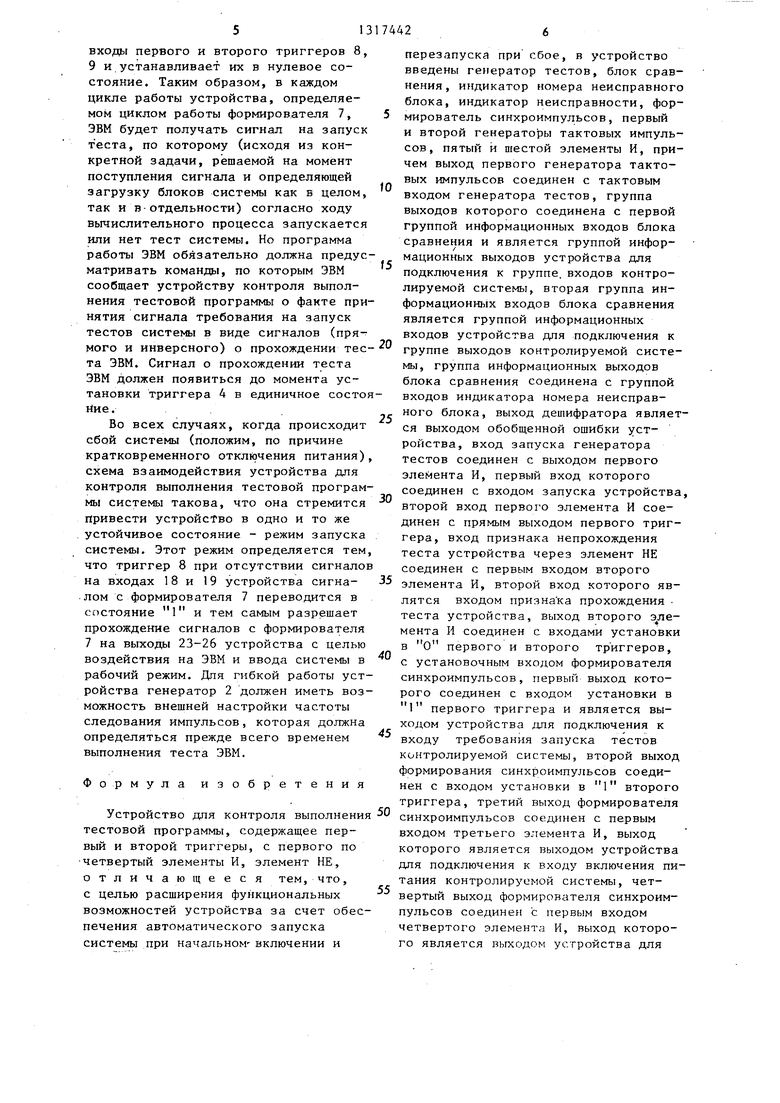

На фиг.1, изображена структурная схема устройства дпя контроля выполнения тестовой программы системы на базе ЭВМ; на фиг.2 - структурная схема генератора тестОв; на фиг.3 - структурная схема блока сравнения.

Устройство содержит первый 1 и второй 2 генераторы тактовых импульсов, генератор 3 тестов, блок 4 сравнения , индикатор 5 номера неисправного блока системы, индикатор 6 неисправности, формирователь 7 синхроимпульсов , первый 8 и второй 9 триггеры, с первого по шестой элементы И 10-15, элемент НЕ 16, вход 17 запуска устройства, входы 18 и 19 признаков непрохождения и прохождения теста, группу информационных входов 20 устройства, группу информационных выходов 21 устройства, выходы устройства 7.7. - 21 для подключения к входу включения питания, тактовому входу, входу начальной установки, входу запуска и входу запуска тестов контролируемой системы.

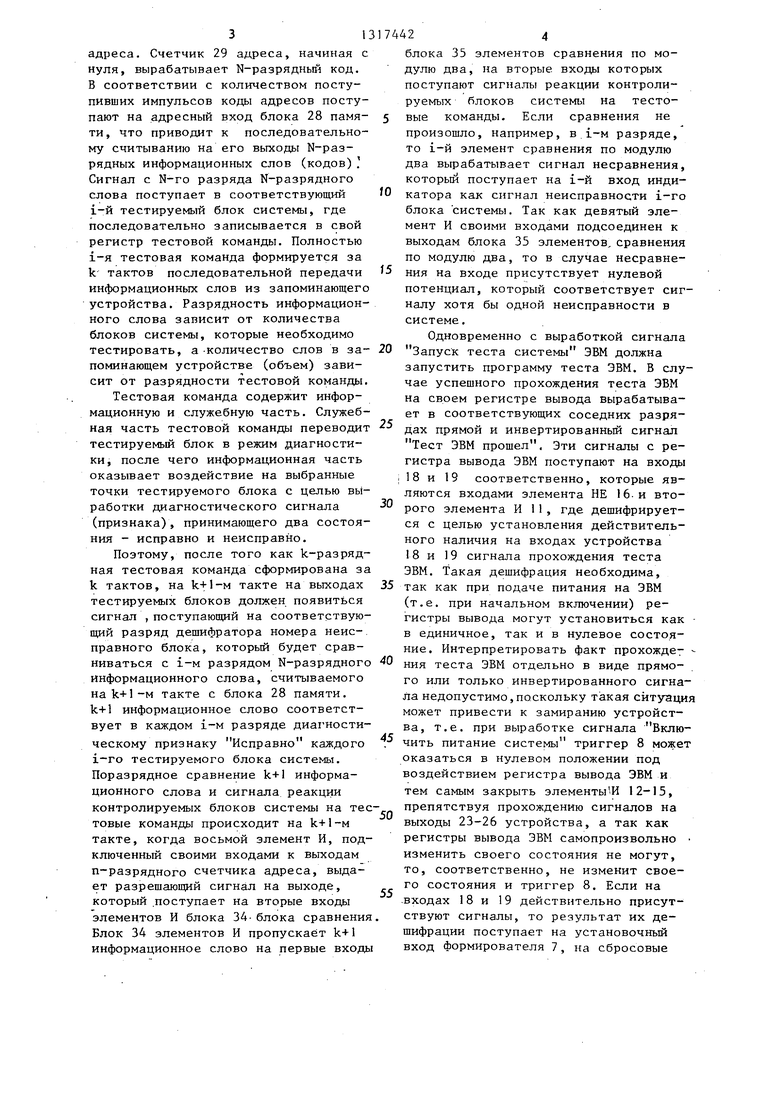

Генератор тестов содержит блок 28 памяти, счетчик 29 адреса, триггер 30, первый 31 и второй 32 элементы И,

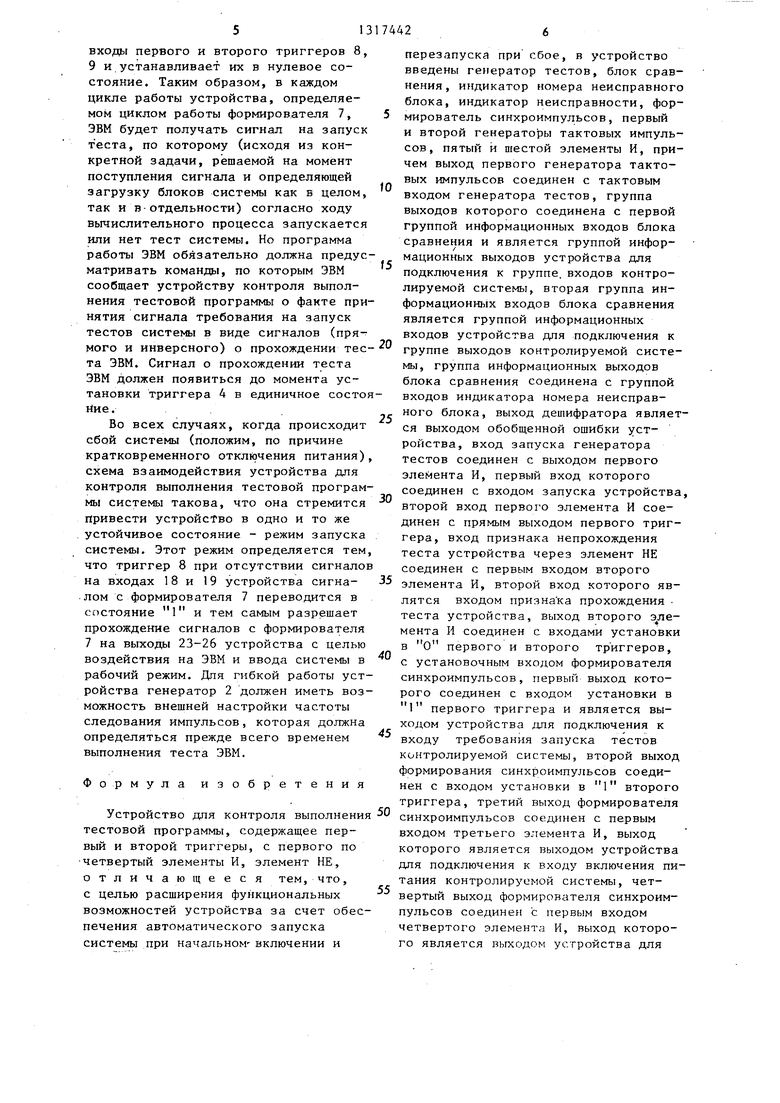

Блок 4 сравнения содержит элемент И 33, блок 34 элементов И, блок 35 элементов сравнения по модулю два.

Устройство работает следующим образом.

После общего включения системы элементы устройства находятся в случайном состоянии. При появлении питающего напряжения запускаются генераторы 1 и 2, которые начинают вырабатывать импульсы прямоугольной формы с заданным периодом. Импульсы с выхода генератора 2 поступают на первый вход форьшрователя 7 синхроимпульсов, в результате чего на его выходах последовательно во времени появляются синхроимпульсы. Пусть после начального включения первый триг

5

гер 8 установился в нулевое состояние, тогда импульсы с первого, второго, третьего и четвертого выходов формирователя 7 синхроимпульсов проходят через третий, четвертый, пятый и шестой элементы И 12-15 (на вторых входах присутствует нулевой потенциал, поступающий с выхода триггера 8). Далее импульс с пятого выхода формирователя 7 синхроимпульсов поступает в ЭВМ в виде сигнала требова-, ния на запуск тестов системы. Поскольку ЭВМ находится в нерабочем состоянии, то реакция на этот сигнал в ЭВМ

0

5

0

отсутствует. Затем с шестого выхода распределителя временных импульсов поступает сигнал на установочный вход триггера 8, под воздействием которого триггер переводится в единичное, состояние. Это состояние фиксируется индикатором 6 неисправности. Далее цикл выработки формирователем 7 синхроимпульсов повторяется. Импульсы вновь поступают на первые-, входы элементов И 12-15, а так как триггер 8 продолжает находиться в единичном состоянии, то эти сигналы поступают на выходы 23-26 устройства и далее на входы ЭВМ как сигналы включения питания системы и ЭВМ, запуска тактового генератора ЭВМ, установки начального адреса рабочих программ ЭВМ, пуска рабочих программ ЭВМ . После чего с пятого выхода формирователя 7 синхроимпульсов с задержкой С , определяемой периодом следования импульсов с выхода тактового генератора 2, появляется импульс, одновременно поступающий,, на установочный вход второго триггера 9 и на выход 27 устройства в виде сигнала требования запуска тестов системы. Если запуск ЭВМ и системы в целом осуществляется за время , то ЭВМ реагирует на этот сигнал и выдает разрещение в виде сигнала запуска теста системы на вход 17 устройства, который через первый элемент И 10 поступает на запускающий вход генератора тестовых команд.

В генераторе 3 тестов сигнал запуска теста системы поступает на установочный вход третьего триггера 30 и переводит его в единичное состояние, открывая тем самым клапан (седьмой элемент Н 31), который начинает пропускать импульсы с генератора 1 на счетный вход счетчика 29.

0

5

0

5

адреса. Счетчик 29 адреса, начиная с нуля, вырабатывает N-разрядньй код. В соответствии с количеством поступивших импульсов коды адресов поступают на адресный вход блока 28 памяти, что приводит к последовательному считыванию на его выходы N-раз- рядных информационных слов (кодов). Сигнал с N-ro разряда N-разрядного слова поступает в соответствующий i-й тестируемый блок системы, где последовательно записывается в свой регистр тестовой команды. Полностью i-я тестовая команда формируется за k тактов последовательной передачи информационных слов из запоминающего устройства. Разрядность информационного слова зависит от количества блоков системы, которые необходимо тестировать, а -количество слов в запоминающем устройстве (объем) зависит от разрядности тестовой команды.

Тестовая команда содержит информационную и служебную часть. Служебная часть тестовой команды переводит тестируемый блок в режим диагностики, после чего информационная часть оказывает воздействие на выбранные точки тестируемого блока с целью выработки диагностического сигнала (признака), принимающего два состояния - исправно и неисправно.

Поэтому, после того как k-разряд- ная тестовая команда сформирована за k тактов, на k+1-м такте на выходах тестируемых блоков должен появиться сигнал , поступающий на соответствующий разряд дешифратора номера неисправного блока, который будет сравниваться с i-M разрядом N-разрядного информационного слова, считываемого на k+1-м такте с блока 28 памяти. k+1 информационное слово соответствует в каждом i-M разряде диагностическому признаку Исправно каждого i-ro тестируемого блока системы. Поразрядное сравнение k+1 информационного слова и сигнала реакции контролируемых блоков системы на тетовые команды происходит на k+1-м такте, когда восьмой злемент И, подключенный своими входами к выходам п-разрядного счетчика адреса, выдает разрешающий сигнал на выходе, который .поступает на вторые входы элементов И блока 34- блока сравнения Блок 34 элементов И пропускает k+1 информационное слово на первые входы

S

0

5

0

5

0

5

0

5

блока 35 элементов сравнения по модулю два, на вторые входы которых поступают сигналы реакции контролируемых блоков системы на тестовые команды. Если сравнения не произошло, например, в i-м разряде, то 1-й элемент сравнения по модулю два вырабатывает сигнал несравнения, который поступает на i-й вход индикатора как сигнал неисправности i-ro блока системы. Так как девятый элемент И своими входами подсоединен к выходам блока 35 элементов, сравнения по модулю два, то в случае несравнения на входе присутствует нулевой потенциал, который соответствует сигналу хотя бы одной неисправности в системе.

Одновременно с выработкой сигнала Запуск теста системы ЭВМ должна запустить программу теста ЭВМ. В случае успешного прохождения теста ЭВМ на своем регистре вывода вырабатывает в соответствующих соседних разрядах прямой и инвертированный сигнал Тест ЭВМ прошел, Эти сигналы с регистра вывода ЭВМ поступают на входы 18 и 19 соответственно, которые являются входами элемента НЕ 16-и второго элемента И 11, где дешифрируется с целью установления действительного наличия на входах устройства 18 и 19 сигнала прохождения теста ЭВМ. Такая дешифрация необходима, так как при подаче питания на ЭВМ (т.е. при начальном включении) регистры вывода могут установиться как - в единичное, так и в нулевое состояние. Интерпретировать факт прохожде- ния теста ЭВМ отдельно в виде прямого или только инвертированного сигнала недопустимо,поскольку такая ситуация может привести к замиранию устройства, т.е. при выработке сигнала Включить питание системы триггер 8 может оказаться в нулевом положении под воздействием регистра вывода ЭВМ и тем самым закрыть элементы И 12-15, препятствуя прохождению сигналов на выходы 23-26 устройства, а так как регистры вывода ЭВМ самопроизвольно изменить своего состояния не могут, то, соответственно, не изменит своего состояния и триггер 8. Если на входах 18 и 19 действительно присутствуют сигналы, то результат их дешифрации поступает на установочный вход формирователя 7, на сбросовые

513

входы первого и второго триггеров 8, 9 и устанавливает их в нулевое состояние. Таким образом, в каждом цикле работы устройства, определяемом циклом работы формирователя 7, ЭВМ будет получать сигнал на запуск т еста, по которому (исходя из конкретной задачи, решаемой на момент поступления сигнала и определяющей загрузку блоков системы как Б целом, так и в отдельности) согласно ходу вычислительного процесса запускается или нет тест системы. Но программа работы ЭВМ обязательно должна предусматривать команды, по которым ЭВМ сообщает устройству контроля выполнения тестовой программы о факте принятия сигнала требования на запуск тестов системы в виде сигналов (прямого и инверсного) о прохождении теста ЭВМ. Сигнал о прохождении теста ЭВМ должен появиться до момента установки триггера 4 в единичное состоя йие.

Во всех случаях, когда происходит сбой системы (положим, по причине кратковременного отключения питания) схема взаимодействия устройства для контроля выполнения тестовой программы системы такова, что она стремится Привести устройство в одно и то же устойчивое состояние - режим запуска системы. Этот режим определяется тем что триггер 8 при отсутствии сигналов на входах 18 и 19 устройства сигна- лом с формирователя 7 переводится в состояние 1 и тем самым разрешает прохождение сигналов с формирователя 7 на выходы 23-26 устройства с целью воздействия на ЭВМ и ввода системы в рабочий режим. Для гибкой работы устройства генератор 2 должен иметь возможность внещней настройки частоты следования импульсов, которая должна определяться прежде всего временем выполнения теста ЭВМ.

Формула изобретения

Устройство для контроля выполнения тестовой программы, содержащее первый и второй триггеры, с первого по четвертый элементы И, элемент НЕ, отличающееся тем, что, с целью расщирения функциональных возможностей устройства за счет обеспечения автоматического запуска системы при начальном включении и

7442

5

0

5

0

5

0

5

0

5

перезапуска при сбое, в устройство введены генератор тестов, блок сравнения , индикатор номера неисправного блока, индикатор неисправности, формирователь синхроимпульсов, первый и второй генераторы тактовых импульсов, пятый и щестой элементы И, причем выход первого генератора тактовых импульсов соединен с тактовым входом генератора тестов, группа выходов которого соединена с первой группой информационных входов блока сравнения и является группой информационных выходов устройства для подключения к группе, входов контролируемой системы, вторая группа ин- формационнь1х входов блока сравнения является группой информационных входов устройства для подключения к группе выходов контролируемой системы, группа информационных выходов блока сравнения соединена с группой входов индикатора номера неисправного блока, выход дешифратора является выходом обобщенной ошибки устройства, вход запуска генератора тестов соединен с выходом первого элемента И, первый вход которого соединен с входом запуска устройства, второй вход первого элемента И соединен с прямым выходом первого триггера, вход признака непрохождения теста устройства через элемент НЕ соединен с первым входом второго элемента И, второй вход которого яв- лятся входом призна ка прохождения теста устройства, выход второго мента И соединен с входами установки в о первого и второго триггеров, с установочным входом формирователя синхроимпульсов, первый выход которого соединен с входом установки в 1 первого триггера и является выходом устройства для подключения к входу требования запуска тестов контролируемой системы, второй выход формирования синхроимпульсов соединен с входом установки в 1 второго триггера, третий выход формирователя синхроимпульсов со€ дннен с первым входом третьего элемента И, выход которого является выходом устройства для подключения к входу включения питания контролируемой системы, четвертый выход формирователя синхроимпульсов соединен с первым входом четвертого элемента И, выход которого является выходом устройства для

подключения к тактовому входу контролируемой системы, пятый выход формирователя синхроимпульсов соединен с первым входом пятого элемента И, выход которого является выходом устройства для подключения к входу начальной установки контролируемой системы. Шестой выход формирователя

28

J/

синхроимпульсов соединен с первым входом шестого элемента И, выход которого является выходом устройства для подключения к входу запуска контролируемой системы, выход второго триггера соединен с вторыми входами с третьего по шестой элементов И и с входом индикатора неисправности.

21

tt 2 .

/

S2

2В

фаг.2

Редактор А.Маковская

Составитель М.Молчанов Техред В. Кадар

Заказ 2425/44Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для формирования тестов диагностики дискретных блоков | 1983 |

|

SU1149265A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для локализации неисправностей | 1985 |

|

SU1339564A1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

Изобретение относится к вычислительной технике и позволяет осущест// . влять контроль выполнения тестовой .программы системы на базе ЭВМ с индикацией результатов контроля, автоматический запуск системы на базе ЭВМ при начальном включении и ее пере- запуск при сбоях. Это достигается введением в известное устройство генератора 3 тестов, блока 4 сравнения, индикаторов 5,6 неисправности, формирователя 7 синхроимпульсов, элементов И 14,15, Использование изобретения высвобождает оператора, обслуживающего и контролирующего систему на базе ЭВМ, и повышает надежность работы системы в режиме непрерывной работы. 3 ил. ff (Л со vl 4 4 ГС (pue.i

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля выполнения тестовой программы | 1979 |

|

SU943732A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-15—Публикация

1986-01-03—Подача