Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах управления, кольцевых коммутаторах, в преобразователях кодов, в програм.1но-временных устройствах и т.д. Известны схемы реверсивных сдвигаю щих регистров l и 23 построенные на основе Д- или Т-триггеров и схема реверсивной передачи межразрядной информации, схемы с дублированием плеч в триггере памяти, схемы с дублированием схем, принимающих информацию Однако,обладая определенными достоинствами, каждая из разновидностей схем имеет и некоторые недостатки такие, как наличие опасных состязаний, относительно невысокое быстродействие, сложность структуры. Наиболее близким по технической сущности с предлагаемому является реверсивный сдвигающий регистр, имею щий шину подачи сигнала сдвига и две шины для подачи парафазного сигнала реверса, построенный на элементах ИЛИ-НЕ (И-HEi, каждый разряд которог содержит триггер приема информации и триггер передачи информации, выполненный с дублированием плеч, од но из которых по сигналу реверса включается для передачи информации в последующий разряд, а второе - в предыдущий зЗ. Недостатком этой схемы является сложность структуры и относительно невысокое быстродействие. Цель изобретения - увеличение быстродействия за счет одновременного осуществления режимов гашения и перезаписи в триггере приема и хранения информации и ее упрощение. Поставленная цель достигается тем, что в ячейку памяти для реверсивного регистра сдвига, содержащую триггер приема и хранения информации, триггер передачи информации, шины управлен ;я реверсом и первую шину управления сдвигом/ введены вторая и третья шины управления сдвигом, причем первый вход установки О триггера передачи информации соединен с первой шиной управления реверсом, первая шина управления сдвигом подключена ко входу гашения триггера передачи информации, единичный и нулевой выходы триггера приема и хранения информации соединены соответственно со входом установки в 1 и со вторым входом установки О триггера передачи ийформации третий вход установки-О которого подключен к нулевому выходу триггера приема и хранения информации, четвертый вход установки О триг.гера передачи соединен со второй шиной управления реверсом, вход установки О триггера приема и хранения информации соединен с третьей шиной управления сдвигом.

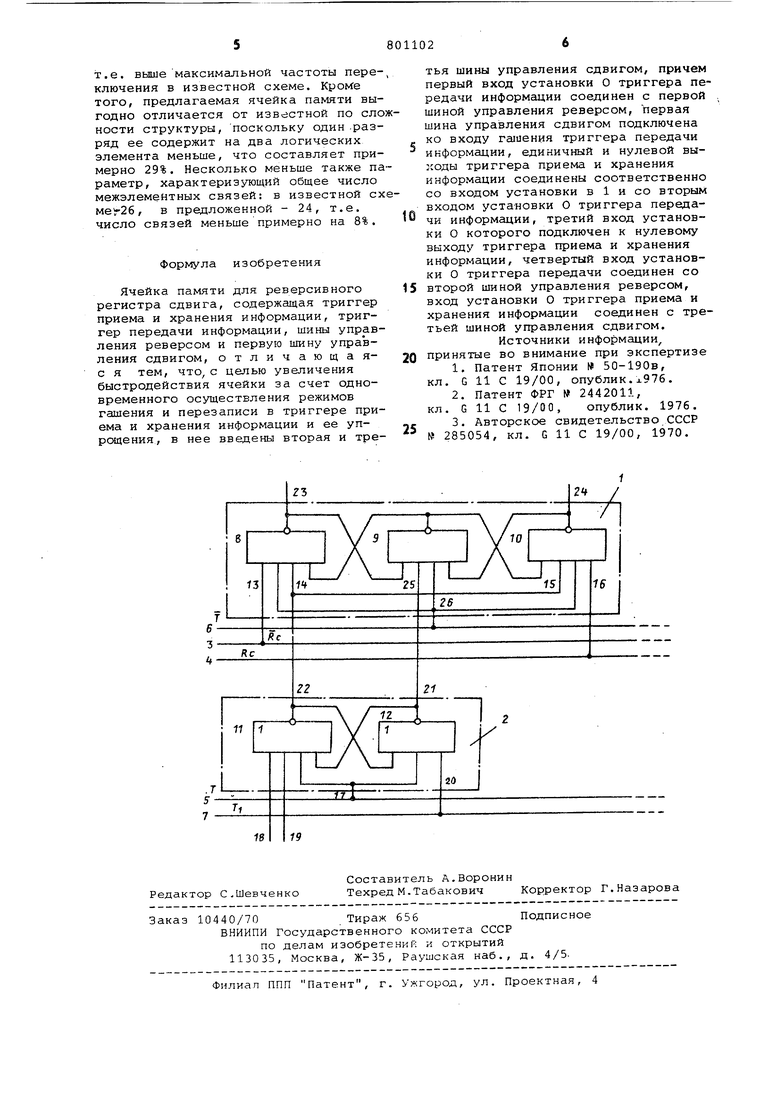

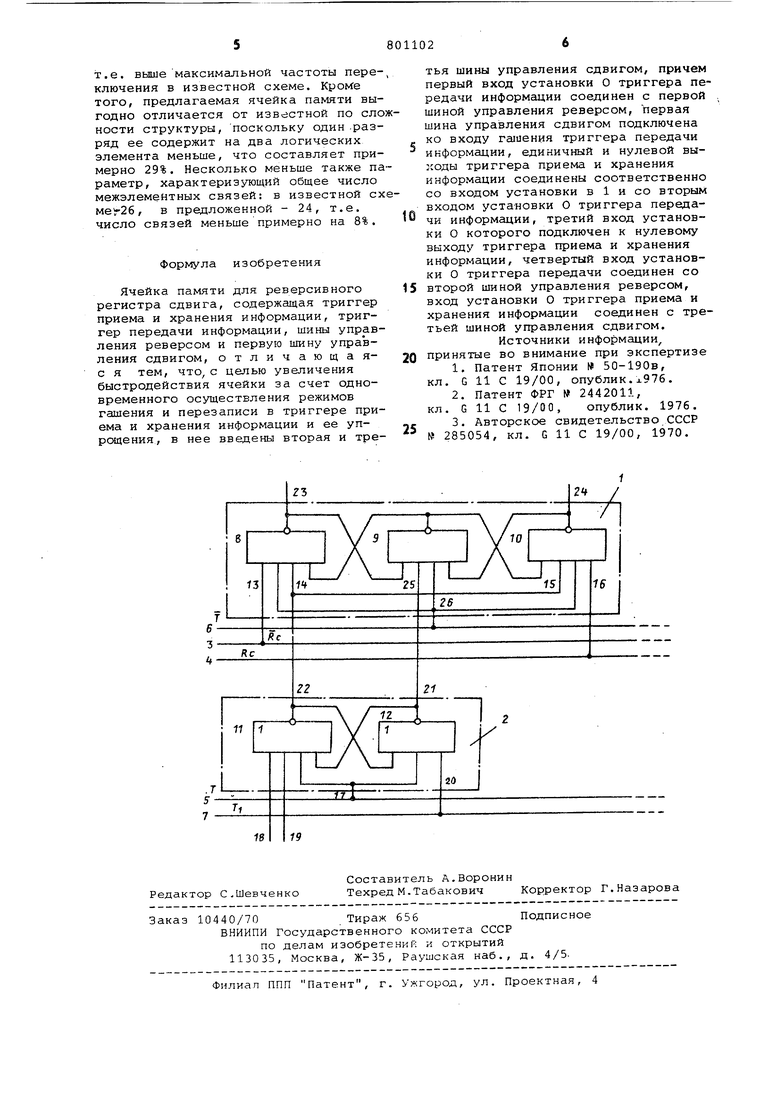

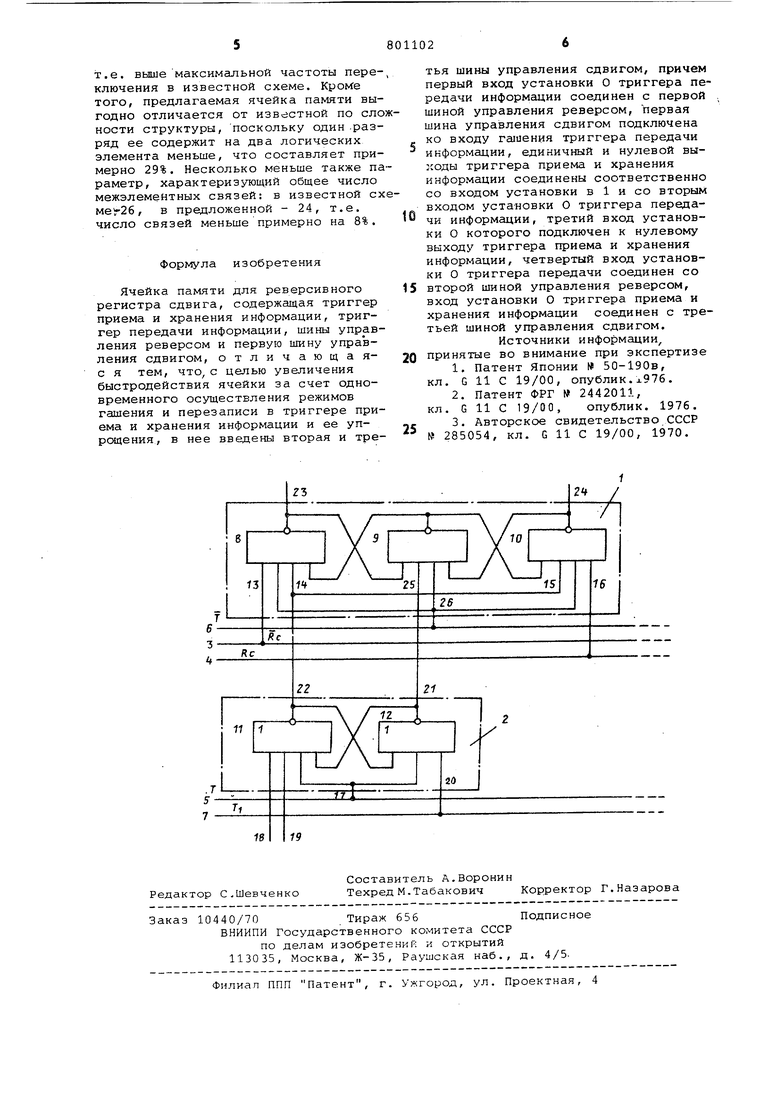

На чертеже изображена функциональная схема ячейки памяти.

Схема содержит триггер 1 передачи информации,триггер 2 приема и хранения информации,шины 3 и 4 управления реверсом,шины 5-7 управления сдвигом элементы ИЛИ-НЕ 8-10, на которых выполнен триггер 1, элементы ИЛИ-НЕ 11-12, на которых выполнен триггер 2 входы 13-16 установки О триггера 1, вход 17 гашения триггера 2,входы 18 и 19 установки 1 триггера 2,вход 20 установки в нулевое соетояние,выходы 21 и 22 триггера 2, 23 и 24 триггера 1, вход 25 установки 1 триггера 1 и вход 26 гашения триггера 1.

Работает ячейка памяти -„ледующим образом.

Направление сдвига информации определяется значением сигнала реверса на шинах 3 и 4. Если сигналы , ( i , то ячейка памяти подготовлена к режиму прямого сдвига, т.е. от предыдущего разряда к следующему, если R l, R,0 , то ячейка памяти подготовлена к обратному сдвигу Сначала рассмотрим режим прямого сдв га. Если сигналы на шинах 3 и 4 , то сигнал на выходах 23 и 24 триггера 1 передачи информации будет равен нулю независимо от характера сигналов на всех остальных входах этого триггера. В исходном состоянии, т.е. если сигналы на шинах , , триггер 1 передачи информации находится в фазе гашения, а триггер 2 находится в режиме хранения информации. Пусть триггер 2 рассматриваемого разряда находится в единице (0,- 1 ) , триггер памяти предыдущего и-следующего разрядов {не показаны на чертеже) находится в нулевом состоянии (9;. 0,0| + 0). При изменении потенциалов на шинах 5 и 6 на противоположные, т.е. , триггеры 2 всех разрядов через время Tj f равное средней задержке в одном элементе ИЛИ-НЕ, перейдут в фазу гашения информации, а триггеры 1 передачи информации во всех пазрядах в то же самое время перейдут в состояние, которое занимали триггеры 2 этих разрядов, т.е. триггер i- го разряда перейдет в единичное состояние, поскольку в течение интеВсша времени с Г., единично

входе имеет место высокий потенциал, равный 2 , а на нулевом - низкий, равный 0| . Триггеры (i +- 1)-го и (i - 1)- го разрядов перейдут в нулевое состояние, в силу того, что в с течение того же самого интервала

t Z на их нулевых входах имеет место высокий потенци ал, равный соответственно 9|-/. и 0j. а на единичных - низкий, равный соответственно

QI-I этом состоянии регистр находится, пока Т 1, Т О. При изменении сигнала сдвига (Т О, Т 1) триггеры 1 передачи информации всех разрядов через время г Г, перейдут в фазу гашения, а триггеры

5 2 приема и хранения информации в то же самое время перейдут в состояние, которое занимали триггеры 1 передачи информации предыдущих разрядов, т.е. триггер 2 г-го перейдет

0 в нулевое состояние, триггер 1

(1 -f 1)-го разряда перейдет в единичное состояние и т.д. Рассмотрим подробнее этот процесс, предварительно заметив, что сигнал т должен задерживаться по отношению к сигналу Т на времядtit . Поскольку при изменении сигнала Т от значения, равного единице, к значению, равному нулю, на входе 17 гашения триггера 2 изме.. нение происходит раньше, чем на его входе 20, то триггер 2 переходит из состояния гашения в нулевое, если на его входе 18 или 19 сигнал равен нулю. Если же на единичном входе 18 или 19 сигнал равен единице, то в те чение интервала времени л-ё после прекращения действия сигнала Т триггер 2 остается в фазе гашения, а затем переходит в единичное состояние, поскольку в течение интервала времени Тз - Д т входе 18 и 19 имеет место высокийпотенциал, а на входе 20 низкий.

Работа ячейки памяти обратного сдвига, т.е. когда RC 1 , R..- О, аналогична.

Поскольку в предложенной ячейке памяти процессы гашения информации в триггере 2 и переписи ее в триггер 1 передачи протекают одновременно, причем это время равно задержке в одном элементе, то минимальная длительность импульса сдвига должна быть не меньше этой згщержки. Длительность паузы должна быть несколько больше, поскольку процесс переписи информации из триггера 1 передачи в триггер 2 в случае единичного значения ее задерживается на величину , следовательно даже в предельном случае эта. длительность не больше 2 Tj , следовательно максимальная частота импульсов сдвига равна

JL

f таГ- i

Ъ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный сдвигающий регистр | 1979 |

|

SU926718A2 |

| Реверсивный регистр сдвига | 1989 |

|

SU1817135A1 |

| Реверсивный регистр сдвига | 1989 |

|

SU1642527A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU875459A1 |

| Регистр сдвига | 1980 |

|

SU879652A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1392573A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1098006A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1991 |

|

RU2022372C1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

Авторы

Даты

1981-01-30—Публикация

1979-03-19—Подача