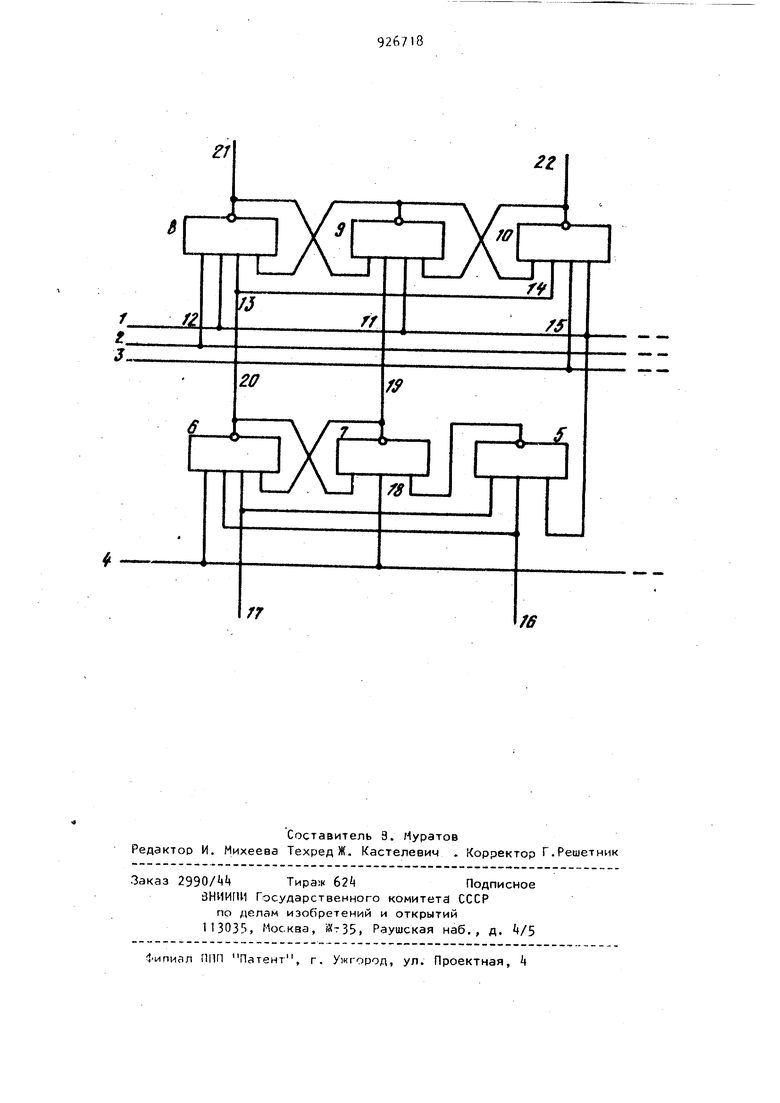

Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах управления, кольцевых коммутаторах, в преобразователях кодов, в программно временных устройствах. По основному авт. св. № 801102, известен реверсивный сдвигающий регистр, имеющий шины управления для подачи прямого, инверсного и задержанного прямого значений сигнала сдвига, а также две шины для подачи парафазного сигнала, реверса, и пост роенный на элементах ИЛИ-НЕ, каждый разряд которого содержит триггер приема и хранения информации, выполняющий также функции триггера памяти и триггер передачи информации, выполненный с дублированием плеча, одно ИЗкоторых по сигналу реверса включается для передачи информации . в последующий разряд, а второе - в предыдущий 1 . Недостатком известного регистра является то, что при больших разбросах задержек в логических элементах триггера передачи и хранения информации и триггера памяти могут иметь место сбои в процессе перепи-си информации из триггера передачи в триггер памяти. Цель изобретения - увеличение надежности регистра. Поставленная цель достигается тем, что в каждый разряд реверсивного сдвигающего регистра введен трехвходовой элемент ИЛИ-НЕ, первый и второй входы которого подключены к соответствующим S-входам триггера приема и хранения информации, третий вход подключен к шине управления сдвигом, а выход каждого элемента ИЛИ-НЕ, подключен к нулевому входу триггера приема и хранения информации. На чертеже представлен один раз ряд предлагаемого реверсивного сдвигающего регистра. 3. 9 РЧ;гистр содержит шины управления, а именно шину 1 для подачи инверс ного значения сигнала, сдвига Т - шину 2 для подачи инверсного значения сигнала реверса RC. шину 3 для подачи прямого значения сигнала реверса R(-., и шину k для подачи прямого значения сигнала сдвига Т. Схема одного разряда регистра содержит триггер приема и хранения информации (памяти), триггер передачи информации и трехвходовой логический элемент ИЛИНЕ 5 выполняющий функции схемы формирования сигнала перевода триггера памяти в нулевое состояние. Триггер памяти собран по схеме RS на элементах 6 и Триггер передачи информации собран по схеме .RS с дублирова нием единичного плеча на элементах 8, 9и 10. Триггер передачи информации имеет один общий вход 11 установки в единичное состоние, один общий вход гашения информации, образованный путем соединения с шиной 1 одного входа элемента 8, одного входа элемента 9 |и одного входа элемента 10, а также по два в каждом плече входа 12,13 и I, 15 установки в нулевое состояние. Триггер памяти имеет вход гашения информации,образованный путем соединения с шиной 4 одного входа элемента 6 и одного входа элемента 7. два входа 16 и 17 установки в единич ное состояние и один вход 18 установки в нулевое состояние.Вход 11 соединен с единичным (Q.) выходом 19 .триггера памяти, в;код 12 - с шиной 2, вход 13 - со входом 1 и подсоединен к нулевому (Q ) выходу 20 триг гера памяти. Один единичный выход 21 триггера передачи информации соединен с единичным входом триггера памя ти предыдущего разряда, а второй еди ничный выход 22 - с единичным входом триггера памяти следующего разряда. Вход 16 соединен с правым единичным выходом триггера передачи информации предыдущего разряда, вход 17 - с левым единичным выходом триггера передачи информации следующего разряда. Зход 18 соединен с выходом элемента 5. Один вход элемента Б соединен со входом 16,, второй - со входом 17, третий - с шиной 1. Устройстэо работает следующим об разом. 84 Направление сдвига информации оп ределябтся значением сигнала реверса: если Rj, О, RC 1 то регистр подготовлен к режиму прямого сдвига, т.е. от предыдущего разряда к следующему, если RC, 1, RC О регистр подготовлен к обратному сдвигу. Рассмотрим режим прямого сдвига. При RC, О, RC, 1 сигнал на выходах левых плеч триггеров передачи информации во всех разрядах регистра равен нулю независимо от характера сигналов на всех остальных входах этих триггеров. Сигналы на выходах правых плеч определяются характером сигнала сдвига и характером сигналов на выходах триггеррв памяти. 3 исходном состоянии (т О, Т 1.) триггеры /передачи информации во всех разрядах регистра находятся в фазе гашения ,а три|- геры памяти - в режиме хранения информации. Пусть триггеры памяти рассматриваемого и предыдущего разрядов находятся в нулевом состоянии (Q - О, Q 1, Q-1 О, Qi--j 1). При изменении потенциалов на шинах сигнала сдвига на противоположные (Т 1, Т 0) триггеры памяти во всех разрядах регистра через время Т , равное средней задержке в одном логическом элементе, переходят в фазу гашения информации (Q Q О), а триггеры передачи информации во всех разрядах в то же самое время переходят из фазы в состояние, которое занимали триггеры памяти этих разрядов, т.е. триггеры (i-l)-ro и i-ro разрядов переходят в нулевое состояние, в силу того что в течение интервала времени t Со, на их нулевых входах имеет место высокий потенциал, равный соответственно Q:. |, а на единичных - низкий, равный соответственно Q д-1, Q .в этом состоянии Т 1 , Т 0. На выходах элементов формирования сигнала перевода триггеров памяти в нулевое состояние имеет место высокий потенциал, поскольку на его входах потенциал низок. При изменении сигнала сдвига (Т 0, Т 1) триггеры передачи информации во всех разрядах через время t р з переходят в фазу- гашения, а триггеры памяти в . то же время переходят из состояния гашения .в состояние, которое занимали триггеры передачи инфор/ ации, предыдущих разрядов. 3 частности, в рассматриваемом разряде триггер ппмяти переходит в нулевое состояние.поскольку в течение времени t -) на его нулевом входе -имеет место высокий потенциал, определяемый потенциалом на выходе элемента 5. Для случая Q,- 1| Q:)-,, О переход-триггера памяти i-ro разряда после окончания действия импульса сдвига аналогичен.

Если в исходном состоянии Q,. О, 1 то во время действия импульса сдвига (т 1, Т 0) триггер передачи информации {i-1)-ro разряда пе:реходитв единицу,а i-ro разряда - в нулевое состояние. После окончания действия импульса (Т О, Т 1) триг гер памяти i-ro разряда переходит в единичное состояние, поскольку на его нулевом (входе на выходе элемента 5) имеет место низкий потенциал, а на единичном выходе в течение времени t имеет место высокий потенциал, определяемый потенциалом на единичном выходе триггера передачи информации (i.-l)-ro разряда. Аналогичным является переход триггера памяти i-ro разряда после окончания действия импульса сдвига, если в исходном состоянии Q- 1, Q.i я 1.

Таким образом, во всех случаях в отсутствие импульса сдвига (Т О, Т 1) триггеры памяти во всех разрядах регистра находятся в состоянии хранения информации, а триггеры передачи информации - в фазе гашения. 3ct время действия импульса сдвига происходит перепись информации в каждом разряде регистра из триггера памяти в триггер передачи информации с одновременным гешением информации в триггерах памяти, и в этом состояНИИ находится в течение всего времени действия импульса сдвига. После окончания действия импульса сдвига происходит перепись информации из триггера передачи информации предыдущих разрядов в триггеры памяти следующих разрядов с одновременным гашением информации в триггерах передачи С приходом следующего импульса сдвига роцессы -, повторяются и после .окончания действия его снова происхо|дит сдвиг на один разряд и т.д..

Поскольку в рассматриваемой схеме процесс переписи информации из триггеров передачи в триггеры памяти ,не зависит от разброса задержек в логических элементах триггеров, то надежность предлагаемого регистра выше известного.

Формула изобретения

Реверсивный сдвигающий регистр по авт. св. f 801102, отличающийся тем, что, с целью увеличения надежности регистра, в каждый разряд его введен трехвходовой элемент ИЛИ-НЕ, и второй входы которого подключены к соответствующим S-входам триггера приема и хранения информации, третий вход подключен к шине управления сдвигом, а выход каждого элемента ИЛИ-НЕ подключен к нулевому входу триггера приема и хранения информации.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР t, 801102, кл. G 11 С 19/00, 19-03.79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для реверсивногоРЕгиСТРА СдВигА | 1979 |

|

SU801102A1 |

| Регистр сдвига | 1980 |

|

SU879652A2 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Микропрограммное устройство управления с контролем и восстановлением | 1984 |

|

SU1242947A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Генератор псевдослучайных чисел | 1989 |

|

SU1691839A2 |

| Автоматизированный класс для контроля знаний обучаемых | 1984 |

|

SU1196938A1 |

Авторы

Даты

1982-05-07—Публикация

1979-05-10—Подача