1

Изобретение относится к импульсной технике/ в частности к схемам для запуска, остановки и контроля счетчика, и может быть использовано в различных цифровых схемах.требуюищх повышенной достоверное информации, в качестве двоичного или двоично-десятичного счетчика, работающего на сложение или вычитание, а также в качестве регистра для записи параллельной или последовательной информации, ее хранения и сдвига и может быть применено в устройствах автоматики и вычислительной техники.

Известен счетчик, содерягиций t счетные узлы, выходы старшихрйзрядов которых соединены с входгши мажоритарных элементов, выходы KOtopiaoi соединены через логические алементы с входами счетчика ll .

Недостатками этого счетчика являются ограниченные функциоигшьные возможности и низкая достоверность функционирования .

Известен также счетчи, содержавши блок мажоритарных элементов, первьш второй и третий регист и сумматор, выходы которого соединены с входгши. регистров, выходы которых соединены

с входами блока мажоритарных элементов t2l .

Недостаток счетчика зактаочается в невозможности реверсивного счета в двоичном и десятичном коде.

Цель изобретения - обеспечение реверсивного счета в двоичном и де-, сятичном кодах.

Поставленная цель достигается

0 тем, что в счетчик содержащий блок мажоритарных элементов, перш1й, второй и третий регастры и сукматор, которого соединены с входами регистров, выходы которых соединены

5 с входги ш блока мажоритарных элементов, введешз элементы И, И-НЕ, ИЛИ, первый, второй и третий элементы запрета и nepstxR и второй коьмутаторы, выходы котсфых соединены со входгили

0 сумматора, вход переноса которого соединен с выходе}м первого элемента запрета, первый и второй управляющие входа ксн4мутаторов соединены с выход u«i соответственно второго и

5 третьего элементов запрета, входы второго и третьего разрядов второго канала первого коммутатора соединены с выходом элемента И, входы второго и третьего разрядов третьего

0 канала первого кo в yтaтopa соединены с выходом элемента И-НЕ, с общей шиной соединены входы всех разрядов первого канала первогокоммутатора, входы первого и четвертого разрядов второго канала первого коммутатора, а также входы всех разрядов первого и четвертого каналов второго коммутатора, с шиной питания соединены вход первого и четвертого разрядов третьего канала первого коммутатора, входы всех разрядов второго и третьего каналов второго коммутатора соединены выходами блока мажоритарных элементо выход элемента ИЛИ соединен с такто.выми входами регистров, первые входы элемента ИЛИ, первого, второго и третьего элементов запрета соединены с входом сброса счетчика, а вторые входы элемента ИЛИ, первого, второго и третьего элементов запрета соединены соответственно с шинами записи и 11ервой,второй и третьей,управлякидими шинами четвертая управляющая шина соединена с первьнии входами элементов И и И-НЕ,остальные входы которых соединен с выходами блока мажоритарных элементов, а пятая, шестая и седьмая управляющие шины соединены соответственно с первыми, вторыми и третьими управляющими входами регистров.

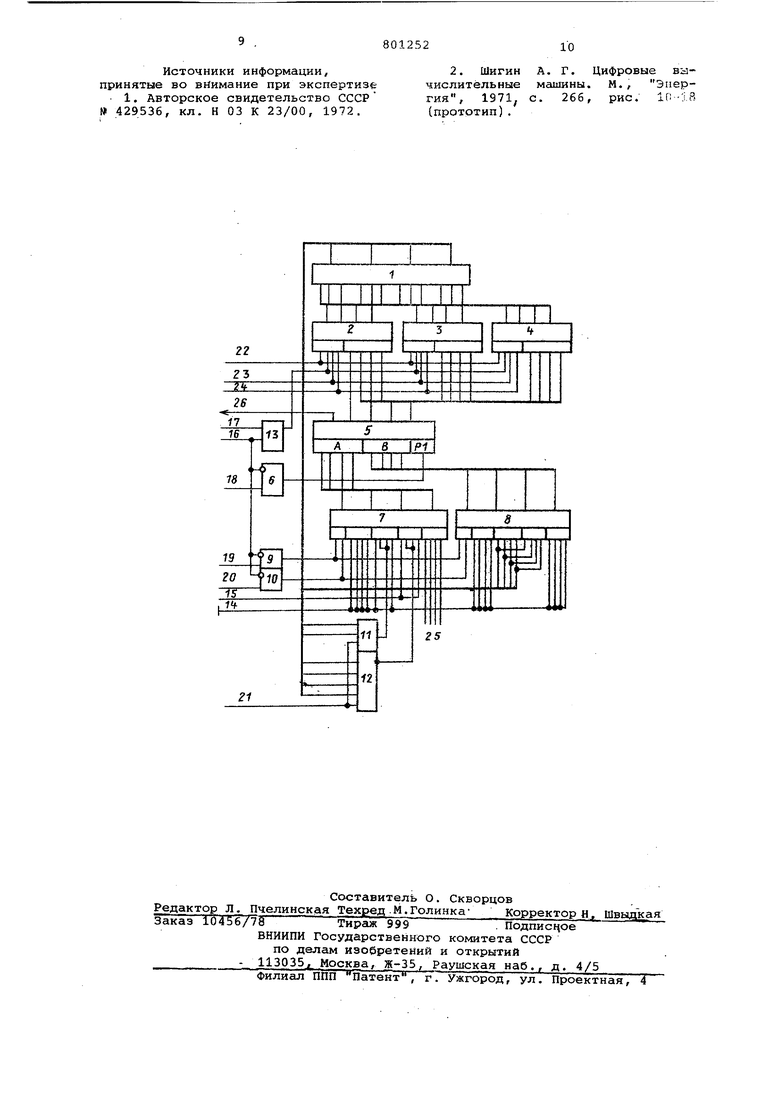

На чертеже показан счетчик, структурная схема.

Счетчик содержит блок мажоритарных элементов 1, первый 2, второй 3 и третий 4 регистры, cyNwaTOp 5, первый элемент б запрета первый 7 и второй 8 коммутаторы, второй 9 и третий 10 элементы запрета, элемент И 11, элемент И-НЕ 12 и элемент ИЛИ 13. Выходы сумматора 5 соединены с входами регистров 2, 3 и 4, выходы которых соединены с входами блока мажоритарньох элементов 1, выходы коммутаторов 7 и 8 соединены со входами сумматора 5, вход переноса которого соединен с выходом первого элемента запрета б первый и второй управляющие входы коммутаторов 7 и 8 соединены с выходами соответственно второго 9 и третьего 10 элементов запрета, входы второго и третьего разрядов второго канала первого коммутатора 7 соединены с выходом элемента И 11, входы второго и третьего разрядов третьего канала первого коммутатора 7 соединены с выходом элемента И-НЕ 12, с общей шиной 14 соединены входы всех разрядов первого канала первого коммутатора 7, входа первого и четвертого разрядов второго канала первого коммутатора 7, а также входы всех разрядов первого и четвертого каналов второго коммутатора 8, с шиной 15 питания соединены входы первого и четвертого разрядов третьего канала первого коммутатора 7 входы всех разрядов второго и третьего каналов вторюго коммутатора 8 соединены с выходами блока мажоритарных элементов 1, выход элемента ИЛИ 13 соединен с тактовыми входами регистров 2, 3 и 4, первые входы элемента ИЛИ 13, первого 6, второго 9 и третьего 10 эле-. ментов запрета соединены с входом сброса 16 счетчика, а вторые входы элемента ИЛИ 13, первого б, второго 9 и третьего 10 элементов запрета соеинены соответственно с шиной 17 записи и первой 18, второй 19 и третьей 20 управляющими шинами, четвертая управляющая шина 21 соединена с перг выми входами элементов И 11 и И-НЕ 12, остальные входы которых соединены с выходами блока мажоритарных элементов 1, а пятая 22, шестая 23, и седьмая 24 управлякяцие шины соединены соответственно с первыми, вторыми и третьими управляющими входами регистров 2, 3 и 4, Входы четвертого канала первого коммутатора соединены с параллельным входом 25 счетчика.

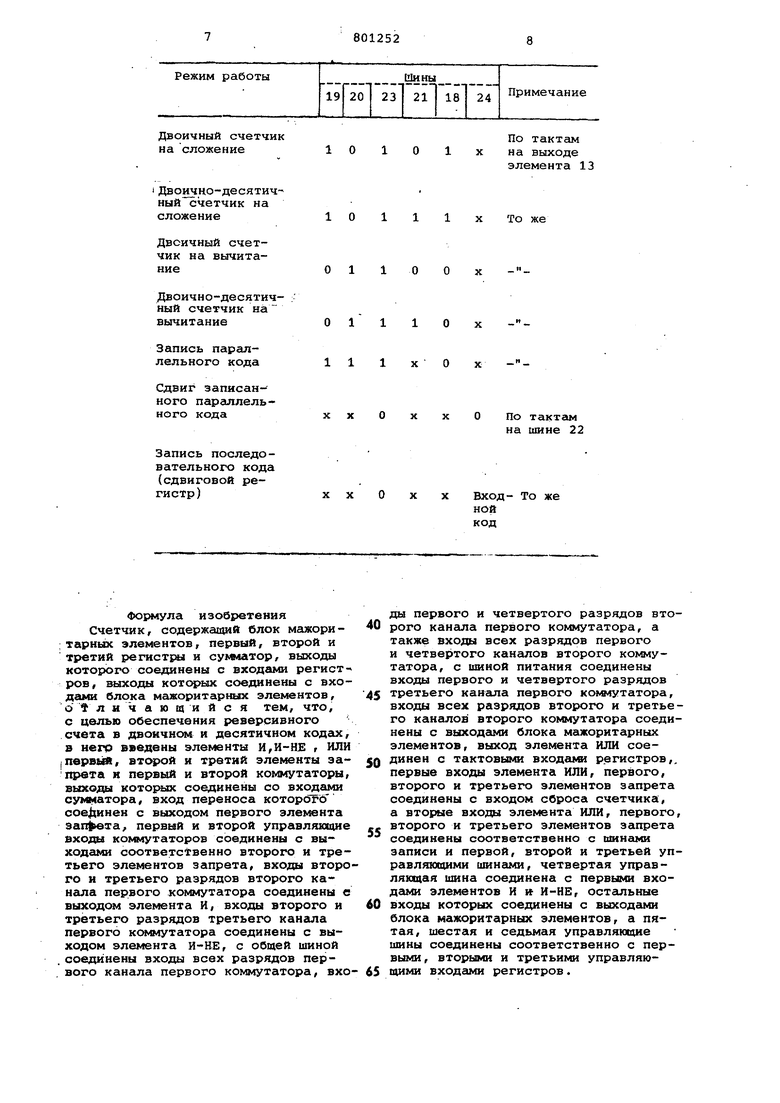

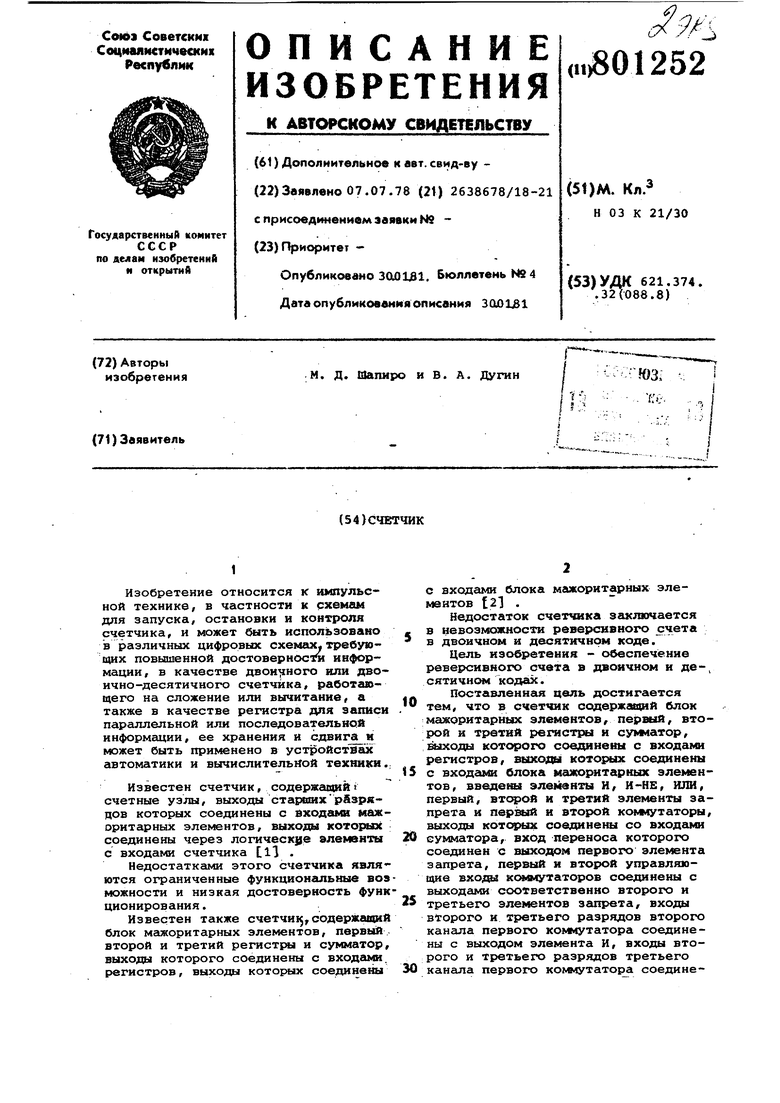

Шлбор режима работы производится подачей сигналов на управляющие входы в соответствии с таблицей, причем переключение происходит по сиг- налам подаваемым на шину 22 при сдвиге параллельного кода и записи последовательного кода.

Установка счетчика в нулевое состояние происходит по импульсу на шине 16, который блокирует сигналы на шинах 18, 19 и 20. с выхода запрета 9 и 10 элементов на управляющие входы коммутаторов 7 и 8 поступают сигналы, открывгиощие первые каналы, входы которых соединены с общей шиной 14. Таким образом на входы сумматора 5 поступаиот три числа: 0000 - на входа А сумматора 5 от коммутатора 77 0000 - на входы В сумматора 5 от коммутатора 8, О - на вход переноса cyNwaTopa 5 от элемента

6запрета ОООО - полученная сумма с выхода сулматора 5 по импульсу на шине 16, поступающему через элемент ИЛИ 13 на входы регистров 2, 3 и 4.

При работе в качестве двоичного счетчика на сложение управляющие сигналы устанавливаются в соответствии с таблицей. Сигналы на шинах 19 и 20 открывают вторые каналы коммутаторов

7и 8, После установки счетчика в 0-ое состояние на выходе сумматора

5 устанавливается число, равное сумме трех слагаегвлх 0000 - на входах А сумматора 5 от коммутатора 7 0000 - на входах В сумматора 5 от коммутатора 8, 1 - на входе переноса сумматора 5; 0001 - этот код по тактовому импульсу на шине 17 заносится в регистры 2, 3 и 4.

По второму тактовому импульсу на шине 17 в регистры 2, 3 и 4 из сумматора 5 будет записано число, рав-. нов суюле трех слагаемых: 0000 - на входах 4 сумматора 5 от коммутатоа 7, 0001 - на входах В сумматора

5 от коммутатора 8; 1 - на входе переноса сумматора 5j 0010 - сумма коров и т.д.

TaKtiM образом, после каждого тактового импульса содержимое регистров 2, 3 и 4 увеличивается на единицу, что соответствует работе двоичного счетчика на сложение.

Режим работы двоично-десятичного счетчика на сложение отличается от работы десятичного счетчика на сложение тем, что управляющим сигналом на шине 21 включается элемент И 11, который участвует в формировании корректирующего кода. Входы логического элемента И 11 соединены с выходами 1-го и 4-го разрядов блока мажоритарных элементов 1. Когда содержимое регистров 2, 3 и 4 достигнет значения 1001 на входы А сумматора 5 с выхода коммутатора 7 поступает код ОНО, который суммируется с содержимым . регистров, поступающим на входы В сумматора 5 через второй канал коммутатора 8. С выходов сумматора 5 в регистры 2 , 3 и 4 по тактовому импульсу на шине 17 записывается число, равное сумме трех слагаемых: ОНО - число на входах А сумматора 5 fкорректирующий , 1001 - число на входах В сукилатора 5 1 - на входе переноса сумматора 5} 1-0000 полученная сумма.кодов. В регистры записывается число 0000 и на выходе 26 переноса сумматора 5 образуется единица переноса в следующую тетраду. Если значение числа, записанного в регистрах 2, 3 и 4 меньше 1001, то на входы А сумматора поступает число 0000 и работа счетчика до значения 1001 аналогична работе в режиме двоичного счетчика.

При работе универсешьного резервированного счетчика на вычитание в двоичном коде управляющие сигналы устанавливаются в соответствии с таблицей . Сигналы на шинах 19 и 20 открывают третьи каналы коммутаторов 7 и 8. Элемент И-НЕ 12 выктаочен. Допускаем, что в регистрах 2, 3 и 4 записано число 1101, тогда на выходе сумматора 5 устанавливается число, равное сумме трех слагаекых: 1111 на Выходах А сумматора 5 от первого коммутатора; 1101 - на выходах В сумматора 5 - число, записанное в регие pax 2,,3 и 4, О - на входе переноса сумматора 5, 1-1100 код, который по тактовому импульсу на шине 17 заносися в регистры 2, 3 и 4. Значение счечика уменьшилось на 1, что соответ ствует работе счетчика на вычитание. С выхода переноса сумматора в следующую тетраду посылается единица переноса.

При .вычитании двоично-десятичных чисел включается элемент-И-НЕ 12,

который формирует корректирующий код.поступающий на входы А сумматора только при значении числа, записанного в регистрах 2, 3 и 4 равного 0000. Например: 0000 - число на 5 входах В сумматора 5 - содержимое регистров, 2,3 и 4/ 1001 -число на рходах А сумматора 5 - корректирующий код, О - на входе переноса сумматора 5, 1001 - содержимое выхода Q сумматора, которое заносится в регистры 2, 3 и 4 по следующему тактовому импульсу на шине 17.

Если значение числа, записанного с в регистрах 2, 3 и 4 не равно 0000, то как и в случае двоичного вычитания на вход А сумматора 5 из коммутатора 7 поступает число 1111.

Запись параллельного кода происходит в соответствии с таблицей. Сигнс1лы на шинах 19 и 20 открывают четвертые каналы коммутаторов 7 и 8. Через коммутатор 7 на входы А сумматора 5 поступает входной код. На

входы В сумматора 5 от коммутатора 8 поступает код 0000. На шину 18 по|дается уровень логического нуля. С выхода сумматора 5 по импульсу на |Шине 17 в регистры 2,3 и 4 записы1вается код, соответствующий подан|ному на входы-25 четвертого канала IKOivBviyTaTopa 7. Если код, записанный в регистры, необходимо сдвинуть, то импульсы сдвига подаются на входы

регистров 2, 3 и 4 по шине 22, а управлявяцие сигналы устанавливаются в соответствии с таблицей. Запись последовательной информации происходит .по импульсам, поступающим по

шине 22, а входная информация подается на шину 24.

При работе универсального резервированного счетчика в режиме как двоичного, так и двоично-десятичного

счетчика на сложение и вычитание, помимо высокой надежности и достоверности содержимого, достигнутого за счет мажоритарного резервированиЯ| в каждом тактовом импульсе происходит коррекция содержимого любого из трех регистров при его случайном сбое. Это достигнуто благодаря логической обратной связи по блок мажоритарных элементов 1, второй и третий кансшы коммутатора 8,

входы В сумматора 5. Введение логичес ких элементовИ,И-НЕ,ИЛИ трех элементов запрета и двух четырехкангшьных коммутаторов существенно расширяет функциональные возможности универсального резервированного счетчика, дает возможность использовать его как многофункциональное устройство с высокой надежностью и достоверностью хранимой информации.

Режим работы

igpol 23 I 21 I 181 24 1 О 1 О 1 X на выходе

10 1 1 1 X то же

О 1 1 О О X

О 1 1 1 О X

11 1 X О X

X X О X X О по тактам

X X О X X Вход- То же

ины

Примечание

По тактам

элемента 13

на шине 22

НОЙ

код

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| УСТРОЙСТВО ГРУППОВОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ШАБЛОНОВ БИТ ПЕРЕМЕННОЙ РАЗРЯДНОСТИ | 2023 |

|

RU2809741C1 |

| Устройство для регенерации телеграфных посылок | 1985 |

|

SU1338080A2 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

Формула изобретения Счетчик, содержащий блок мажоритарных элементов, первый, второй и третий регистры и суквлатор, выходы которого соединены с входами регист-ров, выходы которых соединены с входгши блока мажоритарных элементов, о f ли чающийся тем, что, с целью обеспечения реверсивного счета в двоичном и десятичном кодгис, в него введены элементы И,И-Н , ИЛИ первьЕй, втсчиэй и третий элементы эапрвта н первый и второй коммутаторы, выходы которых соединены со входакш сумиатора, вход переноса которого соединен с выходом первого элемента , первый и второй управляющие входа коквчутаторов соединены с выход 1ми соответс венно второго и третьего элементов запрета, входы второго и третьего разрядов второго канала первого коммутатора соединены е выходом элемента И, входы второго и третьего разрядов третьегю кангша первого кс 1утатора соединены с выходом элемента И-НЕ, с общей шиной соединены входам всех разрядов первого канала первого коммутатора, входы первого и четвертого разрядов второго канала первого коммутатора, а также входы всех разрядов первого и четвертого каналов второго коммутатора, с шиной питания соединены входы первого и четвертого разрядов

5 третьего канала первого кокии|утатора, входы всех разрядов второго и третьего каналов второго коммутатора соединены с выходами блока мажоритарных элементов, выход элемента ИЛИ соел динен с тактовыми вxoдa aI регистров,, первые входы элемента ИЛИ, первого, второго и третьего элементов запрета соединены с входом сброса счетчика, а вторые входы элемента ИЛИ, первого, второго и третьего элементов запрета соединены соответственно с шинами записи и первой, второй и третьей управляющими шинЕши, четвертая управляющая шина соединена с первыми входами элементов И и И-НВ, остгшьные входы которых соединены с выходгими блока мажоритарных элементов, а пятая, шестая и седьмая управляющие шины соединены соответственно с первыми , вторыми и третьими управляющими входами регистров.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 429536, кл. Н 03 К 23/00, 1972.

Авторы

Даты

1981-01-30—Публикация

1978-07-07—Подача