Изобретение относится к области цифровой вычислительной техники, а именно к проектированию цифровых вычислительных машин на основе больших интегральных схем (БИС) микропроцессоров.

Известны микропроцессорные наборные БИС, отличительной чертой которых является наличие микропрограммного устройства управления, предназначенные для конструирования цифровых вычислительных машин.

Недостатками аналогов являются: невозможность образования начального адреса подготовительной программы, подготавливающей микро-ЭВМ к работе невозможность отслеживания сбоев по питанию и принятию необходимых мер при их появлении.

Наиболее близким по технической сущности к изобретению является микропроцессор для управления памятью шкpoкoмaнд,.содержащий регистр микрокоманд (РМК), -схему образования адреса (СОА), регистр адреса микрокоманд (РАМК), ишну адреса (ША), miny входа (Ш), шину микрокоманд (ШМК) и шину синхронизации (ШС).

Недостатком микропроцессора является невозможность выработки начального адреса подготовительной программы, потому, что при включении питания регистр адреса микрокоманд может установиться в любое состояние и на шине адреса появится произвольньй адрес, кроме того микропроцессор для управления памятью микропрограмм не способен формировать признаки, отмечающие моменты кратковременного исчезновения питания.

При использовании прототипа в составе микро-ЭВМ для реализации указанных функций требуется использование дополнительного оборудования, что увеличивает аппаратурные затраты и., снижает ее надежность.

Цель изобретения - расширение функциональных возможностей микропроцессора за счет выработки начального адреса при включе1ши питания, и вьфаботки адреса микропрограммы . при кратковременном сбое питания.

Цель достигается тем, что в микропроцессор для управления памятью №1крокоманд, содержащий регистр микрокоманд, информационный вход и выход которого соединены соответственно с входом микрокоманд микропроцессора и первым входом блока формирования адреса, второй вход которого является синхровходом микропроцессора и соединен с тактовыми входами регистра микрокоманд и регистра адреса микрокоманд, адресньй вход которого соединен с выходом блока формирования адреса, третий вход которого является информационным входом микропроцессора, выход регистра адреса микрокоманд является выходом адреса микрокоманд микропроцессора и соединен с четвертым входом блока фop шpoвaния адреса, введен блок контроля питания, причем первьй вход блока контроля питания соединен с синхровходом микропроцессора, второй вход блока контроля питания соединен с выходом регистра адреса микрокоманд, третий и четвертьй входы блока контроля питания являются соответственно первым и вторым входом питания микропроцессора, первьй и второй выходы блока контроля питания соединены соответственно с первым и вторым контрольными входами регистра адреса микрокоманд .

I

Кроме того, блок контроля питания

содержит два R5-триггера, Г-триггер дешифраторы нуля и единицы, элементы И, ИЛИ, НЕ, причем единичные входы первого и второго Р5 -триггеров соединены соответственно с третьим и четвертым входами блока, а нулевые входы - с выходом элемента И, первьш вход которого соединен с синхровходом -триггера и через первьй элемент НЕ с первым входом блока, второ вход элемента И соединен с выходом И-триггера, информационньй вход которого соединен с выходом элемента ИЛИ и с третьим входом элемента И, первьй и второй входы элемента ИЛИ соединены соответственно с выходами дешифратора нуля и дешифратора едини цы, входы которых соединены со вторым входом блока, выход первого RS-триггера через второй элемент НЕ соединен с первым выходом блока, выход второго RS-триггера через третий элемент НЕ соединен со вторым выходом блока.

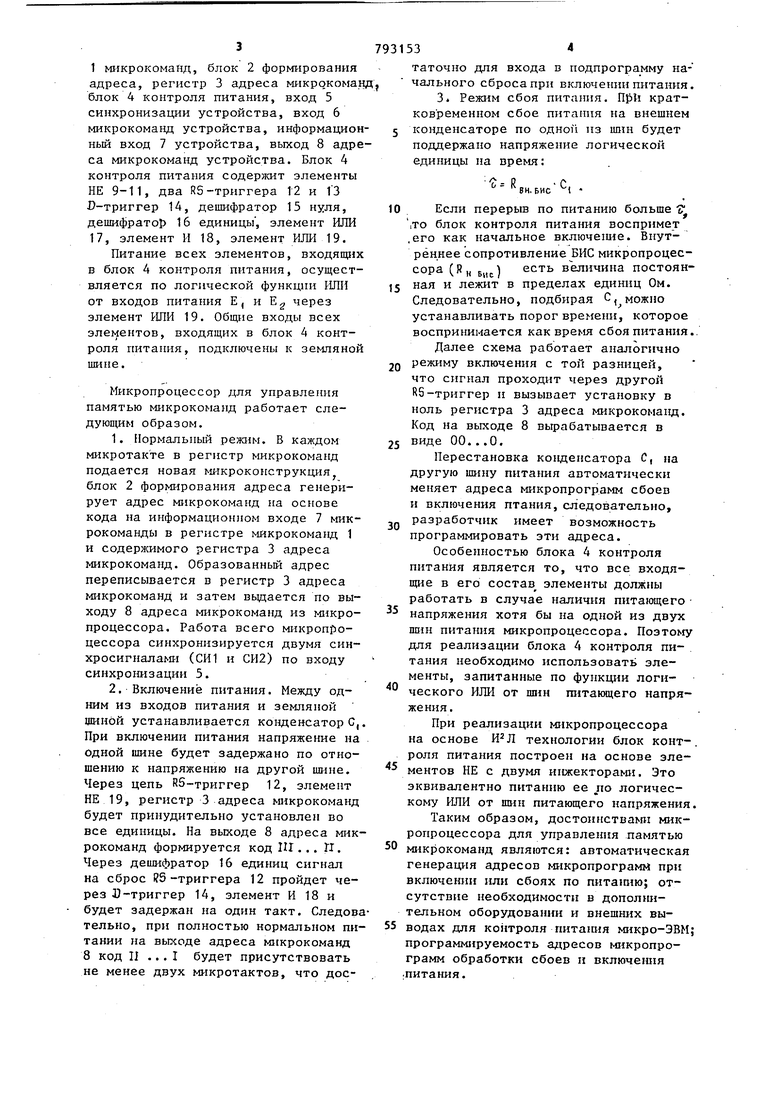

; На чертеже приведена блок-схема микропроцессора.

Микропроцессор для управления памятью микрокоманд содержит регистр 3 1 микрокоманд, блок 2 формирования адреса, регистр 3 адреса микрокома блок 4 контроля питания, вход 5 синхронизации устройства, вход 6 микрокоманд устройства, информацион ный вход 7 устройства, выход 8 адре са микрокоманд устройства. Блок 4 контроля питания содерлсит элементы НЕ 9-11, два R5-триггера 12 и 13 D-триггер 14, дешифратор 15 нуля, дешифратор 16 единицы , элемент ИЛИ 17, элемент И 18, элемент ИЛИ 19. Питание всех элементов, входящих в блок 4 контроля питания, осуществляется по логической функции ИЛИ от входов питания Е, и Е через элемент ОТИ 19. Общие входы всех элементов, входящих в блок 4 контроля питания, подключены к земляно шине. Микропроцессор для управления памятью микрокоманд работает следующим образом. 1.Нормальный режим. В каждом микротакте в регистр микрокоманд подается новая микроконструкция, блок 2 формирования адреса генерирует адрес микрокоманд на основе кода на информационном входе 7 микрокоманды в регистре микрокоманд 1 и содержимого регистра 3 адреса микрокоманд. Образованный адрес переписывается в регистр 3 адреса микрокоманд и затем вьздается по выходу 8 адреса микрокоманд из микропроцессора. Работа всего микропроцессора синхронизируется двумя синхросигналами (СИ1 и СИ2) по входу синхронизации 5. 2.Включение питания. Между одним из входов питания и земляной щиной устанавливается конденсаторе При включении питания напряжение на одной шине будет задержано по отношению к напряжению на другой mine. Через цепь Я5-триггер 12, элемент НЕ 19, регистр 3 адреса микрокоманд будет принудительно установлен во все единицы. На выходе 8 адреса мик рокоманд формируется код П1. . . Г1. Через дешифратор 16 единиц сигнал на сброс R5-триггера 12 пройдет через 3)-триггер 14, элемент И 18 и будет задержан на один такт. Следов тельно, при полностью нормальном пи тании на выходе адреса микрокоманд 8 код II ... I будет присутствовать не менее двух микротактов, что дос34таточно для входа в подпрограмму начального сброса при включении питания. 3. Режим сбоя питания. При кратковременном сбое питания на внешнем конденсаторе по одно11 из шин будет поддержано напряжение логической единицы на время; л . р .л - ВН.БИС -1 Если перерыв по питанию больше V то блок контроля питания воспримет ,его как начальное включе1ше. Внутреннее сопротивление БИС микропроцессора (R,, g,) есть величина постоянная и лежит в пределах единиц Ом. Следовательно, подбирая С,можно устанавливать порог времени, которое воспринимается как время сбоя питания.. Далее схема работает аналогично режиму включения с той разницей, что сигнал проходит через другой R6-триггер и вызывает установку в ноль регистра 3 адреса микрокомавд. Код на выходе 8 вырабатывается в виде 00...0. Перестановка конденсатора С, на другую шину питания автоматически меняет адреса микропрограмм сбоев и включения птания, следовательно, разработчик имеет возможность программировать эти адреса. Особенностью блока 4 контроля питания является то, что все входящие в его состав элементы должны работать в случае наличия питающего напряжения хотя бы на одной из двух шин питания микропроцессора. Поэтому для реализации блока 4 контроля питания необходимо использовать элементы, запитанные по функции логического ИЛИ от miH питающего напряжения. При реализации микропроцессора на основе технологии блок конт-. роля питания построен на основе элементов НЕ с двумя инжекторами. Это эквивалентно питанию ее jio логическому ИЛИ от шин питающего напряжения. Таким образом, достоинствами микропроцессора для управления памятью М11крокоманд являются: автоматическая генерация адресов микропрограмм при включении или сбоях по питаш1ю; отсутствие необходимости в дополнительном оборудовании и внешних выводах для ко11троля питания микро-ЭВМ; программируемость адресов микропрограмм обработки сбоев и включения питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор для управления памятью микрокоманд | 1979 |

|

SU803700A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1267415A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

1. МИКРОПРОЦЕССОР ДЛЯ УПРАВЛЕНИЯ ПАМЯТЬЮ МИКРОКОМАНД, содержащий регистр микрокоманд, информационньй вход и выход которого соедиены соответственно с входом .микрокоманд микропроцессора и первым входом блока формирования адреса, второй вход которого является синхровходом микропроцессора и соединен с тактовыми входами регистра микрокоманд и регистра адреса микрокоманд, адресный вход которого соединен с выходом блока формирования адреса, третий вход которого является информационным входом микропроцессора, выход регистра адреса микрокоманд является выходом адреса микрокоманд микропроцессора и соединен с четвертым входом блока формирования адреса, отличающийс я тем, что, с целью расширения функциональных возможностей за счет обеспечения автоматической генерации адресов микропрограмм при включении или сбоях по питанию, в него введен блок контроля питания, причем первый вход блока контроля пита1шя соединен с синхровходом микропроцессора, второй вход блока контроля питания соединен с выходом регистра адреса микрокоманд, третий и четвертый входы блока контроля питания являются соответственно первым и вторым входом питания микропроцессора,первьй и второй выходы блока контроля питания соединены соответственно с первым и вторым контрольными входами регистра адреса микрокоманд. 2. Микропроцессор по п.1, отличающийся тем, что блок контi роля питания содержит два RS -триггера, Л -триггер,дешифраторы нуля и (Л единицы, элементы И, ИЛИ, НЕ причем С единичные входы первого и второго КЗ-триггеров соединены соответственно с третьим и четвертым входами блока, а нулевые входы - с выходом элемента И, первый вход которого со соединен с синхровходом D -триггера &0 и через первый элемент НЕ с первым входом блока, второй вход элемента И соединен с выходом D-триггера, ел информационный вход которого соедисо нен с выходом элемента ИЛИ и с третьим входом элемента И, первый и второй входы элемента ИЛИ соединены соответственнр с выходами дешифратора нуля и дешифратора единицы, выходы которых соединены с вторым входом блока выход первого RS-триггера через второй элемент НЕ соединен с первым выходом блока, выход второго К5-триггера через третий элемент НЕ соединен со вторым выходом блока. в П т Е

| Прибор для переработки спирта в газовую смесь для двигателей внутреннего сгорания | 1920 |

|

SU589A1 |

| Справочные данные, М., 1977 | |||

| Микропроцессор для управления памятью микрокоманд, техническое описание, 1979. | |||

Авторы

Даты

1986-01-23—Публикация

1979-07-30—Подача