Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных вычислительных систем с микропрограммным управлением.

Цель изобретения - повышение быстродействия устройства.

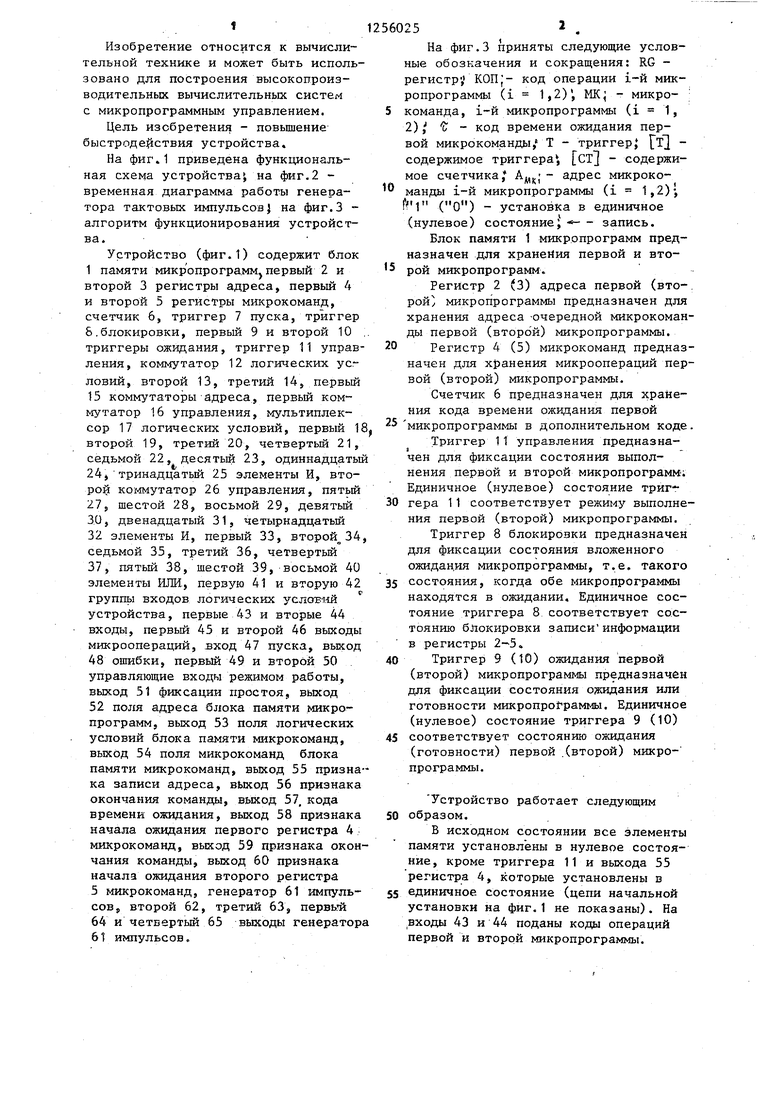

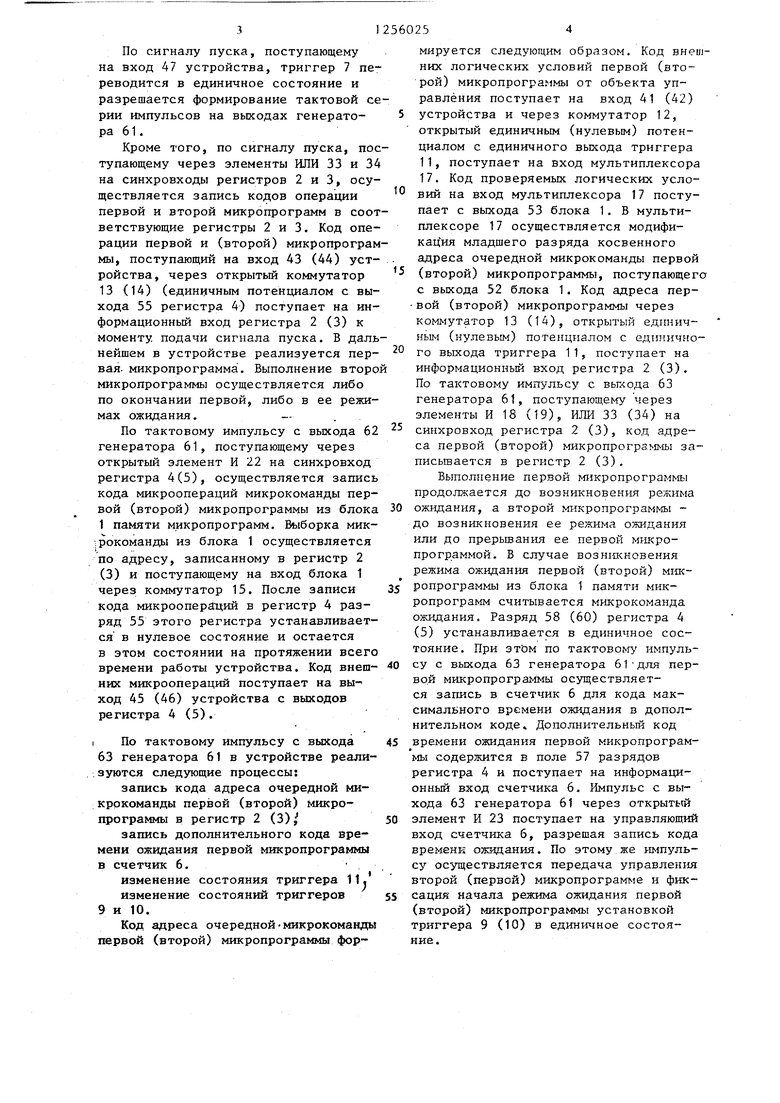

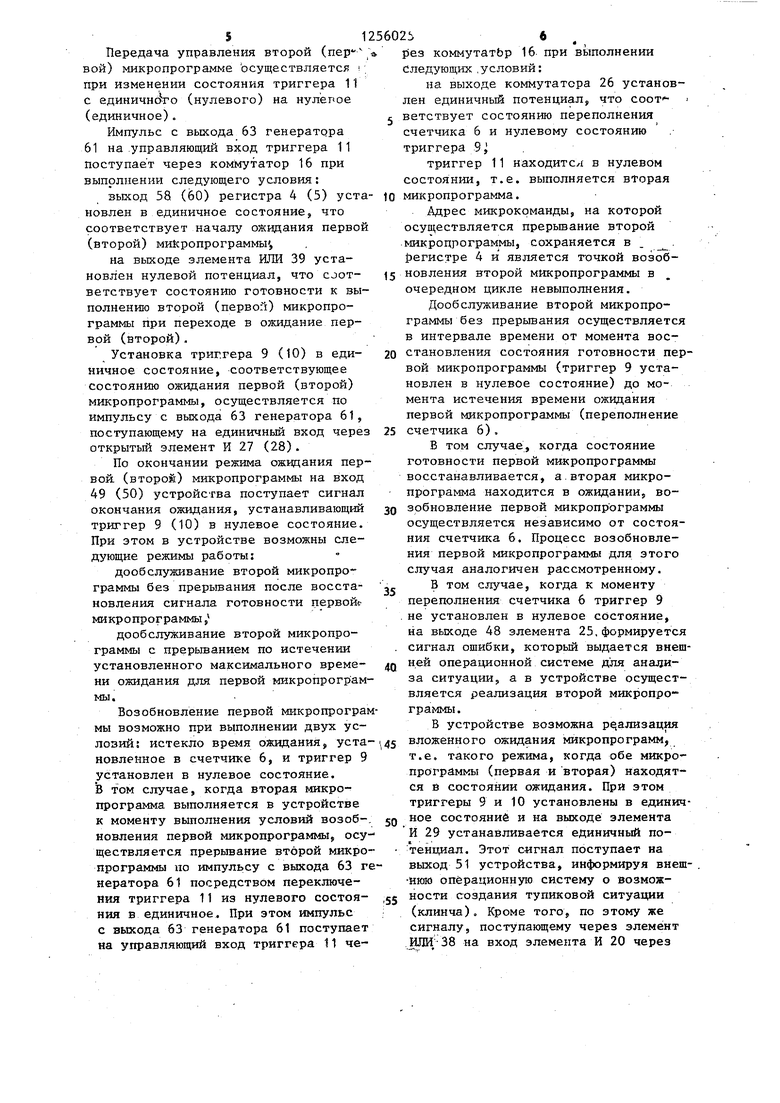

На фиг.1 приведена функциональная схема устройства на фиг.2 - временная диаграмма работы генератора тактовых импульсов} на фиг.З - алгоритм функционирования устройства.

Устройство (фиг.1) содержит блок 1 памяти микропрограмм первый 2 и второй 3 регистры адреса, первый 4 и второй 5 регистры микрокоманд, счетчик 6, триггер 7 пуска, триггер & .блокировки, первый 9 и второй 10 триггеры ожидания, триггер 11 управления, коммутатор 12 логических условий, второй 13, третий 14, первый 15 коммутаторы адреса, первьй коммутатор 16 управления, мультиплексор 17 логических условий, первый 18 второй 19, третий 20, четвертый 21, седьмой 22, десятый 23, одиннадцатый 24, тринадцатьй 25 элементы И, второй коммутатор 26 управления, пятьй 27, шестой 28, восьмой 29, девятый 3.0, двенадцатый 31, четырнадцатый 32 элементы И, первый 33, второй 34 седьмой 35, третий 36, четвертый 37, пятый 38, шестой 39, восьмой 40 элементы ИЛИ, первую 41 и вторую 42 группь входов логических услов-ий устройства, первые.43 и вторые 44 входы, первый 45 и второй 46 выходы микроопераций, вход 47 пуска, выход 48 опшбки, первый 49 и второй 50 управляющие входы режимом работы, выход 51 фиксации простоя, выход 52 поля адреса блока памяти микропрограмм, выход 53 поля логических условий блока памяти микрокоманд, выход 54 поля микрокоманд блока памяти микрокоманд, выход 55 признака записи адреса, вЬгход 56 признака окончания команды, выход 57, кода времени ожидания, выход 58 признака начала ожидания первого регистра 4 микрокоманд, выход 59 признака окончания команды, выход 60 признака начала ожидания второго регистра 5 микрокоманд, генератор 61 импульсов, второй 62, третий 63, первьтй 64 и четвертый 65 выходы генератор 61 импульсов.

На фиг.3 приняты следующие условные обозначения и сокращения: RG - регистр-, КОП|- код операции i-й микропрограммы (i 1,2), МК - микро-

команда, i-й микропрограммы (, 2), о - код времени ожидания первой микрокоманды, Т - триггер - содержимое триггера, ст - содержимое счетчика J А,; - адрес микрокоманды i-й микропрограммы (i 1,2),

ff 1 (о) - установка в единичное

(нулевое) состояние «- запись.

Блок памяти 1 микропрограмм предназначен для хранения первой и второй микропрограмм.

Регистр 2 (3) адреса первой (вто-, рой/ микропрограммы предназначен для хранения адреса -очередной микрокоманды первой (второй) микропрограммы.

Регистр 4 (5) микрокоманд предназначен для хранения микроопераций первой (второй) микропрограммы.

Счетчик 6 предназначен для хранения кода времени ожидания первой

микропрограммы в дополнительном коде.

Триггер 11 управления предназначен для фиксации состояния выполнения первой и второй микропрограмм; Единичное (нулевое) состояние триггера 11 соответствует режиму выполнения первой (второй) микропрограммы.

Триггер 8 блокировки предназначен для фиксации состояния вложенного ожидан.ия микропрограммы, т.е. такого

состояния, когда обе микропрограммы находятся в ожидании. Единичное состояние триггера 8 соответствует состоянию блокировки записи информахщи в регистры

Триггер 9 (10) ожидания первой (второй) микропрограммы предназначен для фиксации состояния ожидания или готовности микропрограммы. Единичное (нулевое) состояние триггера 9 (10)

соответствует состоянию ожидания (готовности) первой .(второй) микропрограммы.

Устройство работает следующим

образом.

В исходном состоянии все элементы памяти установлены в нулевое состояние, кроме триггера 11 и выхода 55 регистра 4, которые установлены в

единичное состояние (цепи начальной установки на фиг.1 не показаны). На входы 43 и 44 поданы коды операций первой и второй микропрограммы.

По сигналу пуска, поступающему на вход 47 устройства, триггер 7 переводится в единичное состояние и разрешается формирование тактовой серии импульсов на выходах генерато- ра 61.

Кроме того, по сигналу пуска, поступающему через элементы ИЛИ 33 и 34 на синхровходы регистров 2 и 3, осуществляется запись кодов операции первой и второй микропрограмм в соответствующие регистры 2 и 3. Код операции первой и (второй) микропрограммы, поступающий на вход 43 (44) уст- ройства, через открытый коммутатор 13 (14) (единичным потенциалом с выхода 55 регистра 4) поступает на информационный вход регистра 2 (3) к моменту, подачи сигнала пуска, В дальнейшем в устройстве реализуется пер- вая- микропрограмма. Выполнение второ микропрограммы осуществляется либо по окончании первой, либо в ее режимах ожидания. -

По тактовому импульсу с выхода 62 генератора 61, поступающему через открытый элемент И 22 на синхровход регистра 4(5), осуществляется запись кода микроопераций микрокоманды первой (второй) микропрограммы из блока 1 памяти микропрограмм. Выборка микрокоманды из блока 1 осуществляется по адресу, записанному в регистр 2 (3) и поступающему на вход блока 1 через коммутатор 15. После записи кода микроопераций в регистр 4 разряд 55 этого регистра устанавливается в нулевое состояние и остается в этом состоянии на протяжении всего времени работы устройства. Код внеш- ник микроопераций поступает на вы- ход 45 (46) устройства с выходов регистра 4 (5).

I По тактовому импульсу с выхода 63 генератора 61 в устройстве реали- .зуются следующие процессы:

запись кода адреса очередной микрокоманды первой (второй) микропрограммы в регистр 2 (3)

запись дополнительного кода времени ожидания первой микропрограммы в счетчик 6.

изменение состояния триггера 11.

изменение состояний триггеров 9 и 10.

Код адреса очередной-микрокоманды первой (второй) микропрограммы фор

мируется следующим образом. Код внешних логических условий первой (второй) микропрограммы от объекта управления поступает на вход 41 (42) устройства и через коммутатор 12, открытый единичным (нулевым) потенциалом с единичного выхода триггера 11, поступает на вход мультиплексора 17. Код проверяемых логических условий на вход мультиплексора 17 поступает с выхода 53 блока 1. В мультиплексоре 17 осуществляется модифи- кац ия младшего разряда косвенного адреса очередной микрокоманды первой (второй) микропрограммы, поступающего с выхода 52 блока 1. Код адреса пер- - вой (второй) микропрограммы через коммутатор 13 (14), открытый единичным (нулевым) потенциалом с единичного выхода триггера 11, поступает на информационный вход регистра 2 (3). По тактовому импульсу с выхода 63 генератора 61, поступающему через элементы И 18 (19), ИЖ 33 (34) на синхроБход регистра 2 (3), код адреса первой (второй) микропрограммы за- письшается в регистр 2 (3).

Выполнение первой мзкропрограммы продолжается до возникновения режима ожидания, а второй микропрограммы - до возникновения ее режима ожидания или до прерьшания ее первой микропрограммой. В случае вознгасновения режима ожидания первой (второй) микропрограммы из блока 1 памяти микропрограмм считывается микрокоманда ожидания. Разряд 58 (60) регистра 4 (5) устанавливается в единичное состояние. При этим по TaKTOBONfy импульсу с выхода 63 генератора 61-для первой микропрограммы осуществляется запись в счетчик 6 для кода максимального времени ожидания в дополнительном коде, Дополн «-ельный код времени ожидания первой микропрограммы содержится в поле 57 разрядов регистра 4 и поступает на информационный вход счетчика 6. Импульс с выхода 63 генератора 61 через открытькй элемент И 23 поступает на управляющий вход счетчика б, разрешая запись кода времени ожидания. По этому.же импульсу осуществляется передача управления второй (первой) микропрограмме и фиксация начала режима ожидания первой (второй) микропрограммы установкой триггера 9 (10) в единичное состояние.

5125602 6

Передача управления второй (. рез коммутатЬр 16 при выполнении

вой) микропрограмме осуществляется при изменении состояния триггера 11 с eдиничн6Vo (нулевого) на нулевое (единичное).

Импульс с выхода 63 генератора 61 на .управляющий вход триггера 11 поступает через коммутатор 16 при выполнении следующего условия:

Следующих,условий:

на выходе коммутатора 26 устан лен единичньй потенциал, что соот ветствует состоянию переполнения счетчика 6 и нулевому состоянию триггера 9 i .

триггер 11 находится в нулевом состоянии, т.е. выполняется втора

выход 58 (60) регистра 4 (5) уста- ю микропрограмма.

новлен в единичное состояние, что соответствует началу ожидания первой (второй) микропрограммы ,

на выходе элемента ИЛИ 39 установлен нулевой потенциал, что соответствует состоянию готовности к выполнению второй (первой) микропрограммы при переходе в олсидание первой (второй),

Установка триггера 9 (10) в единичное состояние, соответствующее состоянию ожидания первой (второй) микропрограммы, осуществляется по импульсу с выхода 63 генератора 61, поступающему на единичный вход через открытый элемент И 27 (28).

По окончании режима ожидания первой (второй) микропрограммы на вход 49 (50) устройства поступает сигнал окончания ожидания, устанавливающий триггер 9 (10) в нулевое состояние. При этом в устройстве возможны следующие режимы работы:

дообслуживание второй микропрограммы без прерьшания после восстановления сигнала готовности первой микропрограммы,

дообслуживание второй микропрограммы с прерыванием по истечении установленного максимального времени ожидания для первой микропрогр ам мы.

Возобновление первой микропрограмы возможно при выполнении двух условий: истекло время ожидания, уста- 45 вложенного ожидания микропрограмм,

новленное в счетчике 6, и триггер 9 установлен в нулевое состояние. Е том случае, когда вторая микропрограмма выполняется в устройстве к моменту выполнения условий возоб-. новления первой микропрограммы, осуществляется прерывание второй микропрограммы 110 импульсу с выхода 63 генератора 61 посредством переключения триггера 11 из нулевого состояния в единичное. При этом импульс с выхода 63 генератора 61 поступает на управляющий вход триггера 11 чет.е. такого режима, когда обе микропрограммы (первая и вторая) находятся в состоянии ожидания. При этом триггеры 9 и 10 установлены в единин

5Q ное состояние и на выходе элемента И 29 устанавливается единичный по- тенциал. Этот сигнал поступает на выход 51 устройства, информируя внеш нюю операционную систему о возмож 55 ности создания тупиковой ситуации (клинча). Кроме того, по этому же сигналу, поступающему через элемент ИЛИ 38 на вход элемента И 20 через

Следующих,условий:

на выходе коммутатора 26 установлен единичньй потенциал, что соот ветствует состоянию переполнения счетчика 6 и нулевому состоянию . триггера 9 i .

триггер 11 находится в нулевом состоянии, т.е. выполняется вторая

Адрес микрокоманды, на которой осуществляется прерьшание второй икропрограммы, сохраняется в . регистре 4 и является точкой возоб- новления второй микропрограммы в очередном цикле невыполнения.

Дообслуживание второй микропрограммы без прерывания осуществляется в интервале времени от момента вос- становления состояния готовности первой микропрограммы (триггер 9 установлен в нулевое состояние) до момента истечения времени ожидания первой микропрограммы (переполнение счетчика 6),

В том случае, когда состояние готовности первой микропрограммы восстанавливается, а.вторая микропрограмма находится в ожидании, во- зрбновление первой микропрограммы осуществляется независимо от состояния счетчика 6. Процесс возобновления первой микропрограммы для этого случая аналогичен рассмотренному. В том случае, когда к моменту переполнения счетчика 6 триггер 9 не установлен в нулевое состояние,

на выходе 48 элемента 25,формируется сигнал ошибки, который вьщается внеш- ней операционной системе для анализа ситуацииJ а в устройстве осуществляется реализация второй микропрограммы.

Б устройстве возможна реализация

т.е. такого режима, когда обе микропрограммы (первая и вторая) находятся в состоянии ожидания. При этом триггеры 9 и 10 установлены в едининное состояние и на выходе элемента И 29 устанавливается единичный по- тенциал. Этот сигнал поступает на выход 51 устройства, информируя внеш-. нюю операционную систему о возможности создания тупиковой ситуации (клинча). Кроме того, по этому же сигналу, поступающему через элемент ИЛИ 38 на вход элемента И 20 через

элемент ИЛИ 36, разрешается установка триггера 8 в единичное состояние по импульсу с выхода 64 генератора 61, при этом блокируется изменение состояний регистров 2-5 и триггеров 9 и 10 импульсами с выходов 62 и 63 генератора 61 ив очередном цикле работы генератора 61.

Возобновление работы устройства может быть выполнено для любой микропрограммы, завершившей ожидание первой. Рассмотрим возобновление выполнения второй микропрограммы в этом случае. На вход 50 устройства поступает сигнал завершения ожидания , триггер 10 устанавливается в нулевое состояние. При этом на выходе элемента И 30 формируется единичный сигнал, который разрешает прохождение импульса с выхода 63 генератора 61 через коммутатор 16 на управляющий вход триггера 11 в том случае, если он находится в единичном состоянии. По этому импульсу триггер 11 устанавливается в нулевое состояние, соответствующее выполнению второй микропрограммы. Кроме того, на выходе элемента И 29 устанавливается нулевой потенциал, что приводит к открьгоанию элемента И 20. и по очередному импульсу с выхода 64 генератора 61 триггер 8 устанавливается в нулевое состояние, при этом временная диаграмма работы устройства сохраняется.

Блокировка элементов И 18, 19, 22 ,27 и 28 снимается и устройство функционирует аналогично рассмотренному выше.

Завершается работа устройства по окончании вьтолнения первой и .второй микропрограмм. По завершении первой (второй) микропрограммы выход 56 (59) регистра 4 (5) устанавливается в единичное состояние. По завершении обеих микропрограмм единичным сигналом с выхода элемента И 2 триггер 7 устанавливается в нулевое состояние, тем самым запре щая формирование тактовой сетки импульсов на выходах генератора 61.

Формула изобретения

Мультимикропрограммное устройство управления, содержащее блок памяти микропрограмм, первый коммутатор управления, первый и второй регистры адреса, триггер пуска, генератор

импульсов, первьм и второй триггеры ожидания, триггер блокировки, триггер управления, первый коммутатор адреса, первый, второй, третий, четвертый, 5 пятый, шестой элементы И, первый, второй, третий, четвертый элементы ИЛИ, причем выход первого коммутатора адреса соединен с адресным входом блока памяти микропрограмм, выходы О первого, второго регистров адреса соединены соответственно с первым и вторым информационными входами первого коммутатора адреса, выходы первого,, и второго элементов ИЛИ соеди- 5 нены соответственно с входами синхронизации первого и второго регистров адреса, выходы первого и второго элементов И соединены с первыми входами соответственно первого и второ- 20 го элементов ИЛИ, выход триггера пуска соединен с входом генератора импульсов, вход установки в 1 триг- / гера пуска, соединен с входом пуска

устройства и с вторыми входами пер- 5 вого и второго элементов И, выход

третьего элемента ЮШ соединен с первым входом третьего элемента И, выход четвертого элемента ИЛИ соединен с инверсным входом четвертого элемен- 0 та И, выход третьего элемента И соединен с входом установки в 1 триг,- гера блокировки, выход четвертого элемента Ti соединен с входом установки в О триггера блокировки, выход 5 триггера блокировки соединен с первым информационным входом первого коммутатора управления, с первыми входами первого и шестого элементов И, с первыми прямыми входами второго и пятого 0 элементов И, выход пятого элемента И соединен с входом установки в 1 первого триггера ожидания, выход шестого элемента И соединен с входом установки в 1 второго триггера 5 ожидания, первый-вход управления режимом работы устройства соединен с входом установки в О первого триггера ожидания, второй вход управления режимом работы устройства соеди- 0 нен с входом установки в О второго триггера ожидания, выход первого коммутатора управления соединен со счетным входом триггера управления, инверсный выход триггера управления 5 соединен с первым управляющим входом первого коммутатора управления, с инверсным входом пятого элемента И с вторым входом шестого элемента

И, прямой выход триггера управления соединен с управляющими входами пер- вего коммутатора адреса, с инверсным входом второго элемента И, с вторым входом первого элемента И, о т л и- чающе е ся тем, что, с целью повышения быстродействия, оно дополнительно содержит перэый и второй регистры микрокоманд, второй и третий коммутаторы адреса, коммутатор и мультиплексор логических условий второй коммутатор управления, счетчик, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый элементы И, пятый, шестой, седьмой и восьмой элементы ИЛИ, причем выход нуля адреса- блока памяти микропрограмм соединен с первыми информационными вхо дами второго и третьего коммутаторов адреса, поле логических условий блока памяти микропрограмм соединено с первой группой информационных выходов мультиплексора логических условий, поле микрокоманд блока памяти микропрограмм соединено с информационными входами первого и второго регистров микрокоманд, прямой выход триггера управления соединен с первым входом десятого элемента И, с инверсным входом одиннадцатого элемента И с входами управления записью первого и второго регистров микрокоманд, с управляющим входом третьего коммутатора адреса, управляющим входом второго коммутатора адреса, управляющими входами коммутатора логических условий, выход признака записи адреса первого регистра микрокоманд соединен с управляющими вхо- дами второго и третьего коммутаторов адреса, поля микроопераций первого и второго регистров микрокоманд являются выходами микроопераций устройства,, выходы признака окончания команды первого и второго регистров микрокоманд соединены соответственно с первыми и вторыми входами четырнадцатого элемента И и восьмого элемента ИЛИ, выходы признака начала ожидания первого и второго регистров микрокоманд соединены соответственно с первыми и вторым входами седьмого элемента ИЛИ, выходы кода времени ожидания первого регистра микрокоманд соединены с информагщонными входами счетчика, первая и вторая группы входов логи

ческих услов 1й устройства соединены соответственно с первой и второй группами информационных входов коммутатора логических условий, группа выходов коммутатора логических условий соединена с второй группой информационных входов мультиплексора логических условий, управляющий вход мультиплексора логических условий соединен с адресным выходом блока памяти микропрограмм, инверсный вход триггера блокировки соединен с первьш входом седьмого элемента И, вторым входом десятого элемента И, с первым прямым входом третьей группы входов первого коммутатора управления, выходы второго и третьего коммутаторов адреса соединены с информационными входами соответственно первого и второго регистров адреса, входы кода операций первой и второй команд соединены с информационными входами соответственно второго и третьего коммутаторов адреса, выход седьмого элемента И соединен с синхровходами первого и второго регистров микрокоманд, выход десятого элемента И соединен с синхровходом счетчика, выход одиннадцатого элемента И соединен со счетным входом счетчика j выход переполнения счетчика соединен с первым входом тринадцатого элемента И и с вторым информационным входом второго коммутатора управления, выход первого триггера ожидания соединен с первыми входами восьмого, девятого элементов И, пятого элемента ИЛИ, с вторым входом тринадцатого элемента И, с управляющим входом второго коммутатора управления, прямой выход второго триггера ожидания соединен с вторым входом восьмого элемента И и пятого элемента ИЛИ, первым информационным входом второго коммутатора управления, инверсный выход второго триггера ожидания соединен с вторым входом девятого элемента И, выход второго коммутатора управления соединен с вторым информационным входом первого коммутатора управления, выход седьмого элемента ИЛИ соединен с третьим входом десятого элемента И, с тре- тьим информационным входом первого коммутатора управленияj с вторым прямым входом пятого элемента И, с третьим входом шестого элемента И, выход тринадцатого элемента И является

1J

выходом ошибки устройства, выход восьмого элемента И соединен с первыми входами третьего и четвертого элементов И и является выходом фиксации простоя устройства, выход пятого элемента ИЛИ соединен с первыми входами шестого элемента ИЛИ и двенадцатого элемента И, выход девятого элемента И соединен с четвертым информационным входом первого коммутатора управления, выход шестого элемента ИЛИ соединен с пятым информационным входом первого коммутатора управления, выход двенадцатого элемента И соединен с вторыми входами третьего и четвертого элементов ИЛИ, выход четырнадцатого элемента И соединен с входом установки в О триггера пуска, выход восьмого элемейта ИЛИ соединен с вторыbbuz: 12

ми входами шестого элемента ИЛИ и двенадцатого элемента И, первый выход генератора импульсов соединен с вторым входом третьего и вторым 5 прямым входом четвертого элементов И, второй выход генератора импульсов соединен с вторым входом седьмого элемента И, третий выход генератора импульсов соединен с четвертым

10 входом десятого элемента И, с третьим прямым входом пятого элемента И, с четвертым входом шестого элемента И, с вторым управляющим входом первого коммутатора управления, с тре 5 тьим входом первого элемента И,

с вторым прямым входом второго элемента И, четвертьй выход генера - тора импульсов соединен с прямым входом одиннадцатого элемен20 та И.

f3

dП П

S4

П П П П

tf

П П

ппппппппппппп

Фиг.г

Мвчаммая аетвювт мементоГуеау р6ел9Л1

Г I

I

1,1 I . . ..;

фи.У

Составитель А. Сошкии Редактор В. Зарванская ТехреД|Л.Сердюкова

Заказ 5148Тираж 671 . Подписное

ВНИИПИ Государственного комитета СССР

ПС делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Г. Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля и управления технологическими процессами | 1984 |

|

SU1193641A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

| МОДУЛЬ МИКРОКОНТРОЛЛЕРНОЙ СЕТИ | 1997 |

|

RU2112272C1 |

| Устройство для программного регулирования | 1988 |

|

SU1571550A1 |

| Устройство для имитации объекта контроля | 1984 |

|

SU1188743A1 |

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Мультимикропрограммное устройство управления | 1981 |

|

SU959079A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-02-20—Подача