1

Изобретение относится к цифровой вычислительной технике и.может быть использовано в вычислительных системах, содержащих несколько активных источников информации, подключенных к общей информационно-адресной магистрали .

Устройство приоритетного подключения процессоров к об14ей магистрали предназначено для анализа сигнаиюв запросов активных устройств fta подключение к общей магистрали и выдачи сигнала разрешения одному из этих устройств, т.е. для устранения конфликтных ситуаций, возникающих при одновременном обращении нескольких устройств к общей магистрали.

Известно интерфейсное устройство с группировкой большого числа запросов, содержащее интерфейсный блок, включающий в себя триггерные cxeN&i и соединенный с блоком определения приоритетов М .

Недостатком устройства является отсутствие средств перераспределения приоритетов (преимущественной обработки) запросов от различных источников.

Наиболее близким по технической сущности к предлагаемому является

устройство управления магистралью, содержащее блок маскирования и блок формирования разрешений. Блок маскирования содержит два последовательно соединенных регистра - входной и выходной. Блок формирования разрешений содержит регистр запросов, две группы элементов И - входную и выходную, два элемента задержки, элемент ИЛИ, элемент И и приоритетный блок, выполняющий стандартную функцию выделения левой едимища 2 .

Однако известное устройство имеет ограниченные функциональные возможности и невысокое быстродействие.

Цель изобретения - повышение быстродействия.

Эта цель достигается тем, что в устройстве приоритетного подключения процессоров к общей магистрали, содержащем блок формированияразрешений и блок маскирования, содержащий выходной регистр, выход которого является выходом блока, первый вход . блока формирования разрешений является входом запросов устройства, второй вход блока формирования разрешений соединен с выходом блока маскирования, выход блока формирования разрешений является выходом устройства.

первый управляющий вход записи информации устройства соединен с первым управляющим входом блока мае;, ирования, в блок маскирования введены регистр управления, счетчик, два блока элементов И-НЕ и блок управления, причем вход данных устройств соединен с входом данных блока управления и с информационным входом регистра управления, управляющий вход которого соединен со вторым управляющим входом записи информации устройства и со вторым управляющим входом блока управления, группа информационных выходов которого соединена с группой информационных входрв счетчика, вход синхронизации которого является входом синхронизации устройства, счетный вход счетчика соединен с выходом логической единицы блока управления, группа информационных входов которого соединена с соответствующими прямыми разрядными выходами счетчика, первые и вторые управляющие входы первого и второго блоков элементов И-НЕ соединены соответственно с первым и вторым выходами .выбора регистра управления, первый и второй выходы выключения которото соединены соответственно с третьими yпpaвJ яющими входами первого и второго блоков элементов И, группы информационных входов которых соединены соответстьенно с первой и второй группами разрядных выходов счетчика, первая группа информационных входов выходного регистра соединена с соответствующими старшими разрядными выходами счетчика, выходы первого и второго блоков элементов И-НЕ соединены с соответствующими информационными входами второй группы выходного регистра,.

. Кроме того, блок управления содержит два регистра и схему сравнения, причем информационные входы первого и второго регистров соединены с входом данных блока, группа разрядных выходов первого регистра соединена с первой группой входов схемы сравнения, вторая группа входов которой соединена с группой информационных входов блока, выход логической единицы которого соединен с выходом схемы сравнения, группа разрядных выходов второго регистра соединена с группой информационных выходов блока, управляющие входы первого и второго регистров соединены со вторым управляющим входом записи информации блока.

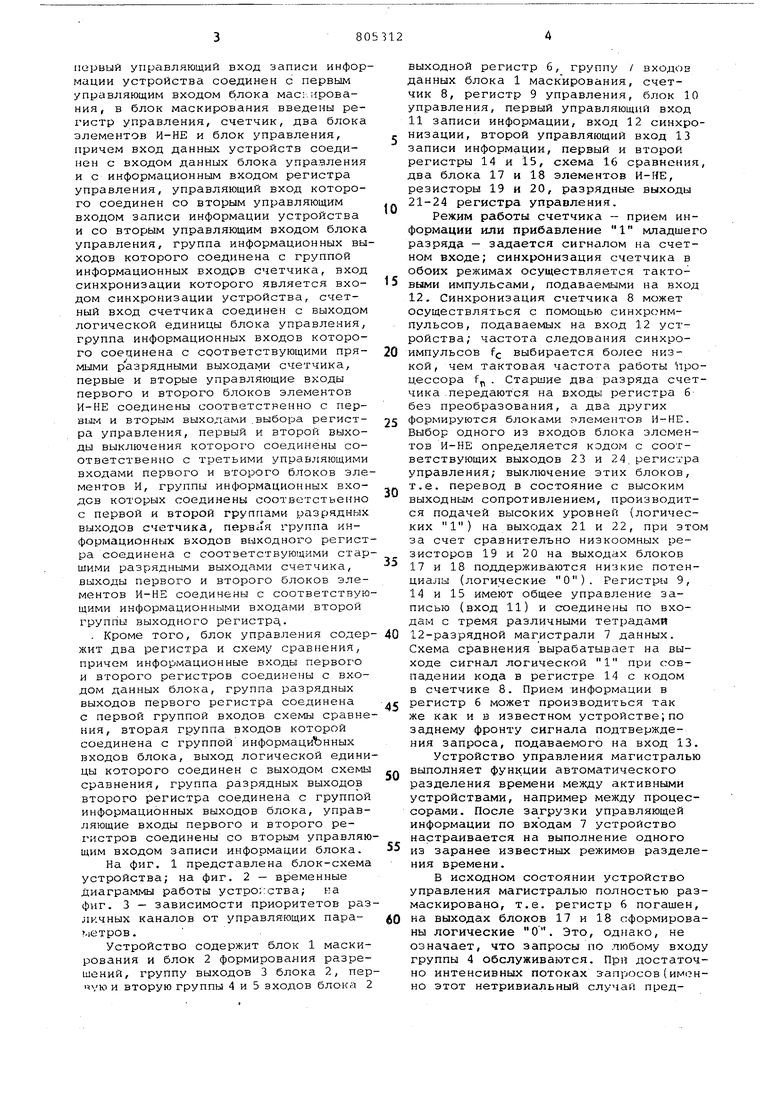

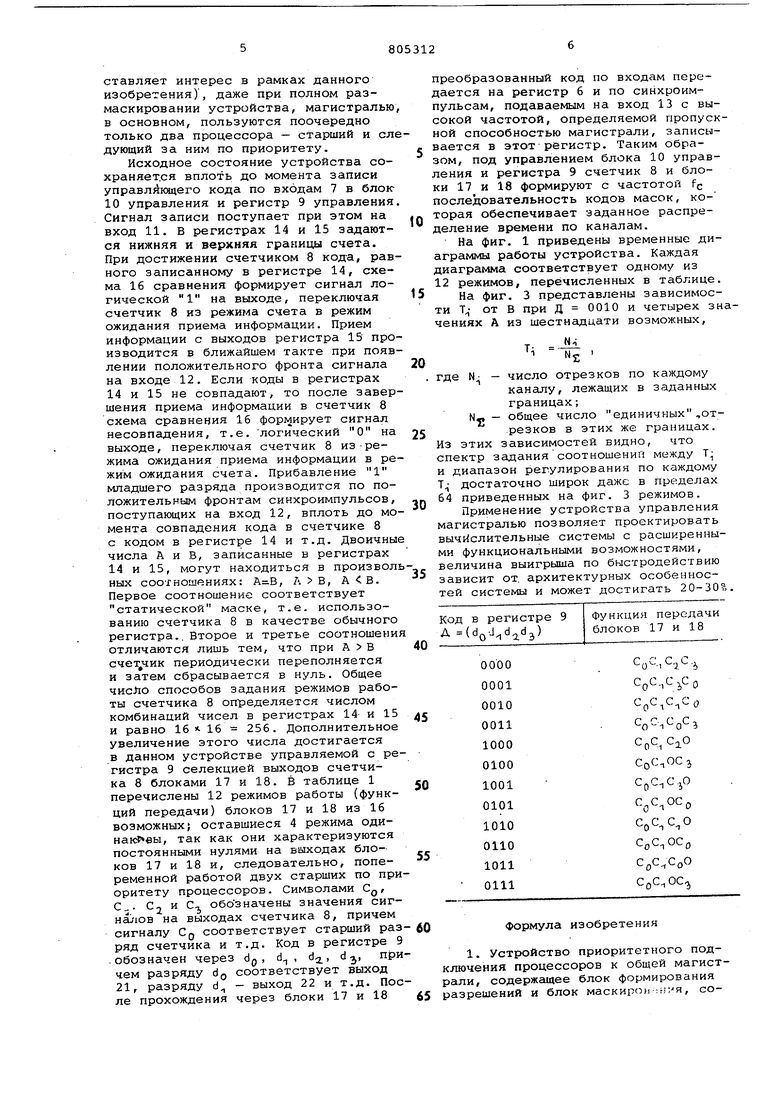

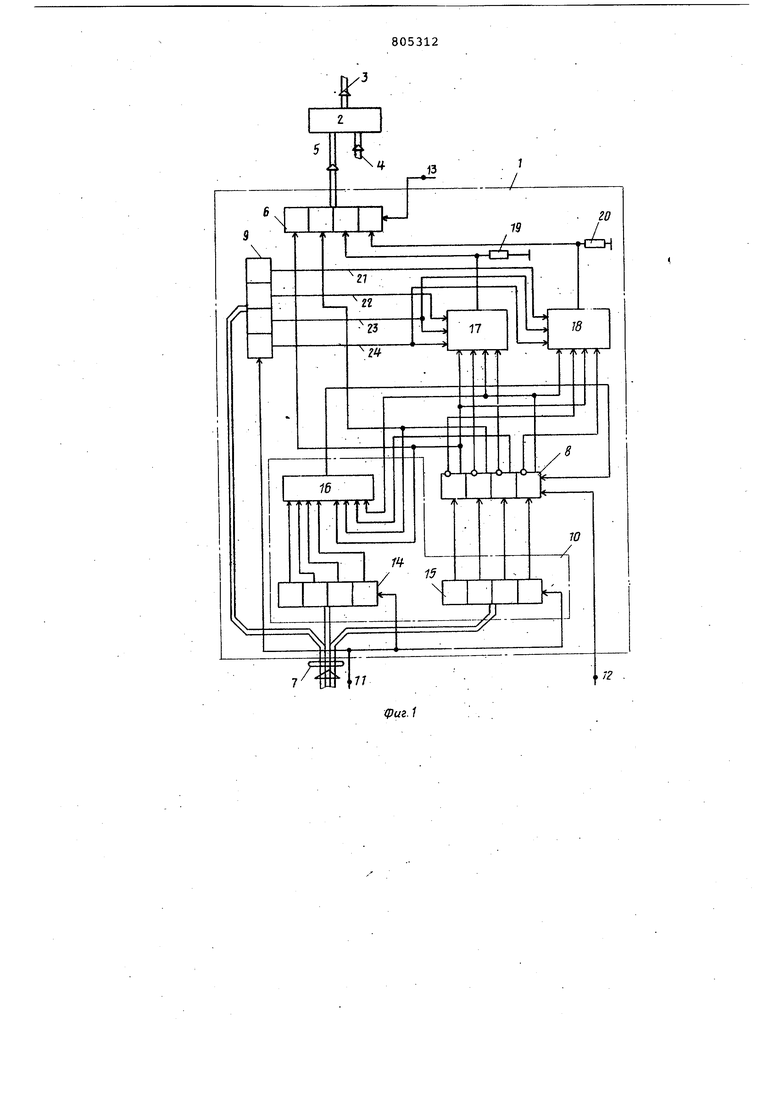

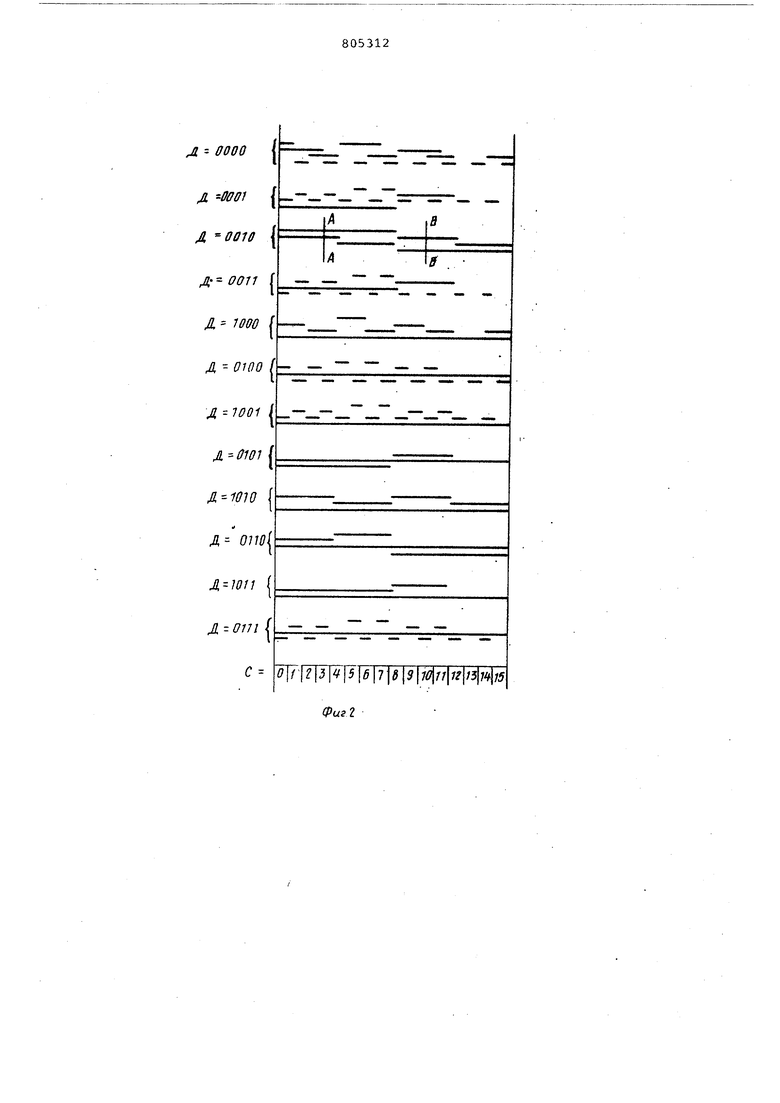

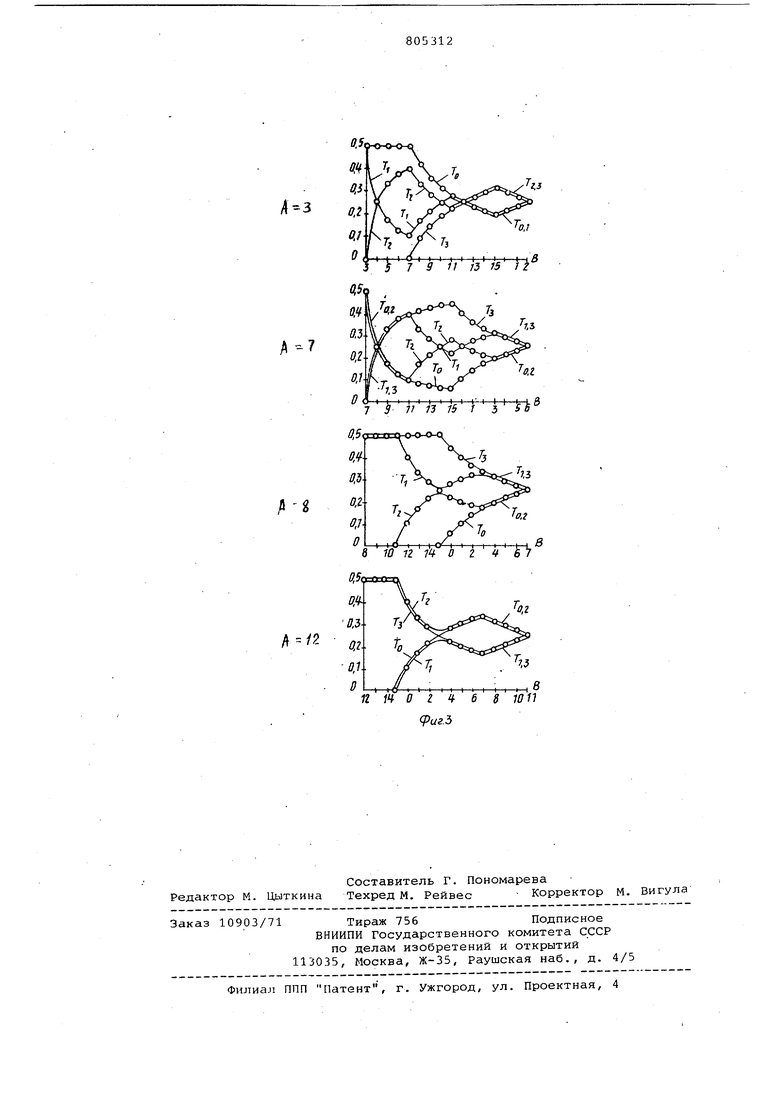

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временные диаграммы работы устро;:ства; на фиг. 3 - зависимости приоритетов различных каналов от управляющих параметров .

Устройство содержит блок 1 маскирования и блок 2 формирования разрешений, группу выходов 3 блока 2, пер1чую и вторую группы 4 и 5 входов блока 2

выходной регистр б, группу / входов данных блока 1 маскирования, счетчик 8, регистр 9 управления, блок 10 управления, первый управляющий вход 11 записи информации, вход 12 синхронизации, второй управляющий вход 13 записи информации, первый и второй регистры 14 и 15, схема 16 сравнения, два блока 17 и 18 элементов И-НЕ, резисторы 19 и 20, разрядные выходы 21-24 регистра управления.

Режим работы счетчика - прием информации или прибавление 1 младшего разряда - задается сигналом на счетном входе; синхронизация счетчика в обоих режимах осуществляется тактовыми импульсами, подаваем лми на вход 12. Синхронизация счетчика 8 может осуществляться с помощью синхроимпульсов, подаваемых на вход 12 устройства; частота следования синхроимпульсов f выбирается более низкой, чем тактовая частота работы процессора f. Старшие два разряда счетчика .передаются на входы регистра б без преобразования, а два других формируются блоками элементов И-НЕ. Выбор одного из входов блока элементов И-НЕ определяется кодом с соответствующих выходов 23 и 24. регистра управления; выключение этих блоков, т.е. перевод в состояние с высоким выходным сопротивлением, производится подачей высоких уровней (логических на выходах 21 и 22, при этом за счет сравнительно низкоомных резисторов 19 и 20 на выходах блоков 17 и 18 поддерживаются низкие потенциалы (логические О). Регистры 9, 14 и 15 имеют общее управление записью (вход 11) и соединены по входа у1 с тремя различными тетрадами 12-разрядной магистрали 7 данных. Схема сравнения вырабатывает на выходе сигнал логической 1 при совпадении кода в регистре 14 с кодом в счетчике 8. Прием информации в регистр б может производиться так же как и в известном устройстве;по заднему фронту сигнала подтверждения запроса, подаваемого на вход 13.

Устройство управления магистралью выполняет функции автоматического разделения времени между активными устройствами, например между процессорами. После загрузки управляющей информации по входам 7 устройство настраивается на выполнение одного из заранее известных режимов разделения времени.

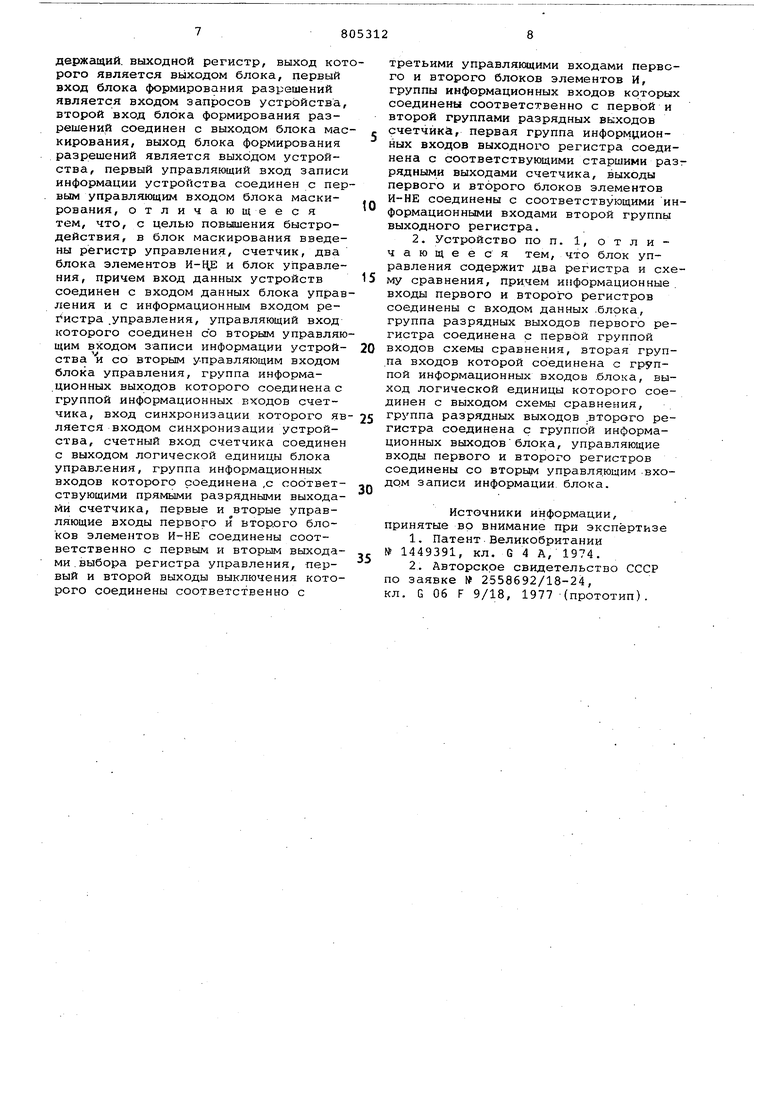

В исходном состоянии устройство управления магистралью полностью размаскировано, т.е. регистр 6 погащен, на выходах блоков 17 и 18 сформированы логические О . Это, однако, не означает, что запросы по любому входу группы 4 обслуживаются. При достаточно интенсивных потоках запросов(именно этот нетривиальный случай представляет интерес в рамках данного изобретения), даже при полном размаскировании устройства, магистралью в основном, пользуются поочередно только два процессора - старший и ел дующий за ним по приоритету. Исходное состояние устройства сохраняется вплоть до момента записи управлякмцего кода по входам 7 в блок 10 управления и регистр 9 управления Сигнал записи поступает при этом на вход 11. В регистрах 14 и 15 задаются нижняя и верхняя границы счета. При достижении счетчиком 8 код-а, рав ного записанному в регистре 14, схема 16 сравнения формирует сигнал логической 1 на выходе, переключая счетчик 8 из режима счета в режим ожидания приема информации. Прием информации с выходов регистра IS про изводится в ближайшем такте при появ лении положительного фронта сигнала на входе 12. Если коды в регистрах 14 и 15 не совпадают, то после завер шения приема информации в счетчик 8 схема сравнения 16 формирует сигнал несовпадения, т.е. логический О на выходе, переключая счетчик 8 из-режима ожидания приема информации в ре жим ожидания счета. Прибавление 1 младшего разряда производится по положительным фронтам синхроимпульсов, поступающих на вход 12, вплоть до мо мента совпадения кода в счетчике 8 с кодом в регистре 14 и т.д. Двоичны числа А и В, записанные в регистрах 14 и 15, могут находиться в произвол ных соотношениях: , Л В, А В. Первое соотношение соответствует статической маске, т.е. использованию счетчика 8 в качестве обычного регистра.. Второе и третье соотношения отличаются лишь тем, что при А В периодически переполняется и затем сбрасывается в нуль. Общее чисЛо способов задания режимов работы счетчика 8 определяется числом комбинаций чисел в регистрах 14- и 15 и равно 16 «. 16 256. Дополнительное увеличение этого числа достигается в данном устройстве управляемой с регистра 9 селекцией выходов счетчика 8 блоками 17 и 18. В таблице 1 перечислены 12 режимов работы (функций передачи) блоков 17 и 18 из 16 возможных; оставшиеся 4 режима одиHaK:t ebi, так как они характеризуются постоянными нулями на выходах блоков 17 и 18 и, следовательно, попеременной работой двух старших по приоритету процессоров. Символами С, С. С и Са обозначены значения сигналов на выходах счетчика 8, причем сигналу CQ соответствует старший разряд счетчика и т.д. Код в регистре 9 .обозначен через d , d , d, d-j, причем разряду dg соответствует выход 21, разряду d - выход 22 и т.д. После прохождения через блоки 17 и 18 преобразованный код по входам передается на регистр 6 и по синхроимпульсам, подаваемым на вход 13 с высокой частотой, определяемой пропускной способностью магистрали, записывается в этот регистр. Таким образом, под управлением блока 10 управления и регистра 9 счетчик 8 и блоки 17 и 18 формируют с частотой f последовательность кодов масок, которая обеспечивает заданное распределение времени по каналам. На фиг. 1 приведены временные диаграммы работы устройства. Каждая диаграмма соответствует одному из 12 режимов, перечисленных в таблице. На фиг. 3 представлены зависимости от В при Д 0010 и четырех значениях А из шестнадцати возможных. где N - число отрезков по каждому каналу, лежащих в заданных границах; N., - общее число единичных ,от-резков в этих же границах. Из этих зависимостей видно, что спектр задания соотношенип между Т и диапазон регулирования по каждому достаточно широк даже в пределах 64 приведенных на фиг. 3 режимов. Применение устройства управления магистралью позволяет проектировать вычислительные системы с расширенными функциональными возможностями, величина выигрыша по быстродействию зависит от. архитектурных особенностей системы и может достигать 20-30%. Формула изобретения 1. Устройство приоритетного подлючения процессоров к общей магистали, содержащее блок формирования азрешений и блок маскир(, содержащий, выходной регистр, выход кот рого является выходом блока, первый вход блока формирования разрешений является входом запросов устройства, второй вход блока формирования разрешений соединен с выходом блока мас кирования, выход блока формирования разрешений является выходом устройства, первый управляющий вход записи информации устройства соединен с пер вым управляющим входом блока маскирования, отличающееся тем, что, с целью повышения быстродействия, в блок маскирования введены регистр управления, счетчик, два блока элементов И-Ц,Е и блок управления, причем вход данных устройств соединен с входом данных блока управ ления и с информационным входом регистра управления, управляющий вход которого соединен со вторым управляю щим входом записи информации устройства и со вторым управляющим входом блока управления, группа информационных выходов которого соединена с группой информационных входов счетчика, вход синхронизации которого яв ляется входом синхронизации устройства, счетный вход счетчика соединен с выходом логической единицы блока управления, группа информационных входов которого соединена ,с собтветствующими прямыми разрядньоми выходаМи счетчика, первые и вторые управляющие входы первого и второго блоков элементов И-НЕ соединены соответственно с первым и вторым выходами.выбора регистра управления, первый и второй выходы выключения которого соединены соответственно с третьими управляющими входами первого и второго блоков элементов И, группы информационных входов которых соединены соответственно с первой и второй группами разрядных выходов счетчика, первая группа информционных входов выходного регистра соединена с соответствующими старшими раз рядными выходами счетчика, выходы первого и второго блоков элементов И-НЕ соединены с соответствующими информационными входами второй группы выходного регистра. 2. Устройство по п. 1, отличающееся тем, что блок управления содержит два регистра и схему сравнения, причем информационные . входы первого и второго регистров соединены с входом данных .блока, группа разрядных выходов первого регистра соединена с первой группой входов схемы сравнения, вторая груп.па входов которой соединена с группой информационных входов .блока, выход логической единицы которого соединен с выходом схемы сравнения, группа разрядных выходов .второго регистра соединена с группой информационных выходовблока, управляющие входы первого и второго регистров соединены со вторьм управляющим -входом записи информации блока. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1449391, кл. 6 4 А, 1974. 2.Авторское свидетельство СССР по заявке 2558692/18-24, кл. G 06 F 9/18, 1977 -(прототип).

Л - 0000 I

Д -0001 { Д 0010 {

А- ООП

л 1000

л - 0100

л -1001 I

ф|Ж 5 б|7| |3|7 Г/|/ |/3|;ф5 (иг

Д-3

/Ig

«

H-rtS

.;/Уз j }V

8 ro r27V°

А /2

п 14 О г б 8 W11

(Риг.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Контроллер с переменным приоритетом | 1980 |

|

SU907550A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU824210A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Многоканальное приоритетное устройство | 1984 |

|

SU1239716A1 |

| Многоканальное приоритетное устройство | 1980 |

|

SU896624A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для обмена информацией | 1978 |

|

SU941978A1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

Авторы

Даты

1981-02-15—Публикация

1978-12-25—Подача