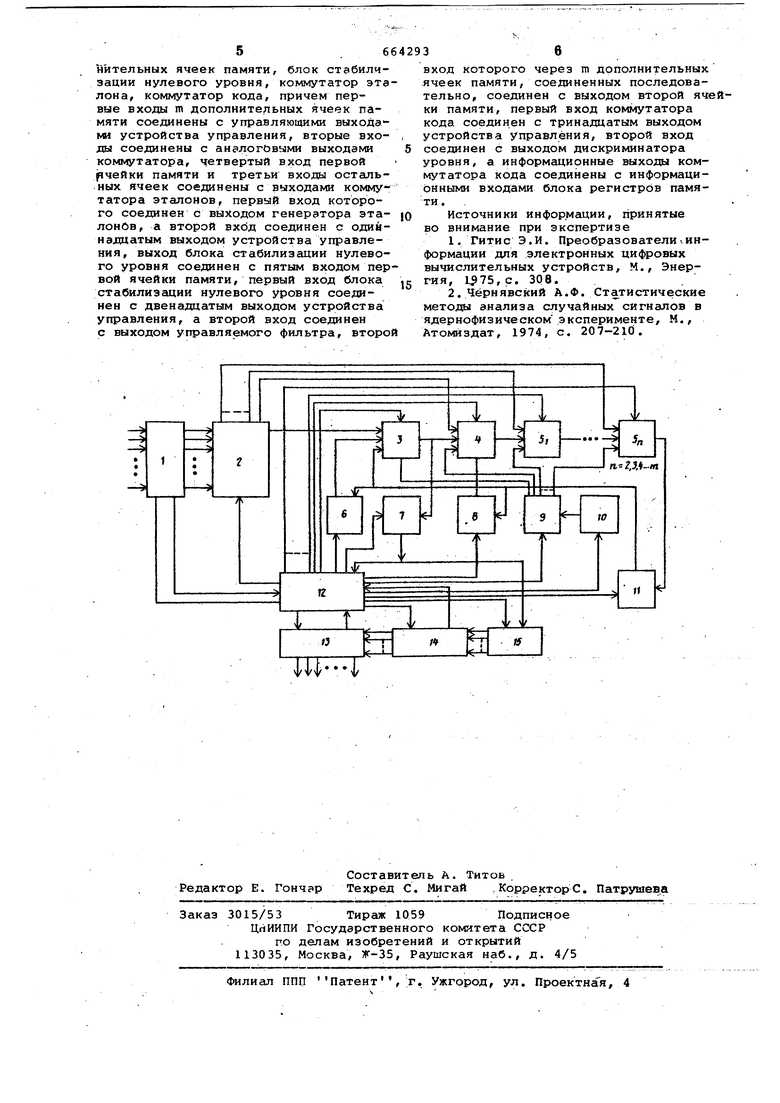

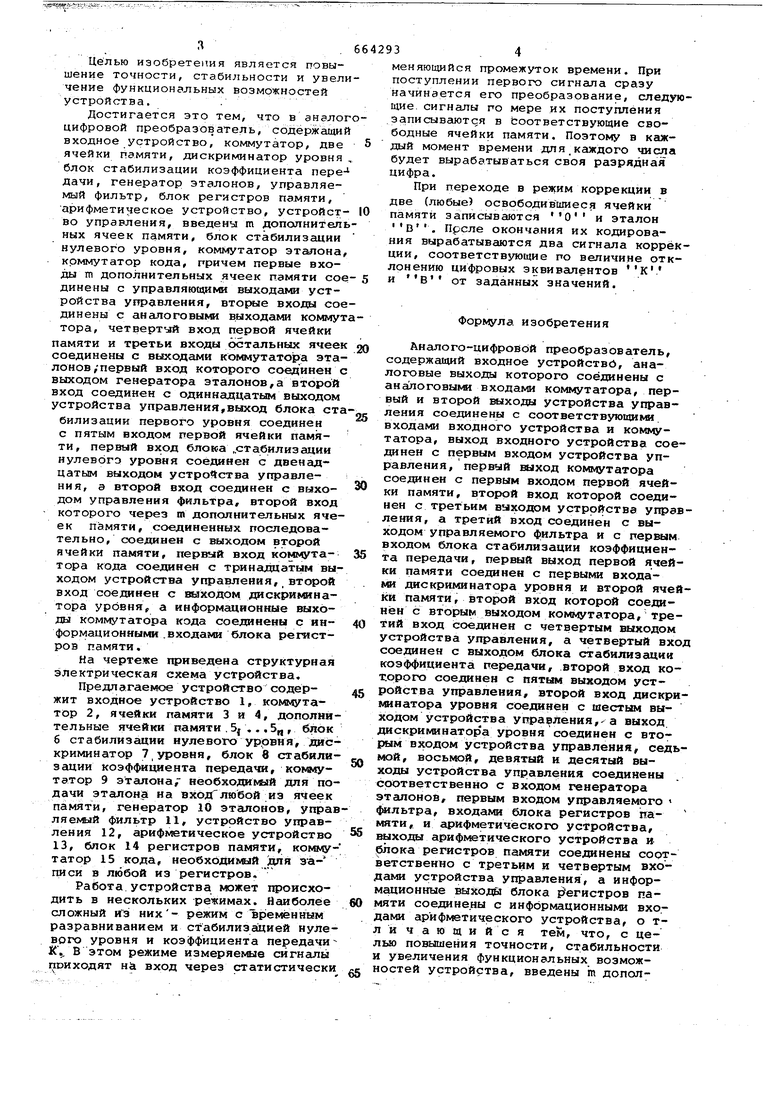

Изобретение относится к радиотехни ке и может быть использовано в амплитудных анализаторах. Известен аналого-цифровой преобразователь, содержащий входное устрой ство, коммутатор, две ячейки памяти, генератор эталонов, дискриминатор уровня, блок стабилизации коэффициента передачи, устройство упрайления, арифметическое устройство и блок регистров памяти i. Однако это устройство имеет недостаточную точность, стабильность и ограниченные функциочальные возможности. Известен аналого-цифровой преобразователь, содержащий входное устройство, аналоговые выходы которого соединены с аналоговыми уходами коммутатора, первый и второй выходы устрой ства управления соединены с соответствующими входами входного устройства и коммутатора, выход входного устройства соединен с первым входом устройства управления, первы выход коммутатора соединен с первым входом пер вой ячейки памяти, второй вход которой соединен с третьим выходом устрой ства управления, а третий вход соедийен с выходом управляемого фильтра и с первым входом блока стабилизации коэффициента передачи, первый выход первой ячейки памяти соединен с первыми входами дискриминатора уровня и второй ячейки памяти, второй вход которой соединен с вторым выходом коммутатора, третий вход соединен с четвертым выходом устройства управления, а четвертый вход соединен с выходом блока стабилизации коэффициента передачи, второй вход которого соединен с пятым выходом устройства управления, второй вход дискриминатора уровня соедине н с шестым выходом устройства управления, а выход дискриминатора уровня соединен с вторым входом устройства управления, седьмой, восьмой, девятый и десятый выходы устройства управления соединены соответственно с входом генератора эталонов, первым входом управляемого фильтра, входами блока регистров памяти и арифметического устройства, выходы арифмети-. ческого устройства и блока регистров памяти сое.цинены соответственно с третьим и четвертым входами устройства управления, а информационные выходы блока регистров памяти соединены с информационными входами арифметического устройства 2. Целью изобретения является повышение точности, стабильности и увели чение функциональных возможностей устройства. Достигается это тем, что в аналог цифровой преобразователь, содержащий входное устройство, коммутатор, две ячейки памяти, дискриминатор уровня блок стабилизации коэффициента передачи, генератор эталонов, управляемый фильтр, блок регистров памяти, арифметическое устройство, устройство управления, введенъл m дополнител ных ячеек памяти, блок стабилизации нулевого уровня, коммутатор эталона коммутатор кода, причем первые входы m дополнительных ячеек памяти сое динены с управляющими выходами устройства управления, вторые входы сое динены с аналоговыьм выходами коммут тора, четвертый вход первой ячейки памяти и третьи входы остальных ячеек соединены с выходами коммутатора эталонов/первый вход которого соединен с выходом генератора эталонов,а второй вход соединен с одиннадцатым выходом устройства управления,выход блока ста билизации первого уровня соединен с пятым входом первой ячейки памяти, первый вход блока „стабилизации нулевого уровня соединен с двенадцатым выходом устройства управлення, а второй вход соединен с выходом управления фильтра, второй вход которого через m дополнительных ячеек памяти, соединенных последовательно, соединен с выходом второй ячейки памяти, первый вход коммутатора кода соединен с тринадцатым выходом устройства управления, второй вход соединен с выходом дагскриминатора уровня, а информационные выходы коммутатора кода соединены с информационными.входами блока регистров памяти. На чертеже приведена структурная электрическая схема устройства, Предлагае « е устройство содержит входное устройство 1, ко№4утатор 2, ячейки памяти 3 и 4, дополнительные ячейки памяти . 5| ,.. 5ц , блок 6 стабилизации нулевого уровня, даскриминатор 7,уровня, блок 8 стабилизации коэффициента передачи, коммутатор 9 эташона, необходимый Для подачи эталона на вход любой из яхеек памяти, генератор 10 эт1алонов, управ ляелый фильтр 11, устройство управЛенин 12, арифметическое устройство 13, блок 14 регистров памяти, коммутатор 15 кода, необходимый ;п1Ля записи в любой из регистров. Работа устройства может происходить в нескольких режимах, Ягдаболее сложный из них- режим с Ъремённым разравниванием и стабилизацией нулевого уровня и коэффициента передачи К . В этом режиме измepяe ыв сигналы ПРИХОДЯТ н& вход через статистически меняющийся промежуток времени. При поступлении первого сигнала сразу начинается его преобразование, следующие, сигналы го мере их поступления записываются в соответствующие свободные ячейки памяти. Поэтому в каждый момент времени для каждого числа будет вырабатываться своя разрядная цифра. При переходе в режим коррекции в две (любые) освободившиеся ячейки памяти записываются О и эталон . Прсле окончания их кодирования вырабатываются два сигнала коррекции, соответствующие по величине отклонению цифровых эквивалентов К и в от заданных значений. Формула изобретения Аналого-цифровой преобразователь, содержащий входное устройстве), аналоговые выходы которого соединены с аналоговы1Л1 входами коммутатора, первый и второй выходы устройства управления соединены с соответствующими входами входного устройства и коммутатора, выход входного устройства соединен с первым входом устройства управления, первый выход коммутатора соединен с первым входом первой ячейки памяти, второй вход которой соединен с третьим выходом устройства управления, а третий вход соединен с выходом управляемого фильтра и с первым входом блока стабилизации коэффициента передачи, первый выход первой ячейки памяти соединен с первыми входами дискриминатора уровня и второй ячейки памяти, второй вход которой соединён с вторым выходом коммутатора, третий вход соединен с четвертым выходом устройства управления, а четвертый вход соединен с выходом блока стабилизации коэффициента передачи, второй вход которого соединен с пятым выходом устройства управления, второй вход дискриAQiBaTopa уровня соединен с шестым выходом устройства управления,а выход, дискриминатора уровня соединен с вторым входом устройства управления, седьмой, восьмой, девятый и десятый выходы устройства управления соединены соответственно с входом генератора эталонов, первым входом управляемого фильтра, входами блока регистров п амяти, и арифметического устройства, выхода арифметического устройства и блока регистров памяти соединены соответственно с третьим и четвертым вхоДс1ми устройства управления, а информационные выхода блока р егистров памяти соединены с информационными входами арифметического устройства, о тл и ч а ю щ и и с я тем, что, с целью повышения точности, стабильности и увеличения функциональных возможностей устройства, введены m дополнительных ячеек памяти, блок стабилизации нулевого уровня, коммутатор эталона, коммутатор кода, причем первые входы m дополнительных ячеек памяти соединены с управляющими выходаьм устройства управления, вторые входы соединены с аналоговыми выходами коммутатора, четвертый вход первой (Ячейки памяти и третьи входы остгшьиых ячеек соединены с выходами коммутатора эталонов, первый вход которого соединен с выходом генератора эталонов, а второй вход соединен с одиннадцатым выходом устройства управления, выход блока стабилизации нулевого уровня соединен с пятым входом первой ячейки памяти, первый вход блока стабилизации нулевого уровня соединен с двенадцатым выходом устройства управления, а второй вход соединен с выходом управляемого фильтра, второ

вход которого через га дополнительных ячеек памяти, соединенных последовательно, соединен с выходом второй ячейки памяти, первый вход коммутатора кода соединен с тринадцатым выходом устройства Управления, второй вход соединен с выходом дискриминатора уровня, а информационные выходы коммутатора кода соединены с информационными входами блока регистров памяти,

Источники информации, принятые во внимание при экспертизе

1.Гитис Э.И. ПреобразователиVинформации для электронных цифровых вычислительных устройств, М., Энергия, 1Э75, с. 308.

2.Чернявский А.Ф. Статистические методы анализа случайных сигналов в ядернофизическом эксперименте, М,, Атомйздат, 1974, с. 207-210.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU805488A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU805487A1 |

| Аналого-цифровой преобразователь | 1977 |

|

SU677098A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU1170606A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Устройство для определения весового расхода и контроля качества сыпучего материала | 1982 |

|

SU1089425A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

Авторы

Даты

1979-05-25—Публикация

1977-01-27—Подача