первого коммутатора подключен к третьему входу блока памяти..

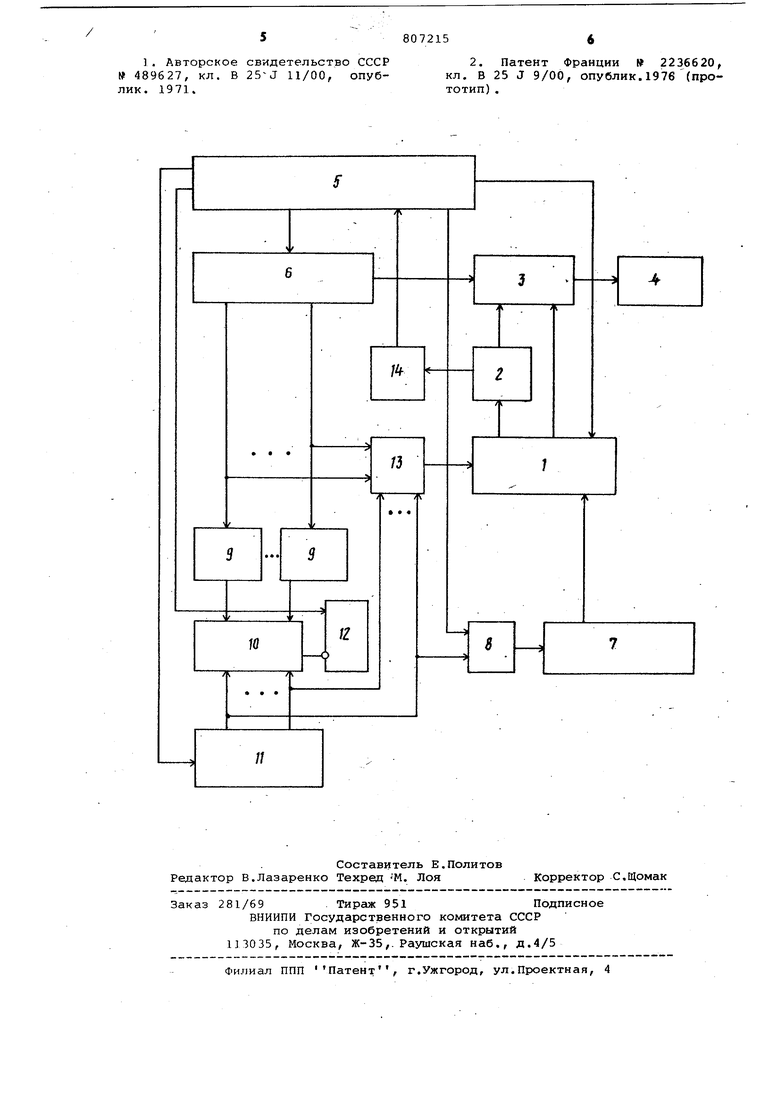

На чертеже представлена функциона.пьная схема устройства.

Устройство содержит блок 1 памяти, первый дешифратор 2, линейный интерполятор 3, исполнительный механизм 4 манипулятора, блок 5 управления, блок 6 обучения, счетчик 7 адреса, элемент ИЛИ 8, вторые дешифраторы 9, блок 10 селекции, распределитель 11 импульсов, элемент 12 запрета, первый коммутатор 13, второй коммутатор 14,

Устройство работает следующим образом.

Для программного управления исполнительным механизмом 4 манипулятора в блок 1 памяти должна быть записана соответствующая программа движения, которая формируется методом пробного паремещения. При этом по командам из блока 5 управления в режиме обучения осуществляется перемещение исполнительного механизма 4 манипулятора в заданную точку пространстра. Информация о величине перемещения между последовательными точками траектории фиксируется в блоке б обучения. Эта информация поступает на информационные входы первого коммутатора 13 и входы вторых дешифраторов 9. По команде из блока 5 управления, поступающей на. вход распределителя 11 импульсов, последний вырабатывает группу импульсов, под воздействием которых информация с выхода блока 6 обучения через первый коммутатор 13 записывается в запоминающий блок 1. При записи не нулевых значений величин перемещений выходной сигнал блока 10 селекции разрешает прохождение импульсов с выхода блока 5 управления через элемент запрета 12, Выходной сигнал элемента 12 запрета через элемент ИЛИ 8 переключает счетчик 7 адреса, подключающий для записи очередную ячейку блока 1 памяти. Момент переключения адреса выбирается синхроимпульсом, поступающим из блока 5 управления на прямой вход элемента 12 запрета. Е.сли же значение величины перемещения по некоторой координате равно нулю, то при ее записи в блок- 1 памяти, благодаря выходному сигналу соответствующего второго дешифратора 9, на выходе блока 10 селекции формируется потенциал, запрещающий прохождение импульса переключения счетчика 7 адреса через элемент 12 запрета. Таким образом, обеспечивается селективная запись информации в блок 1 памяти лишь о координатах манипулятора, величина перемещения по которым отлична от нуля,

В режиме автоматического воспроиз ведения записанной программы, информация из блока 1 памяти считывается в линейной интерполятор 3 по командам блока 5 управления. Для последовательного выбора информации из ячеек блока 1 памяти по сигналам блока управления через элемент ИЛИ 8 осуществляется переключение снетчика 7 адреса. Правильная адресация считываемой информации осуществляется первым дешифратором 2,дешифрирующим признаки координат. Второй коммутатор 14 вьвделяет момент, соответствущий считыванию всей информации, оИисывающей переход от точки к точке. По его сигналу блок 5 управления прекращает считывание информации и осуществляется отработка накопленно информации.

Предлагаемое устройство существено сокращает необходимый объем памяти запоминающего блока, так как общее количество координат манипулятора (обычно 5-7) значительно больше, чем количество координат, изменяющихся при переходе схвата между последовательными точками траектории (обычно 2-3).

Формула изобретения

Устройство для программного управления многокоординатным манипулятором, содержащее последовательно соединенные блок памяти, первый дешифратор, линейный интерполятор и исполнительный механизм манипулятора, блок управления, первый выход которого подключен к первому входу блока памяти,второй выход которого соединен со вторым входом линейного интерполятора, отличающеес я тем, что, с целью упрощения устройства, оно содержит первый и второй коммутаторы, блок обучения, .вторые дешифраторы, распределитель импульсов и последовательно соединенные блок селекции, элемент запрета, элемент ИЛИ и счетчик адреса выход которого подключен ко второму входу блока памяти, второй выход первого дешифратора соединен через второй коммутатор со входом блока управления, второй выход которого подключен ко второму входу элемента ИЛИ, третий выход - ко входу распределителя импульсов, четвертый выход - ко второму входу элемента запрета, а пятый выход - ко входу блока обучения, первый выход которого соединен с третьим входом линейного интерполятора, а вторые выходы - с первыми входами первого коммутатора и входами вторых дешифраторов, выходы которых подключены к первым входам блока селекции, вторые входы которого, а также вторые входы первого коммутатора соединены с выходами распределителя импульсов, а выход первого коммутатора подключен к третьему входу блоka памяти.

Источники инф.ормации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР 489627, кл. В 11/00, опублик. 1971.

2. Патент Франции 2236620, кл. В 25 J 9/00, опублик.1976 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Устройство для программногоупРАВлЕНия МНОгОКООРдиНАТНыММАНипуляТОРОМ | 1977 |

|

SU819794A1 |

| Система телемеханики | 1982 |

|

SU1152015A1 |

| Линейный интерполятор | 1988 |

|

SU1538166A2 |

| Устройство для считывания графической информации | 1981 |

|

SU983731A1 |

| СИСТЕМА ПРОГРАММНОГО УПРАВЛЕНИЯ ГРУППОЙ ЕДИНИЦ ТЕХНОЛОГИЧЕСКОГО ОБОРУДОВАНИЯ | 1991 |

|

RU2020537C1 |

| Устройство для распознавания элементов треков | 1983 |

|

SU1161969A1 |

| Система контурного программного управления манипулятором | 1977 |

|

SU620368A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для формирования управляющих программ | 1985 |

|

SU1257616A1 |

Авторы

Даты

1981-02-23—Публикация

1978-07-10—Подача