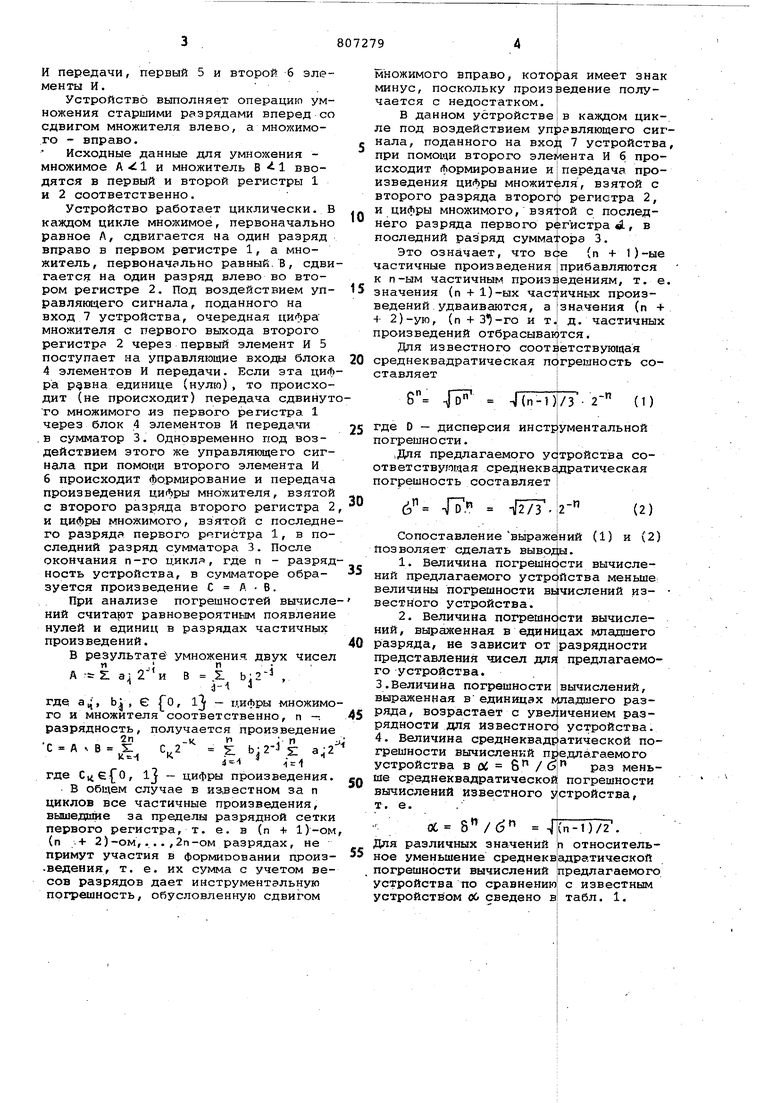

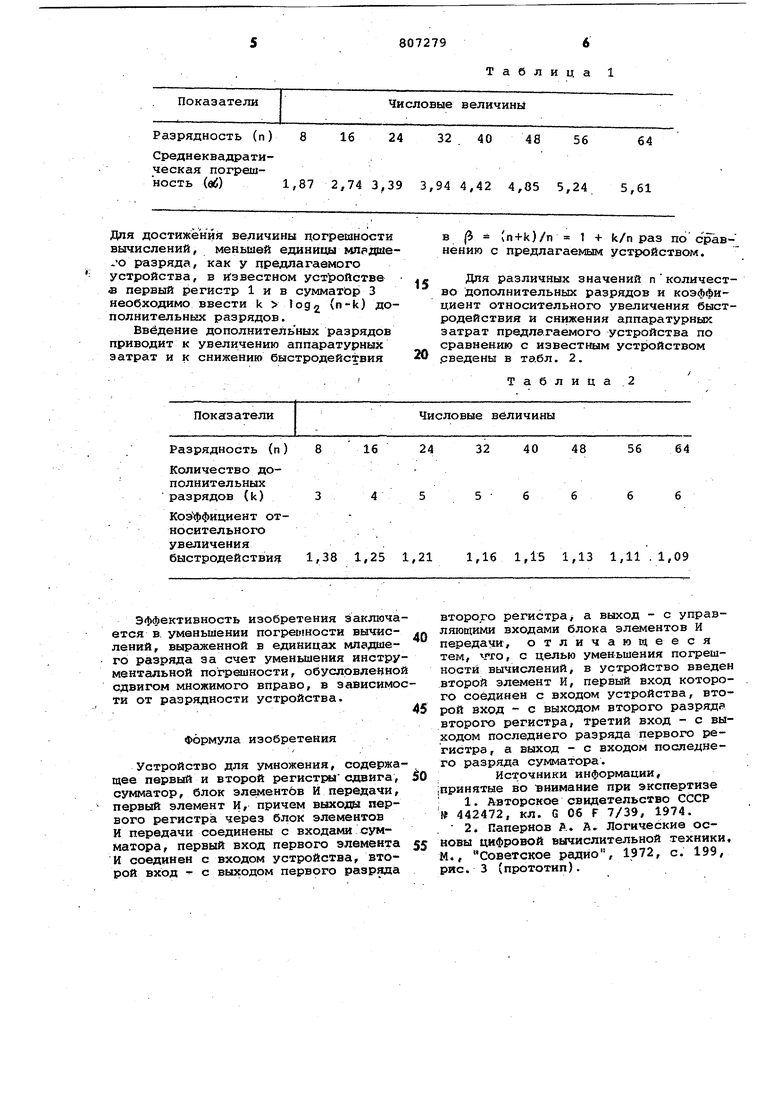

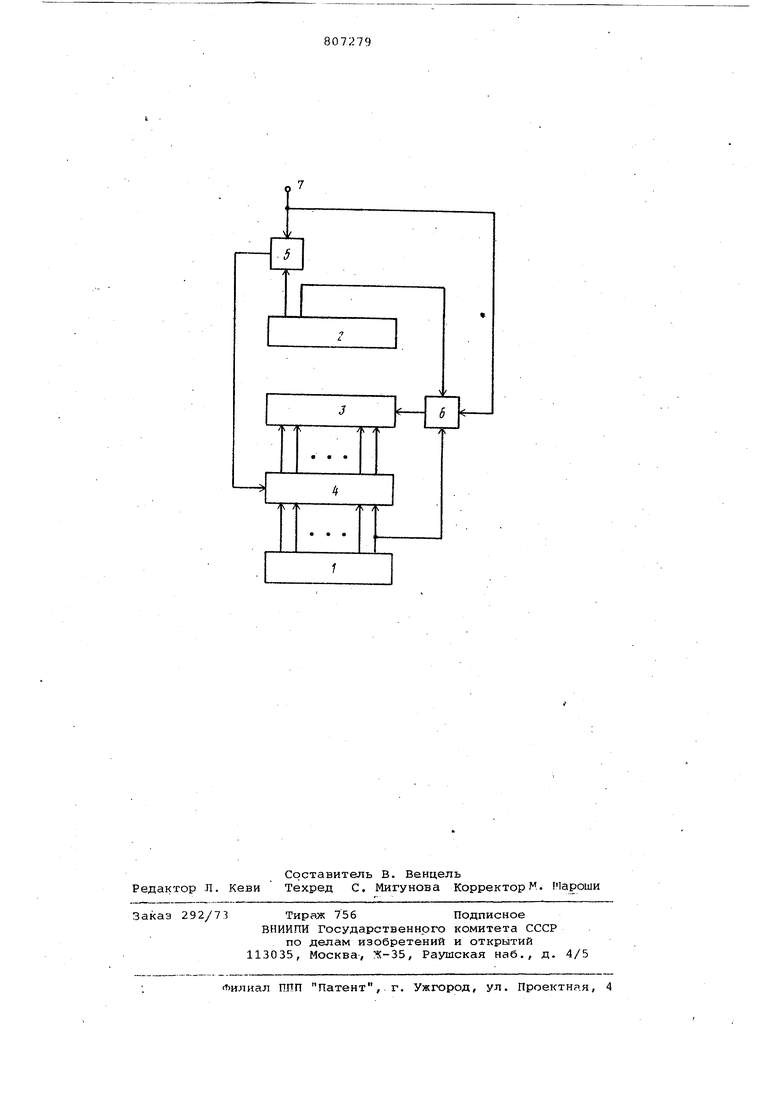

Изобретение относится к цифровой вычислительной технике и может применяться в цифровых вйчислительных машинах. Известны устройства для умножения содержащие регистры сдвига, блок передачи, элементы И 1 . Однако уменьшение погрешности вычислений в данных устройствах обеспе чивается путем введения дополнительных разрядов в регистры и сумматоры или путем введения датчиков случайных чисел, что приводит к уменьшению быстродействия и к увеличению аппара турных затрат. Наиболее близким по технической сущности к предлагаемому является ус ройство умножения, содержащее первый и второй регистры сдвига, сумматор, вентили передачи,. первый элемент И(53 Данное устройство обладает простой конструкцией, однако у него низка точность вычислений, поскольку инструментальная погрешность вычислений , обусловленная сдвигом множимого вправо, пропорциональна разрядности. Для достижения величины погрешности вычислений меньшей единицы младьчего разряда, устройство содержит дополнительные разряды первого регистра и сумматора, что приводит к увеличению аппаратурных затрат и к уменьшению быстродействия. Цель изобретения - уменьшение погрешности вычислений. Поставленная цель достигается тем, что в устройство для умножения, содержащее первый и второй регистры сдвига, сумматор, блок элементов И передачи, первый элемент И, причем выходы первого регистра через блок злементов И передачи соединены с входами сумматора, первый вход первого элемента И соединен с входом устройства, второй вход - с выходом первого разряда второго регистра, а выход - с управляюв1ими входами блока элементов Ипередачи, введен второй элемент И, первый вход которого соединен с входом устройства, второй вход - с выходом второго разряда второго регистра/ третий вход - с выходом последнего разряда первого регистра, а выход с входом последнего разряда сумматора. На чертеже изображена блок-схема предлагаемого устройства. Устройство содержит первый и второй регистры 1 и 2 сдвига соответственно, сумматор 3, блок 4 элементов И передачи, первый 5 и второй б элементы И. . Устройство вьшолняет операцию умножения старшими разрядами вперед со сдвигом множителя влево, а множимого - вправо. Исходные данные для умножения множимое А 1 и множитель В 1 вводятся в первый и второй регистры 1 и 2 соответственно. Устройство работает циклически. В каждом цикле множимое, первоначально равное Л, сдвигается на один разряд вправо в первом регистре 1, а множитель, первоначально разный. В, сдви гается на один разряд влево во втором регистре 2. Под воздействием управляющего сигнала, поданного на вход 7 устройства, очередная цифра множителя с первого выхода второго регистра 2 через первый элемент И 5 поступает на управляющие входы блока 4 элементов И передачи. Если эта циф ра р§вна единице (нулю), то происхо дит (не происходит) передача сдвинут то множимого из первого регистра 1 через блок 4 элементов И передачи .в сумматор 3. Одновременно под воздействием этого же управляющего сиг нала при помощи второго элемента И 6 происходит формирование и передач произведения ци()ры множителя, взято с второго разряда второго регистра и цифры множимого, взятой с последн го разряда первого регистра 1, в по следний разряд сумматора 3. После окончания п-го цикля, где п - разря ность устройства, в сумматоре образуется произведение С А В. При анализе погрешностей вычисл ний считарт равновероятным появлени нулей и единиц в разрядах частичных произведений. В результате умножения двух чисе п ,; п А rt 2: а: 2 i i . И D 51 JM где , Ь; , е Го, 1 цифры множим го и множителя соответственно, п -. разрядность, получается произведени 4 Z b: 2- s: где , 1 - цифры произведения В общем случае в известном за п циклов все частичные произведения, вышедйше за пределы разрядной сетк первого регистра, т. е. в (п + 1)-о (п .+ 2)-ом,...,2п-ом разрядах, не примут участия в формировании произ .ведения, т. е. их сумма с учетом ве сов разрядов дает инструментальную погрешность, обусловленную сдвигом множимого вправо, котоЬая имеет знак минус, поскольку произведение получается с недостатком. В данном устройстве IB каждом цикле под воздействием уп 5авляющего сигнала, поданного на вкоЬ 7 устройства, при помощи второго элемента И б происходит формирование и I передача произведения цифры множителя, взятой с второго разряда второго регистра 2, и цифры множимого, взятой с последнего разряда первого р(гистра «1, в последний разряд сумма:ора 3. Это означает, что все (п + 1)-ые частичные произведения I прибавляются к п-ым частичным произведениям, т. е. значения (п + 1)-ых част ичных произведений удваиваются, а значения (п + + 2)-ую, (п + и т.| д. частичных произведений отбрасываются. Для известного соответствующая среднеквадратическая погрешность составляет6 i -(п-1)/з- 2- где D - дисперсия инструментальной погрешности. ,Для предлагаемого устройства соответствующая среднеквсдратическая погрешность составляет 6 47. nflTTСопоставление выражений (1) и (2) Позволяет сделать выводы. 1.Величина погрешности вычислений предлагаемого устрсэйства меньше: величины погрешности вычислений известного устройства. 2.Величина погрешности вычислений, выраженная в единицах мпадшего разряда, не зависит от разрядности представления чисел для предлагаемого устройства. 3.Величина погрешности вычислений, выраженная вединицах штадшего разряда, возрастает с yвe :ичeниeм разрядности для известногс устройства. 4. Величина среднеквадратической погрешности вычислений предлагаемого устройства 3 ОС /( раз меньше среднеквадратической погрешности вычислений известного устройства, т. е. . ос 4 (п-1)/2 . Для различных значений п относитель. ное уменьшение среднеквадратической погрешности вычислений предлагаемого устройства по сравнению с известным устройством об сведено в табл. 1.

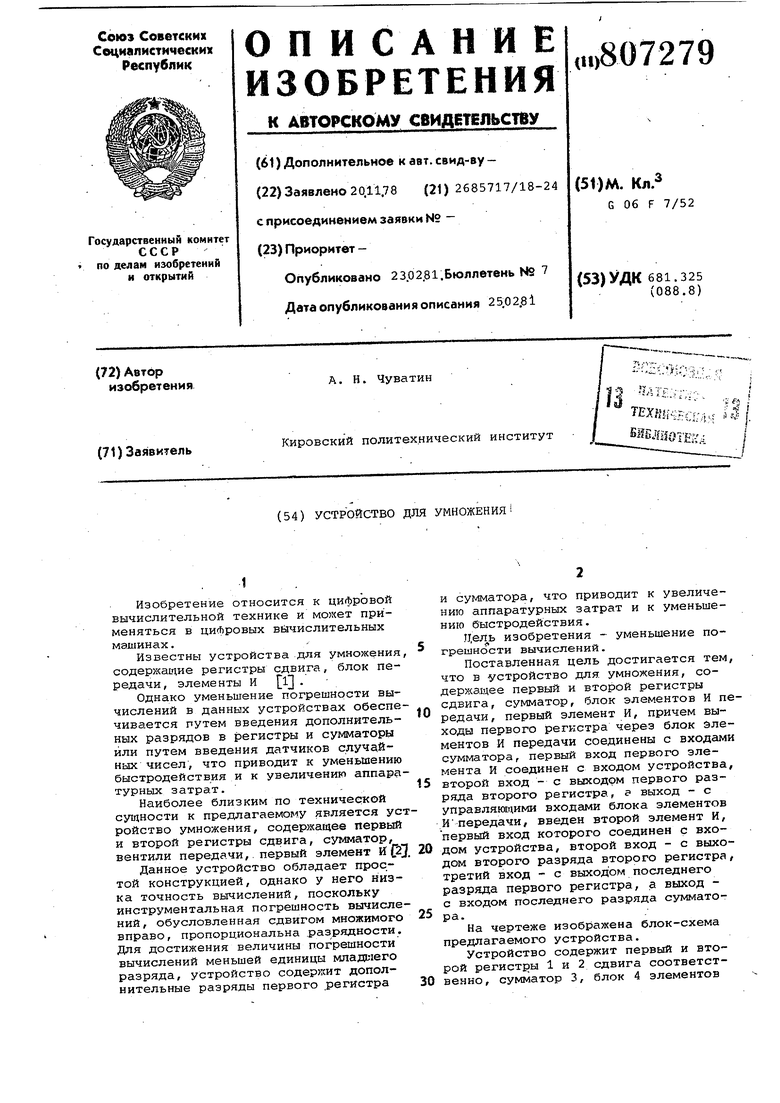

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения | 1983 |

|

SU1111154A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ УМНОЖИТЕЛЬ С ФИКСИРОВАННОЙ ТОЧКОЙ | 1998 |

|

RU2131617C1 |

| Устройство для умножения | 1988 |

|

SU1569824A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

Разрядность (п) 8 16 24 32 . 40 48 56

Среднеквадратическая погрешность Ы) 1,87 2,74 3,39 3,94 4,42 4,85 5,24

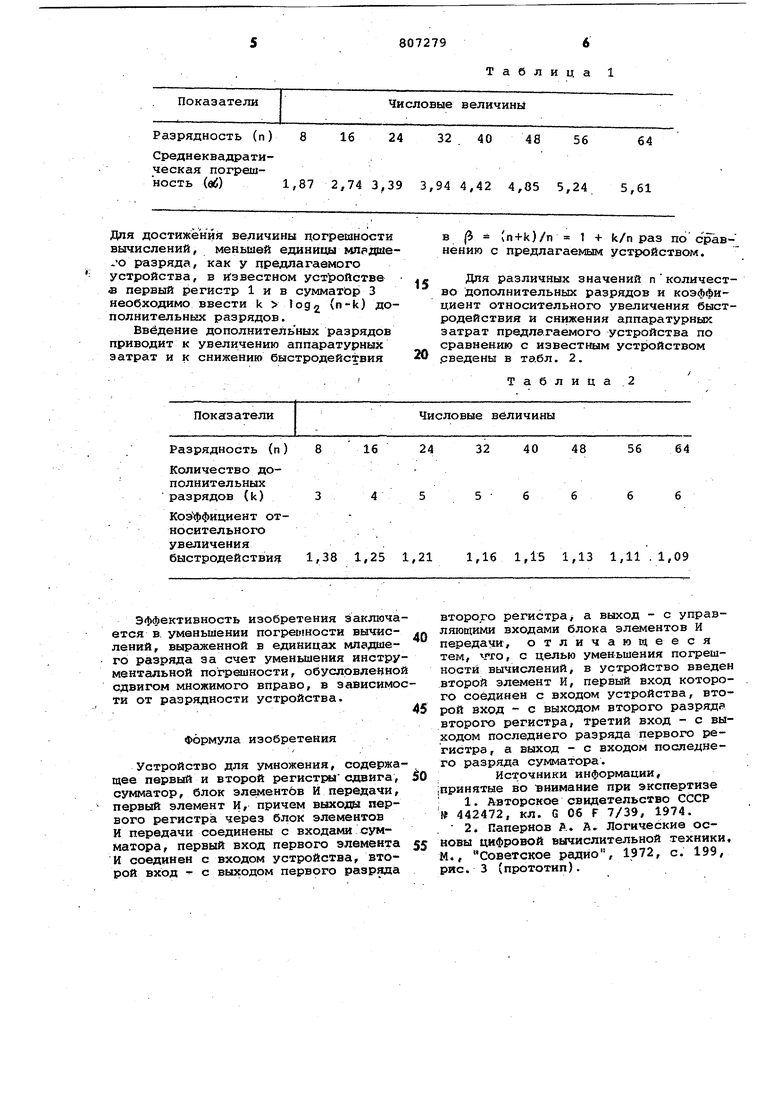

Для достижения величины цогрешности вычислений, меньшей единицы млрдше-о разряда, как у предлагаемого устройства, в Известном уст)ойстве а первый регистр 1 и в сумматЬр 3 необходимо ввести k logg (n-k) дополнительных разрядов.

Введение дополнительных разрядов приводит к увеличению аппаратурных затрат и к снижению быстродействия

81624

Эффективность изобретения заключается в уменьшении погретности вычис- дл лений, выраженной в единицах младшего разряда за счет уменьшения инструментальной погреиности, обусловленной сдвигом множимого вправо, в зависимости от разрядности устройства.

Формула изобретения

Устройство для умножения, содержа щее первый и второй регистЕ сдвига, сумматор, блок злеялентбв И передачи, первый элемент и, причем выходы первого регистра через блок элементов И передачи соединены с входами сумматора, первый вход первого элемента И соединен с входом устройства, второй вход - с выходом первого разряда

64

5,61

в |5 (n4-k)/n 1 + k/n раз посравнению с предлагаемым устройством.

Для различных значений пколичество дополнительных разрядов и коэффициент относительного увеличения быстродействия и снижения аппаратурных затрат предлагаемого устройства по сравнению с известным устройством .сведены в табл. 2.

Таблица2

32 40 48 56 64

5 6

1,16 1,15 1,13 1,11 . 1,09

второго регистра а выход - с управляющими входами блока элементов И пед едачи, отличающееся тем, , с целью уменьшения погрешности вычислений, в устройство введен второй элемент И, первый вход которого соединен с входом устройства, вто45рой вход - с выходом второго разряда второго регистра, третий вход - с выходом последнего разряда первого регистра, а выход - с входом последнего разряда сумматора.

Источники информации, ;принятые во внимание при экспертизе 1. Авторское свидетельство СССР 442472, КЛ. G Об F 7/39, 1974. . 2. Папернов А. А. Логические основы цифровой вычислительной техники, М., Советское радио, 1972, с. 199, рис. 3 (прототип).

Авторы

Даты

1981-02-23—Публикация

1978-11-20—Подача