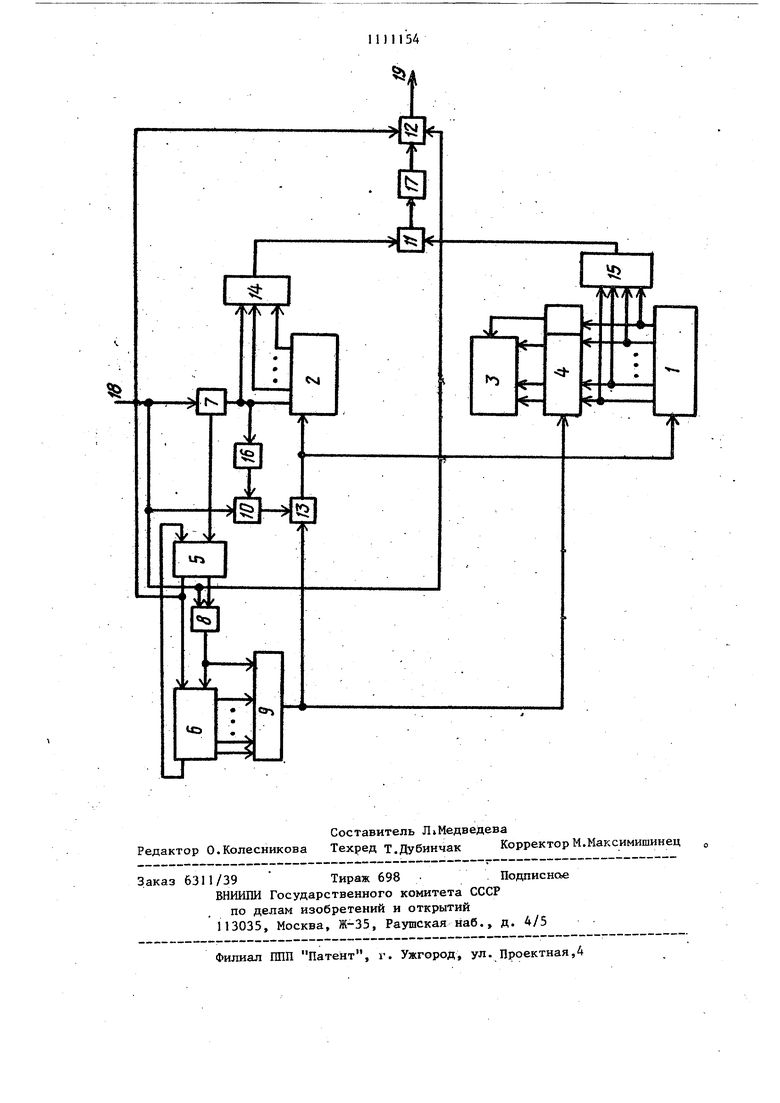

Изобретение относится к области цифровой вычислительной техники, в частности к устройствам для умножения, и может быть использовано в цифровых вычислительных машинах. Известно устройство для умножения, содержащее первый и второй регистры сдвига, вентили передачи, первый элемент И С1Л« Данное устройство довольно прост однако для достижения величины погрешности вычислений меньшей един цы младшего разряда устройство содержит дополнительные разряды перво го регистра и сумматора, что приводит к увеличений аппаратурных затрат и уменьшению быстродействия. Наиболее близким к данному является устройство для умножения, соде жащее первый и второй регистры сдви га, сумматор, блок элементов И передачи, первый элемент И, второй элемент И, причем выходы первого регистра через блок элементов И передачи соединены с входами суммат ра, первый вход первого элемента И соединен с входом устройства, второ вход - с выходом первого разряда вт рого регистра, а выход - с управляю щими входами блока элементов И пере дачи, первый вход второго элемента И соединен с входом устройства, вто рой вход - с выходом BTOjporo разряд второго регистра, третий вход - с выходом последнего разряда первого регистра, а выход - с входом послед него разряда сумматора С2. Недостатком известного устройств является низкое быстродействие. Цель изобретения. - повышение быстродействия. Поставленная цель достигается тем, что в устройство, содержащее первый регистр сдвига, второй регистр сдвига, сумматор, группу элементов И, два элемента И, причем первый вход первого элемента И соединен с тактовым входом устройст и первым входом второго элемента И, выходы И старших разрядов первого регистра сдвига соединены с информационными входами соответствующих элементов И группы (и - разрядность операндов у, выходы которьпс соединен с соответствующими входами сумматор выход старшего разряда второго регистра сдвига соединен с вторым входом первого элемента И, введены три элемента ИЛИ, триггер, третий, четвертьй пятый и шестой элементы И 4 счетчик, два элемента НЕ, причем вы- ходы разрядов рервого регистра сдвига соединены соответственно с входами первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, выход которого соединен через первый элемент НЕ с первым входом четвертого элемента И, выход которого соединен с выходом устройства, второй вход третьего элемента И соединен с выходом второго элемента ИЛИ, входы которого соединены соответственно с выходами рззрядоэ второго регистра сдвига, выход старшего разряда которого через второй элемент НЕ соединен с первым входом пятого элемента И, второй вход которого соединен с тактовым входом устройства и вторым входом четвертого элемента И, третий вход соединен с инверсным выходом триггера и входом сброса счетчика, счетный вход которого соединен с выходом второго элемента И и первьп-1 входом шестого элемента И, остальные входы которого соединены соответственно с выходами счетчика, выход переполнения которого соединен с входом сброса триггера, информационный вход которого соединен с выходом первого элемента И, прямой выход триггера соединен с вторым входом второго элемента И, выход щестого элемента И соединен с первым входом третьего элемента РиШ и управляющими входами элеь1ентов И группы, второй вход третьего элемента ИЛИ соединен с выходом пятого элемента И, выход третьего элемента ИЛИ соединен с входами сдвига первого и второго регистров сдвига, выход младшего ( +П-го разряда первого регистра сдвига соединен с информационным входом соответствующего элемента И группы, выход которого подключен к соответствующему входу сумматора. На чертеже представлена блок-схема устройства для умножения. Устройство содержит первый 1 и торой 2 регистры сдвига, сумматор3., группу элементов И 4, триггер 5, четчик 6, элементы И 7 - 12, элемены ИЛИ 13 - 15, элементы НЕ 16,17, актовый вход 18 и выход 19 устроййта. Устройство работает следующим бразом. Исходные данные для умножения ножимое без младшего разряда 31 и множитель вводятся в первый и второй регистры 1 и 2 соответственно триггер 5 и счетчик 6 установлены Б нулевом состоянии. При поступлении тактового сигнала на вход J 8 устройства множимое, перв начешьно равное А, сдвигается на один разряд вправо в первом регистре а множитель первоначально равный В, сдвигается на один разряд влево во втором регистре 2. Так кик в первый регистр 1 введено множимое без младшего разряда, то значение дополнительного разряда первого регистра I после первого сдвига равно, нулю.Начи ная со второго такта сдвига в этом разряде последовательно находятся с предпоследней по первую цифры множимого , соответствующие с второй по ft,- -ю цифрам множителя.Передача произведения цифры множителя,взятой с первого разряда второго регистра 2,и цифры .множимого,взятой с последнего допол.нительного разряда первого регистра I , в последний разряд сумматора 3 производится через группу элементов И 4 только при передачах сдвинутого множимого в сумматоре 3. Под воздействием тактового сигнала на входе 18 устройства частоты ) определяемой частотой сдвига первого и второго регистров 1,2,анализируется очередняя цифра множителя с первого выхода второго регистра 2. Если эта цифра равна единице, то на выходе элемента И 7 формируется сигнал, устанавливающий по переднему фронту триггер 5 в единичное состояние. При этом на выходе элемента И 8 формируется сигнал, поступающий на счетный вход счетчика 6, коэффициент пересчета которого определяется длительностью такта суммирования и на один из входов элемента И 9, на остальных входах элемента И 9 присутствуют сигналы 1 ,. и на его выходе формируется сигнал начала такта суммирования, который через группу элементов И 4 вводит информацию первого регистра 1 в сумматор 3 а по заданному фронту через элемент ИЛИ I3 осуществляет сдвиг информации первого и второго регистров 1,2 Таким образом, после окончания действия сигнала с выхода элемента И 9 и прихода очередноготактового сигнала с входа 18 имеется возможность анализа следующих цифр множителя. 44 Если одна или несколько следующих цифр множителя равны нулю, то с помощью элемента НЕ 16 и элемента И 10 формируются сигналы, которые через элемент ИЛИ 13 сдвигают информацию первого и второго регистров 1,2. Если в момент выполнения такта суммирования анализируемая цифра множителя равна единице, то последующее формирование сигналов сдвига не проходит и осуществляется ожидание окончания такта суммирования. Конец такта суммирования определяет сигнал переполнения счетчика 6, переключающегося по заднему фронту сигналов элемента И 8. После окончания действия сигнала переполнения триггер 5, а следовательно, и счетчик 6 переходят в нулевое состояние. Последующий приход тактового сигнала с входа 18 в зави-г симости от анализируемого разряда множителя определит такт суммирования либо такт сдвига. Операция умножения может считаться законченной, если не выполняется такт суммирования и состояния первого или второго регистров 1,2 равны нулю. Сигнал окончания умножения формируется на выхо5;е элемента И J 2 под действием тактового сигнала входа 18, когда триггер 5 установлен в нулевом состоянии, с помощью элементов ИЛИ 14 и 15,являющихся схемами совпадения для низких уровней сигнала, элемента И 11, выполняющего функцию сборки сигналов низких уровней, и элемента НЕ 17, на выходе которого формируется сигнал, когда значения.сдвинутого множимого или множителя в первом или втором регистрах 1,2 равны нулю. По сигналу выхода 19 устройства можно осуществлять ввод последующих чисел множителя и.множимого в соответствующие регистры 1,2. Таким образом, время умножения в данном устройстве красно периоду TC такто,вых сигналов входа 18 и . зависит не только от множителя, но и от множимого. Если считать появление нулей и единиц в разрядах множителя и множимого равновероятным и учитывать анализ состояний регистров множителя и множимого, то среднее время умножения в данном устройстве более чем в 2,4 раз.а меньше прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для умножения в избыточной системе счисления | 1983 |

|

SU1124286A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для умножения | 1979 |

|

SU842799A1 |

| Устройство для умножения двоичныхчиСЕл B дОпОлНиТЕльНыХ КОдАХ | 1979 |

|

SU813420A1 |

| Устройство для умножения двоичных чисел в дополнительных кодах | 1983 |

|

SU1119008A1 |

| Устройство для умножения целых чисел в р-кодах Фибоначчи | 1986 |

|

SU1345190A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

УСТРОЙСТВО ДЛЯ УШЮЖЕНИЯ, содержание первый регистр сдвига,второй регистр сдвига, сумматор, группу элементов И, два элемента И, причем первый вход первого элемента И соединен с тактовьш входом устройства и первым входом второго элемента И, выходы пстарших разрядов первого регистра сдвига соединены с информационными входами соответствующих элементов И группы ;п -разрядность операндов, выходы которых соединены с соответствующими входами сумматора, выход старшего разряда второго регистра сдвига соединен с вторым входом первого элемента И,отличающееся тем, что, с целью повышения быстродействия, в него введены три элемента ИЛИ, триггер, третий, четвертый, пятый и шестой элементы И, счетчик, два элемента НЕ, причем выходы разрядов первого регистра сдвига соединены соответственно с входам.и первого элемента ИЛИ, выход которого соединен с первым входом третьего элемента И, выход которого соединен через первый элемент НЕ с первым входом четвертого элемента И, выход которого соединен с выходом устройства, второй вход третьего элемента И соединен с выходом второго элемента ИЛИ, входы которого соединены соответственно с выходами разрядов второго рег истра сдвига, выход старшего разряда которого через второй элемент НЕ соединен с первым входом пятого элемента И, второй вход которого соединен с тактовым входом устройства и вторым входом четвертого элемента И, третий вход которого соединен с инверсным выходом триггера и входом сброса счетчика, счетный вход которого соединен с выходом второго элемента И и-первым (О входом шестого элемента И, остальные входы которого соединены соответственно с выходами счетчика, выход переполнения которого соединен с входом сброса триггера. инЛоомячионный вход которого соединен с выхо, дом первого элемента И, прямой выход триггера соединен с вторым входом второго элемента И, выход шестого элемента И соединен с первым входом третьего элемента ИЛИ и упел равляющими входами элементов И груп4 пы, второй вход третьего элемента ИЛИ соединен с выходом пятого элемента И, выход третьего элемента ИЛИ соединен с входами- сдвига первого. :i второго регистров сдвига, выход младшего (п +И-го разряда первого регистра сдвига соединен с информационным входом соответствующего элемента И группы, выход которого подключен к соответствующему входу сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Папернов А.А | |||

| Логические основы цифровой вычислительной техники | |||

| М.,Сов.радио, 1972, с | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для умножения | 1978 |

|

SU807279A1 |

Авторы

Даты

1984-08-30—Публикация

1983-02-04—Подача